ENGR 338 Lab 9 - Design a simple 8-bit ALU

Name: Max Krauss

Email: mtkrauss@fortlewis.edu

Objectives:

1. Be able to build an 8-bit ALU in ElectricVLSI.

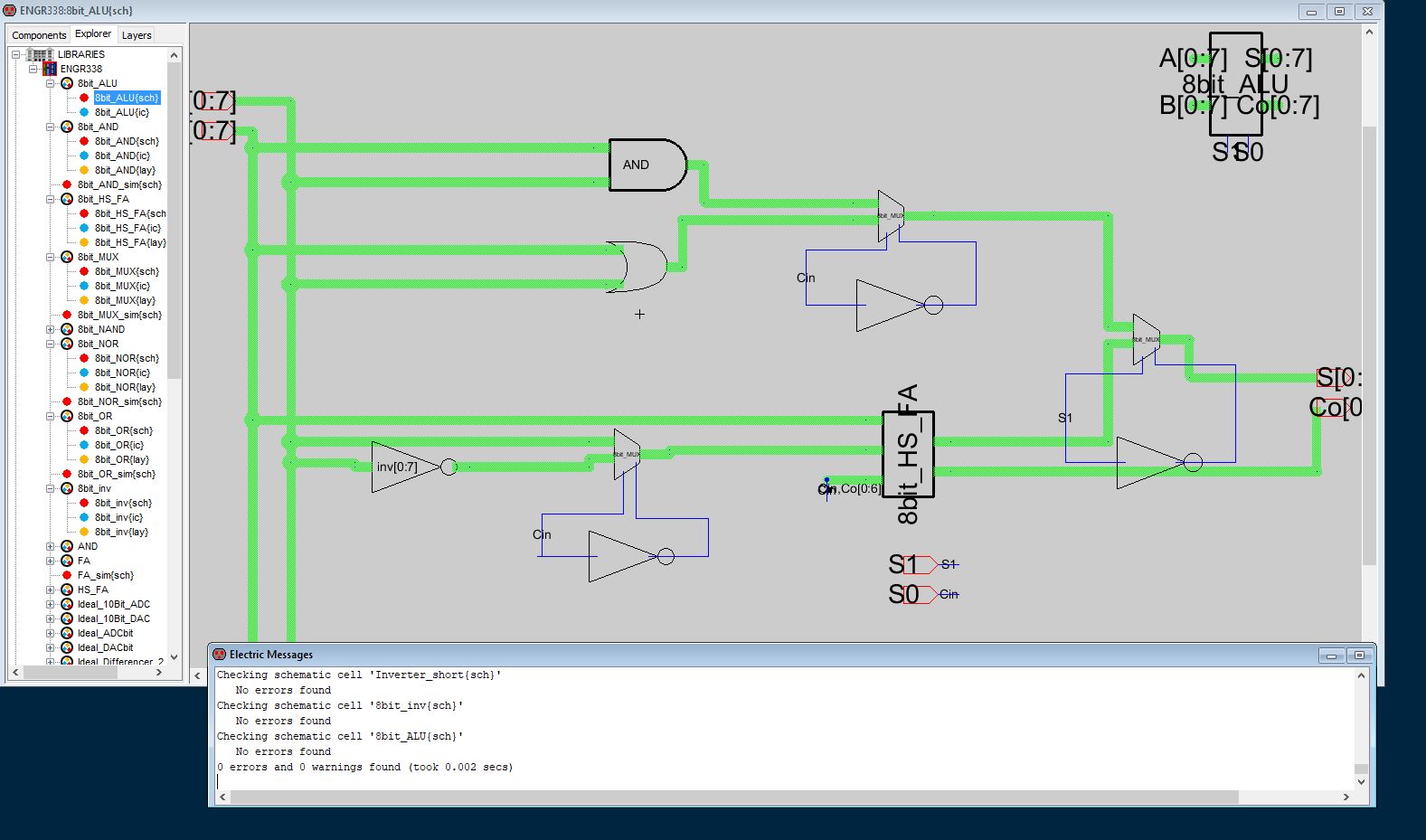

Task 1: Design the logic circuit of the ALU. (40 points)

Figure 1: 8-bit ALU schematic in Electric VLSI.

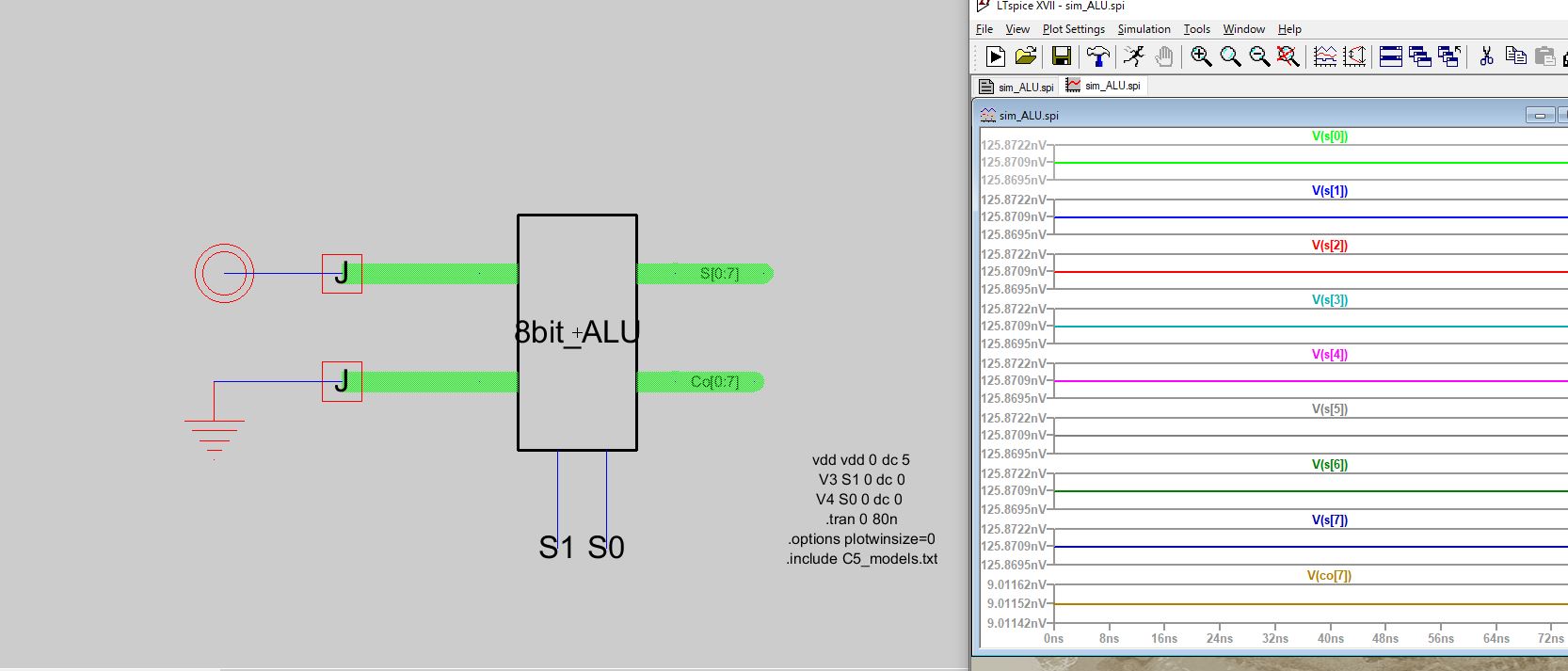

First, verify the AND gate by setting S1S0 = 00:

Figure 2: AND gate verification simulation for the 8-bit ALU.

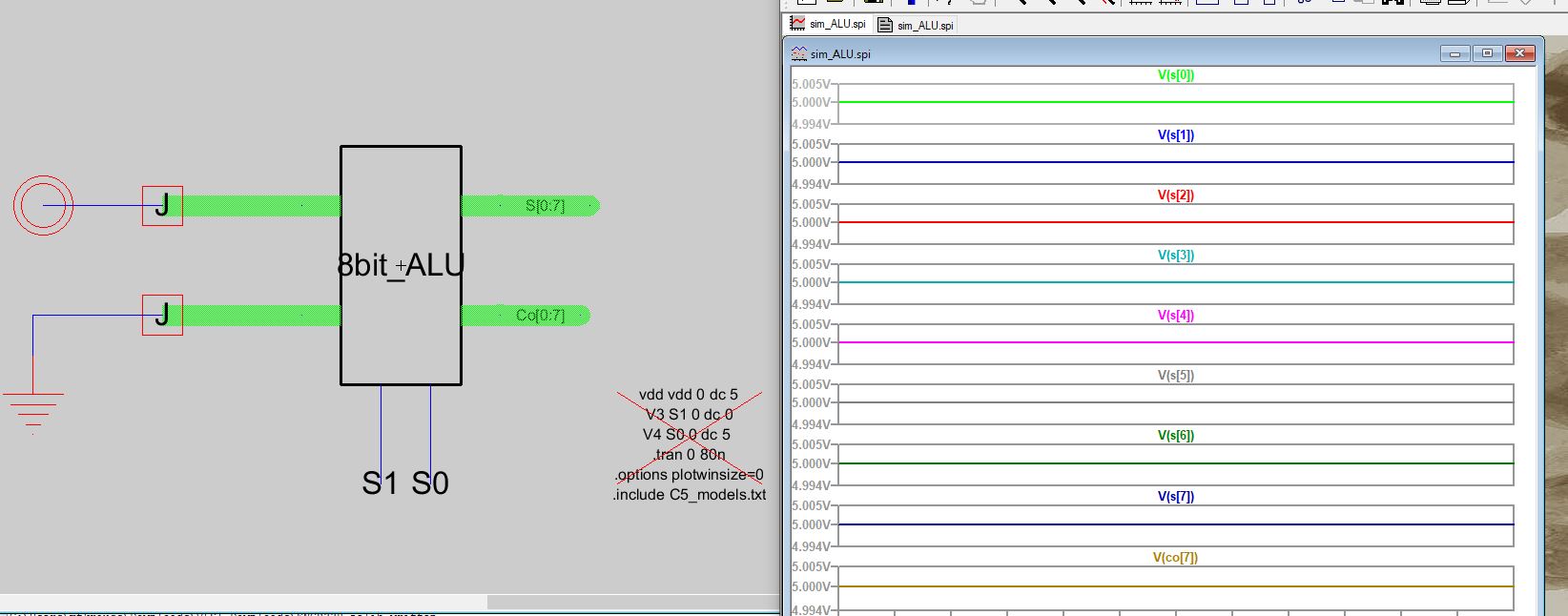

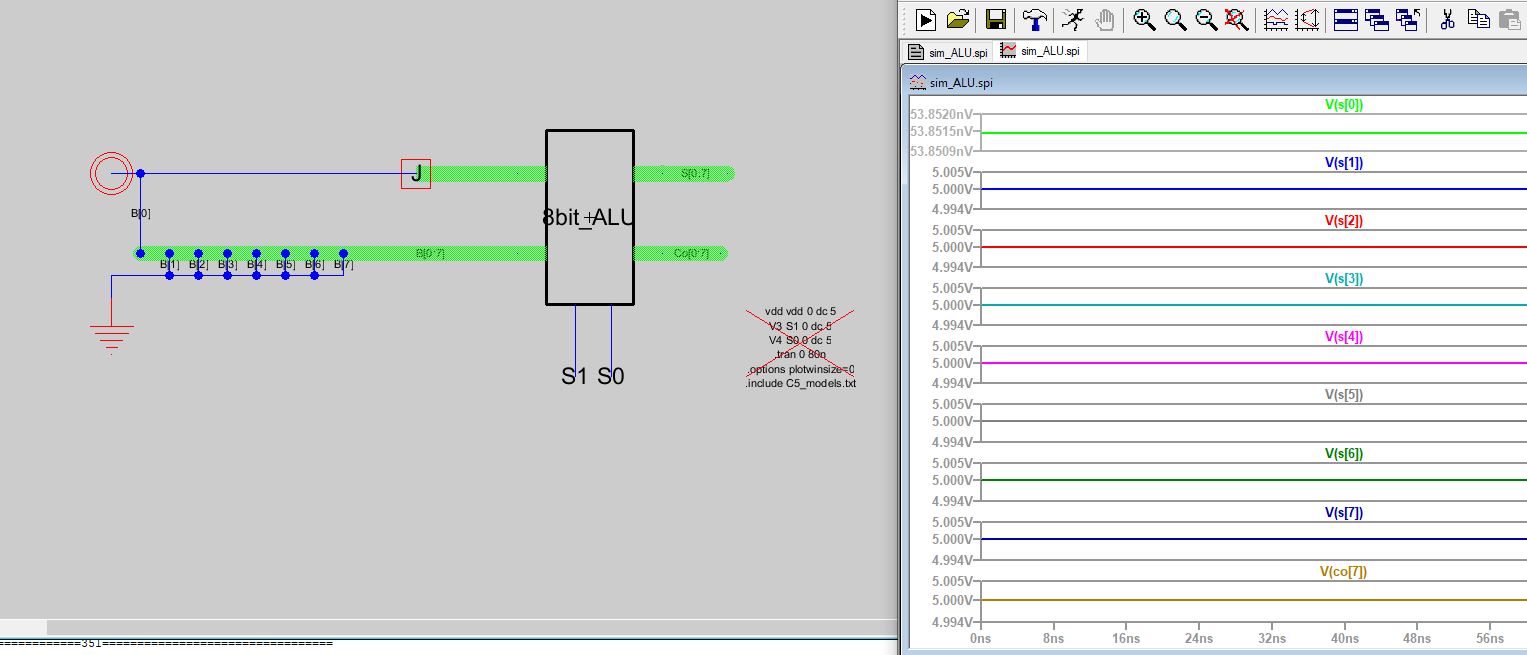

Second, verify the OR gate by setting S1S0 = 01:

Figure 3: OR gate verification simulation for the 8-bit ALU.

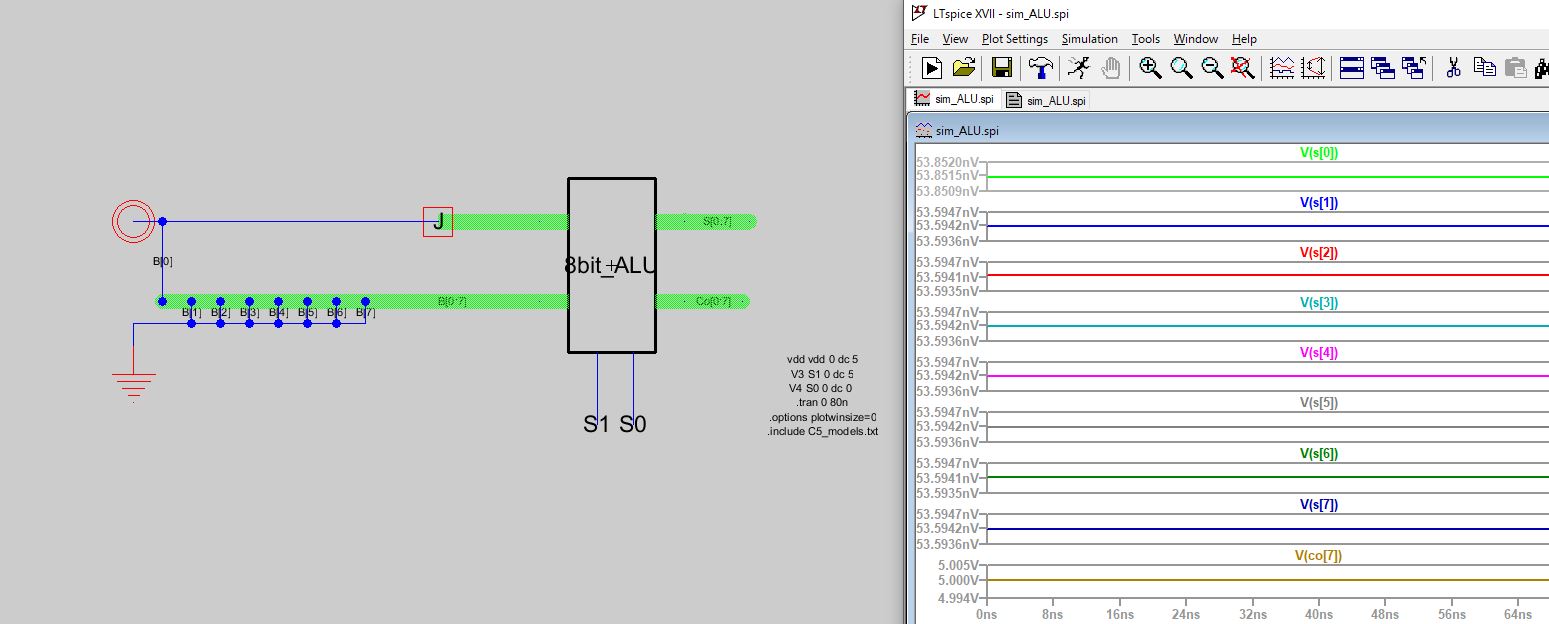

Next, verify the ADD operation. Use 1111 1111 + 0000 0001 = S = 0000 0000, Co = 1.

Figure 4: ADD operation verification simulation for the 8-bit ALU.

Next,

verify the subtraction operation. Use 1111 1111 - 0000 0001 = 1111 1111

+ (-0000 0001) = 1111 1111 + (1111 1110 + 1) = 1111 1111 + 1111 1111 =

1111 1110 (Co = 1).

Figure 5: Subtraction operation verification simulation for the 8-bit ALU.

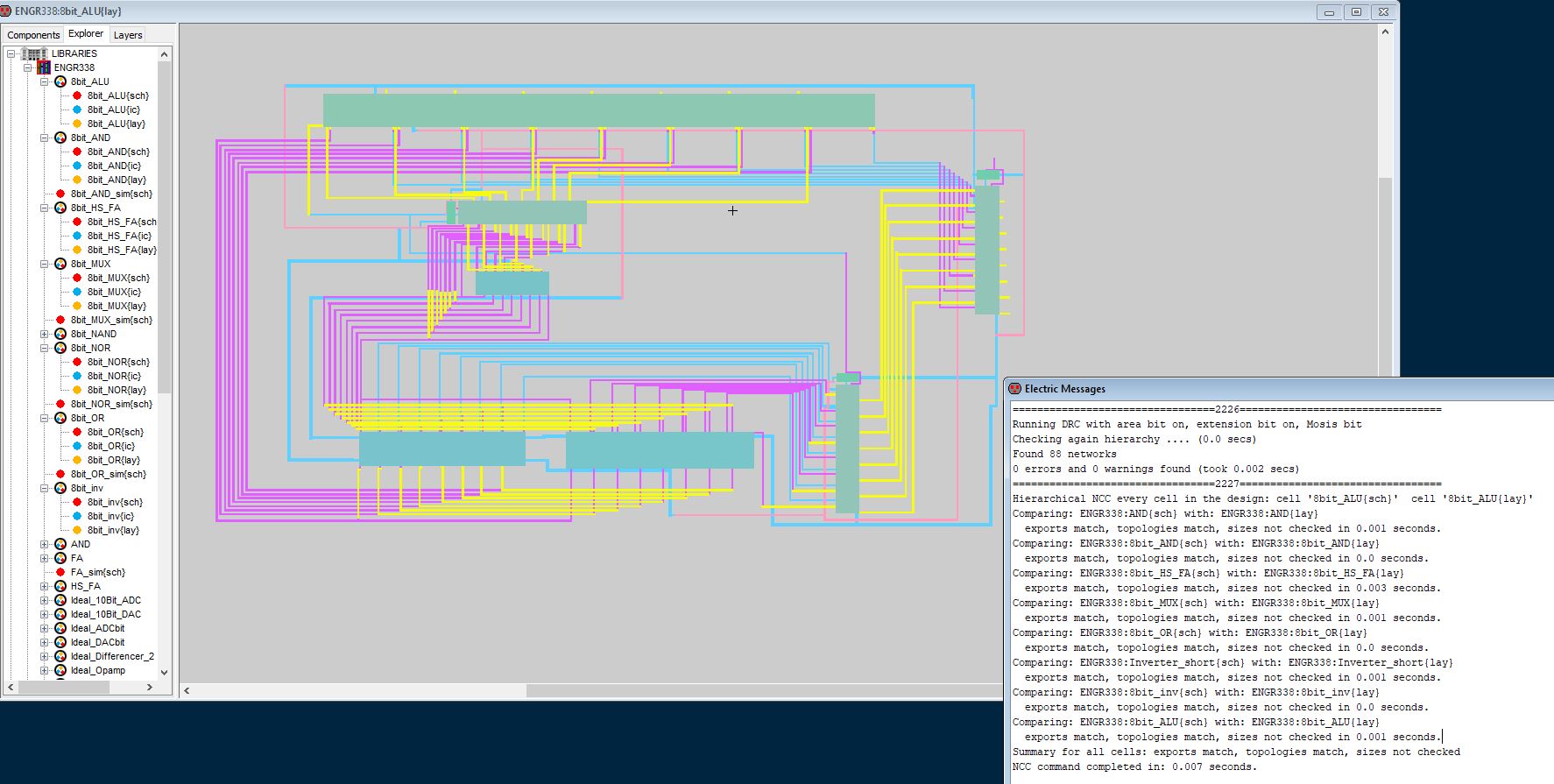

Task 2: Finish the layout of the ALU. (50 points)

Figure 6: ALU Layout passes DRC and NCC check.

Conclusion: Completing the ALU was a great challenge. Felt like we

finally got a real taste of VLSI, as this layout connected all of our

previous components into one. The actual layout took around 4 hours and

it was very satisfying once it passed NCC.