ENGR 338 Lab 8 Design a MUX, and a High-Speed Full Adder (2-week lab)

Name: Max Krauss

Email: mtkrauss@fortlewis.edu

Objectives:

1. Be able to build an 8-bit MUX in ElectricVLSI.

2. Be able to build an 8-bit high-speed FA in ElectricVLSI.

Task 1: Build an 8-bit MUX. (20 points)

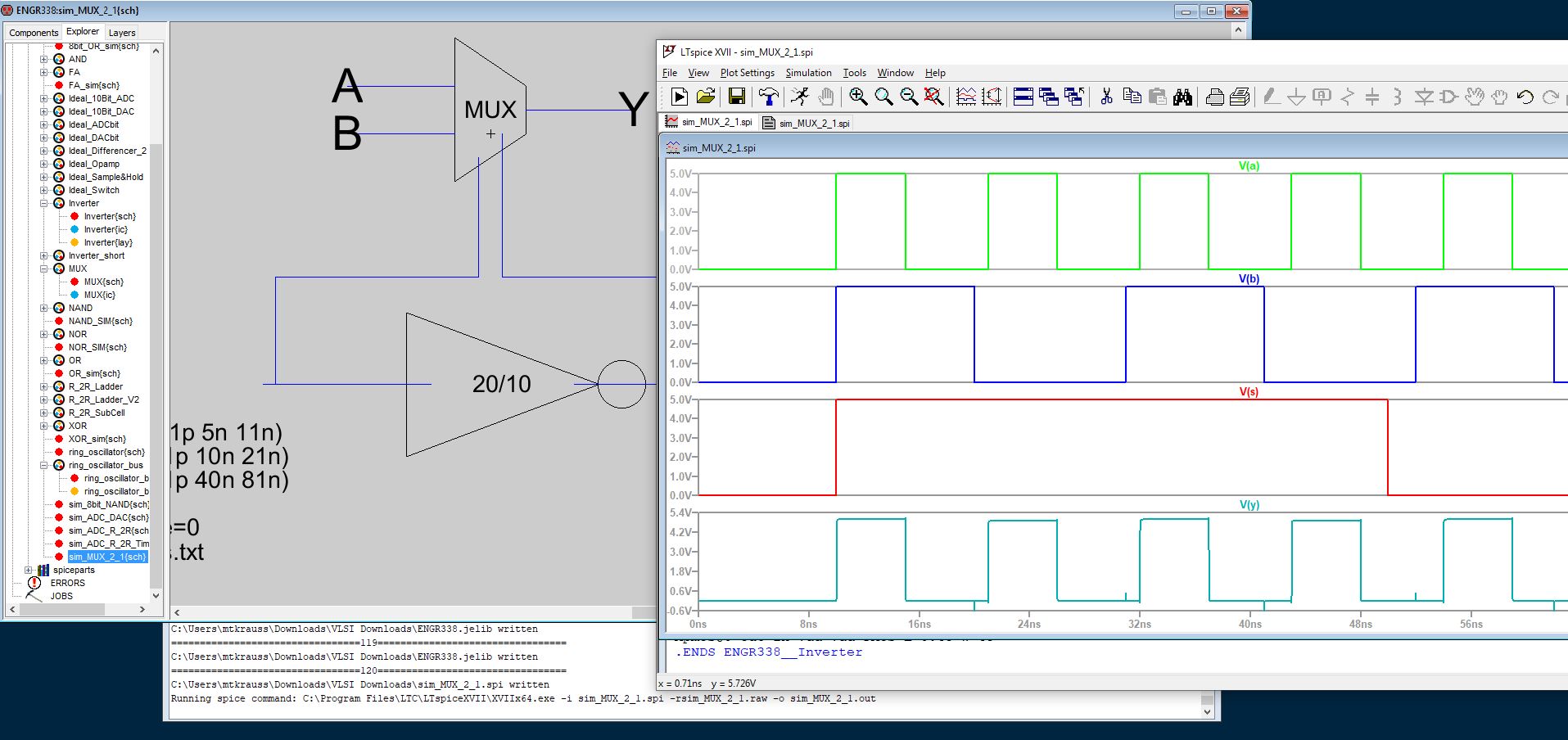

Figure 1: One bit MUX simulation.

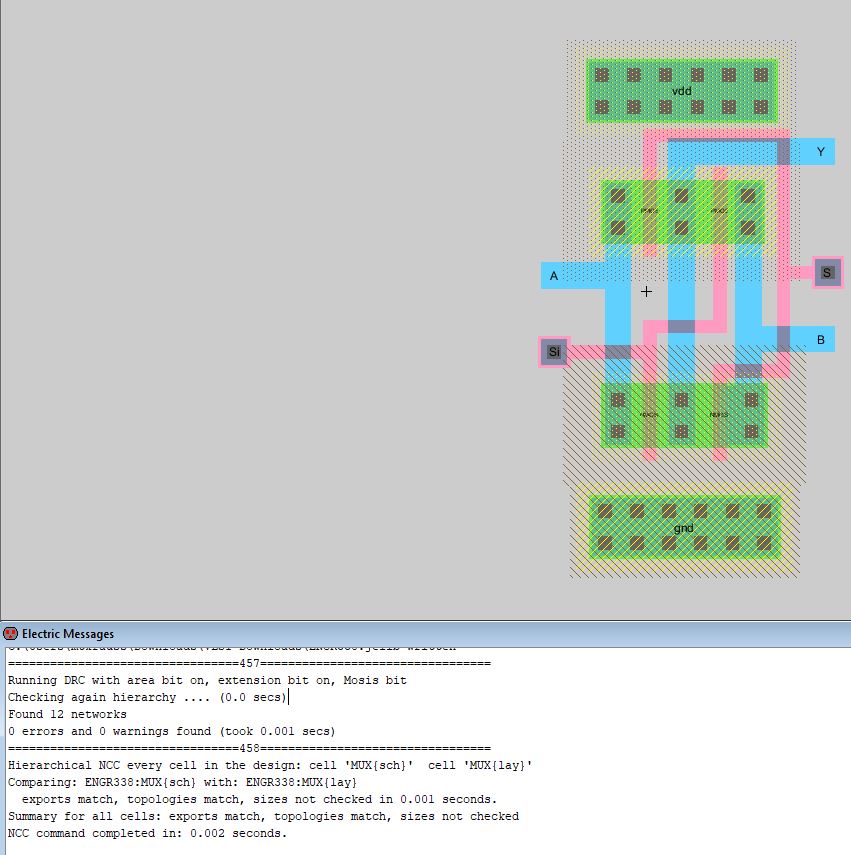

Figure 2: One bit MUX layout.

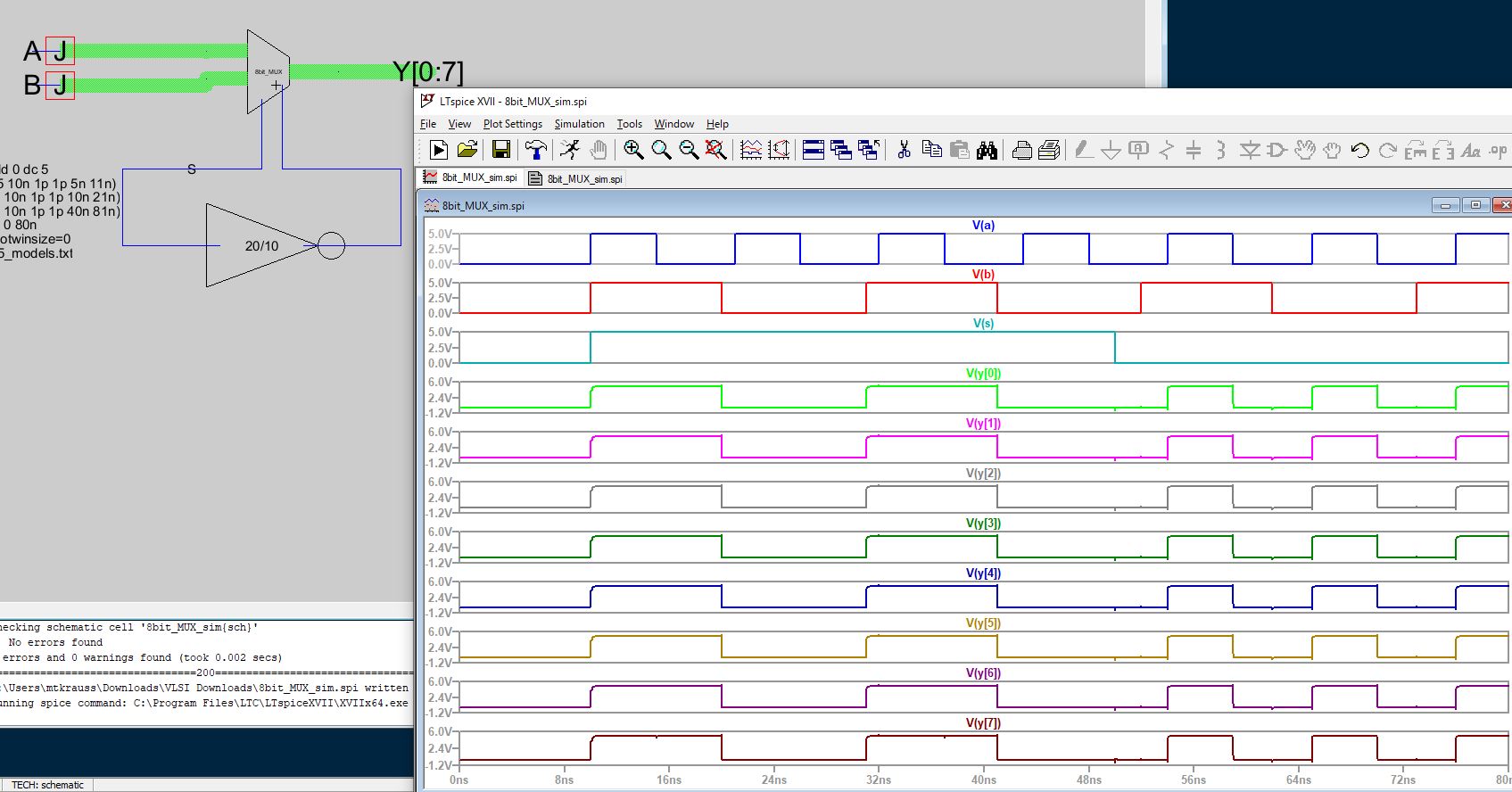

Figure 3: 8-bit MUX simulation.

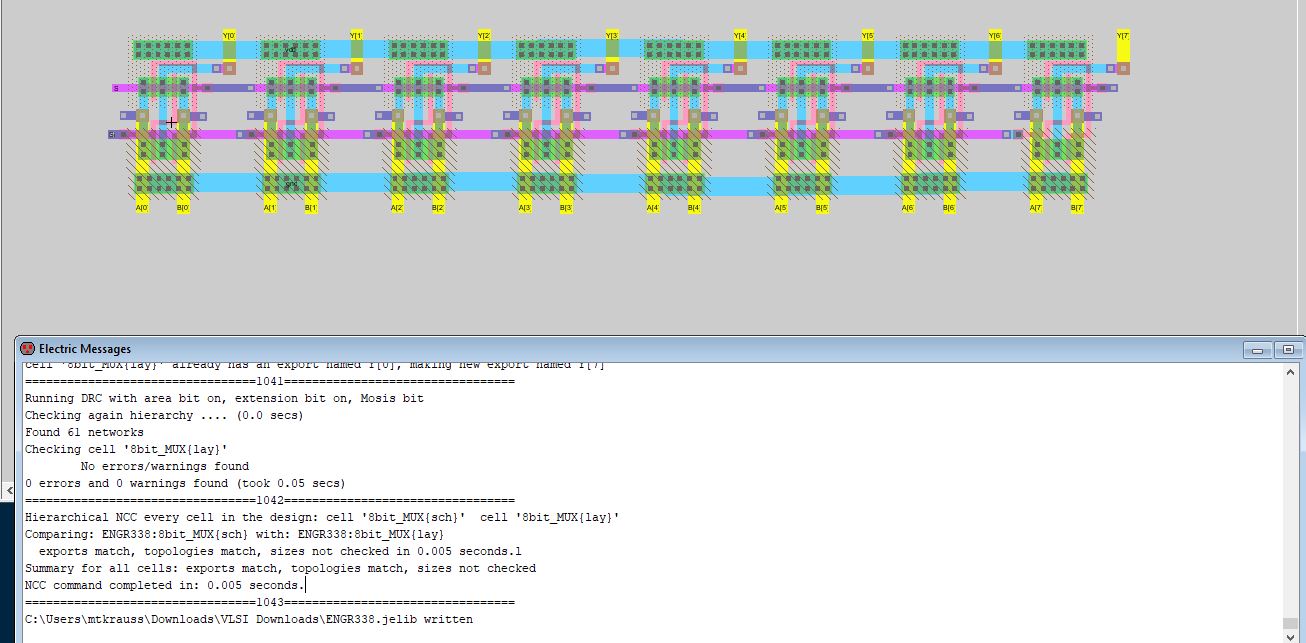

Figure 4: 8-bit MUX layout.

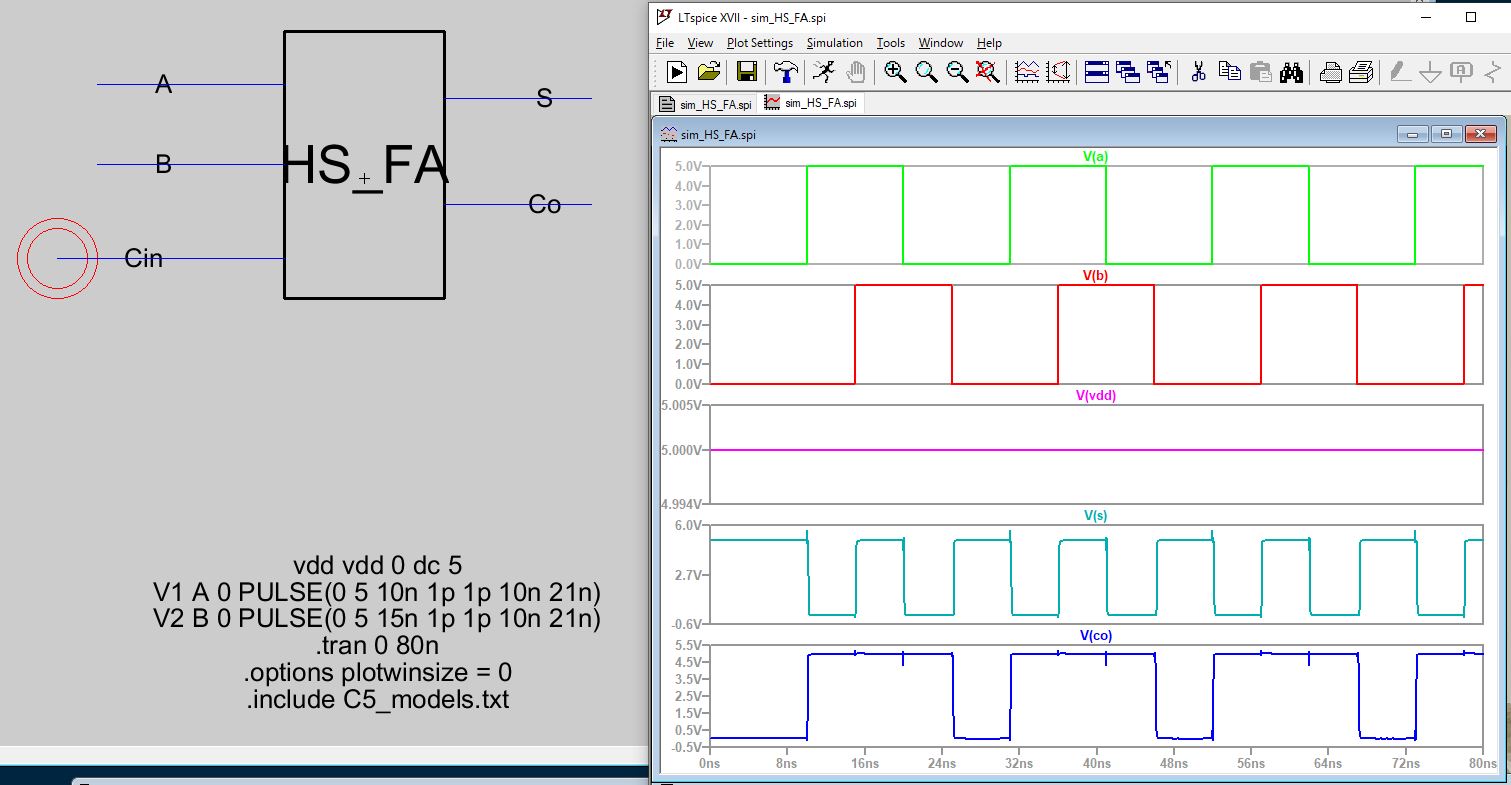

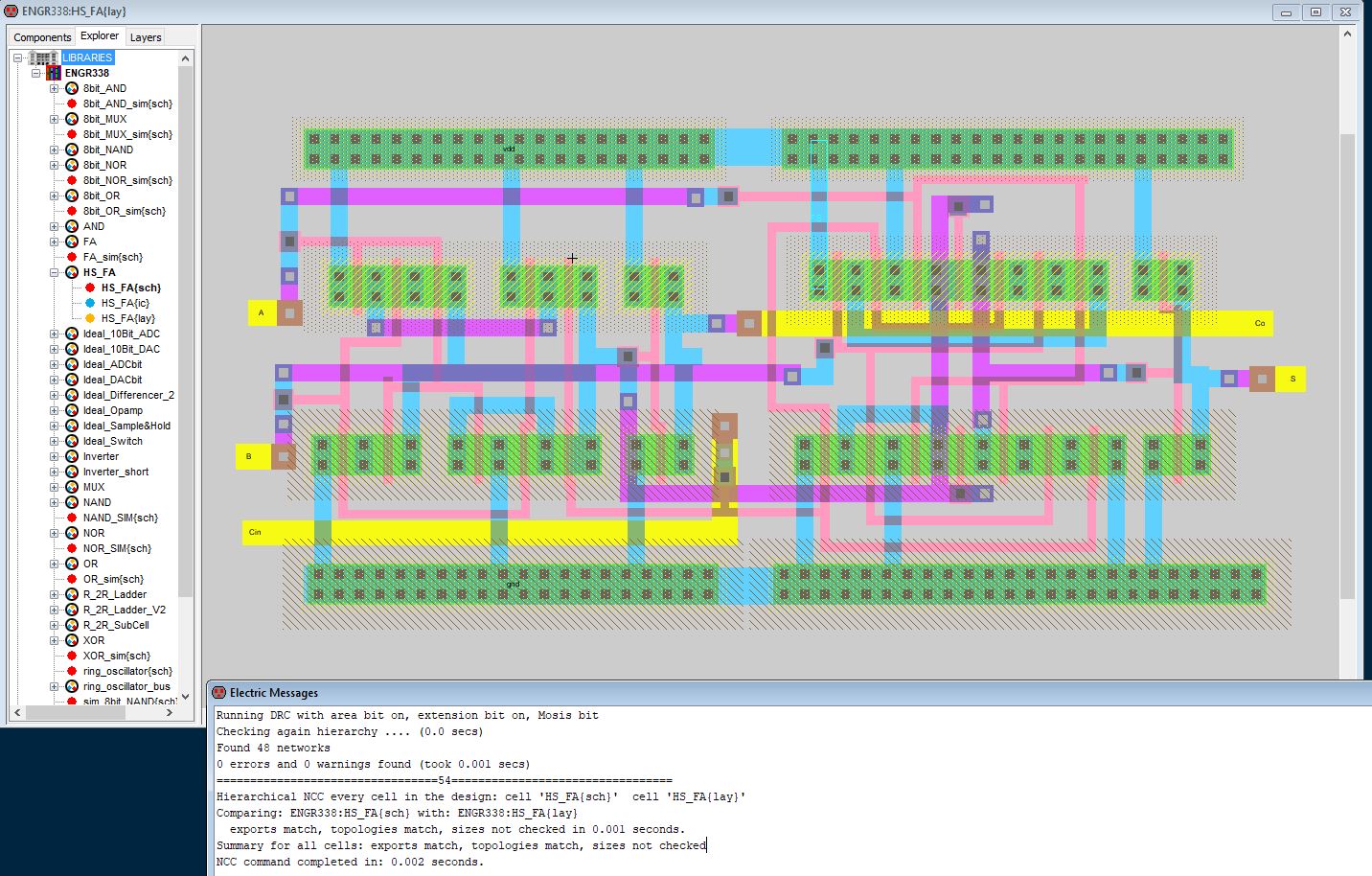

Task 2: Build a 1-bit high-speed full adder. (40 points)

Figure 5: High-speed full adder simulation.

Figure 6: High-speed full adder layout.

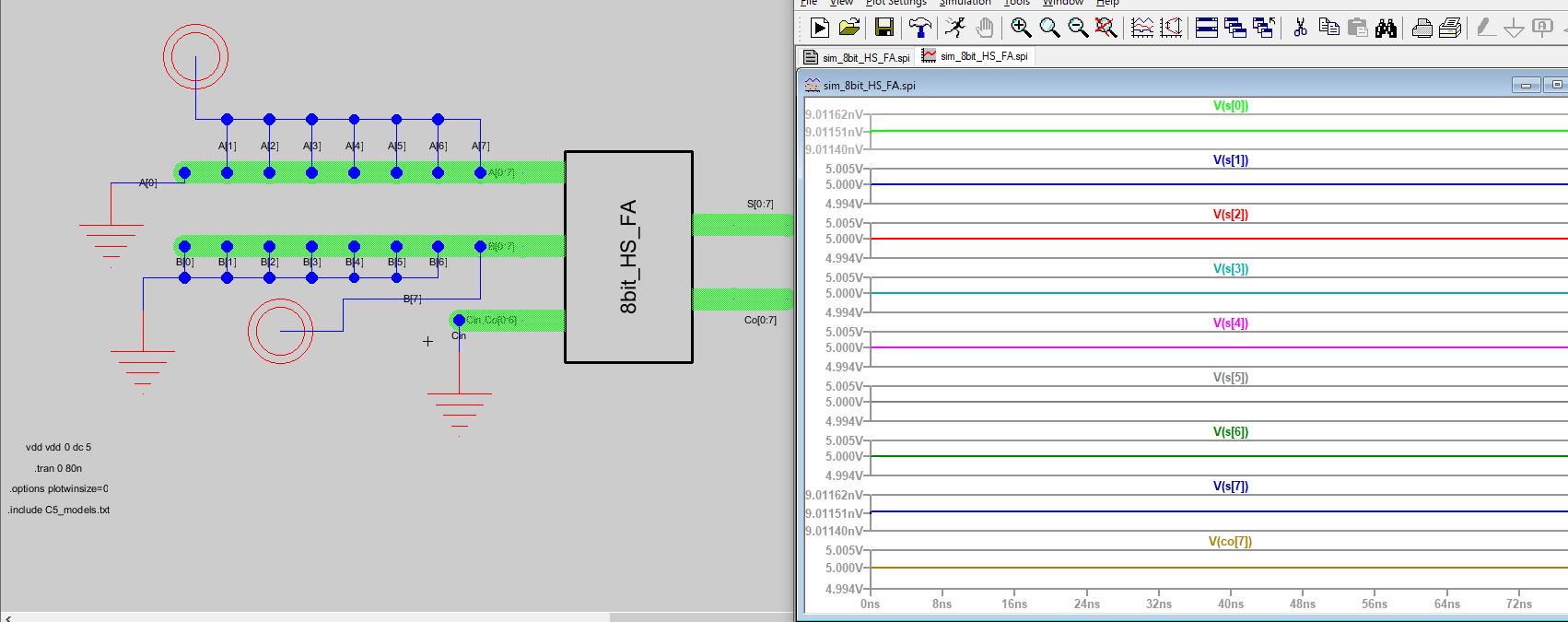

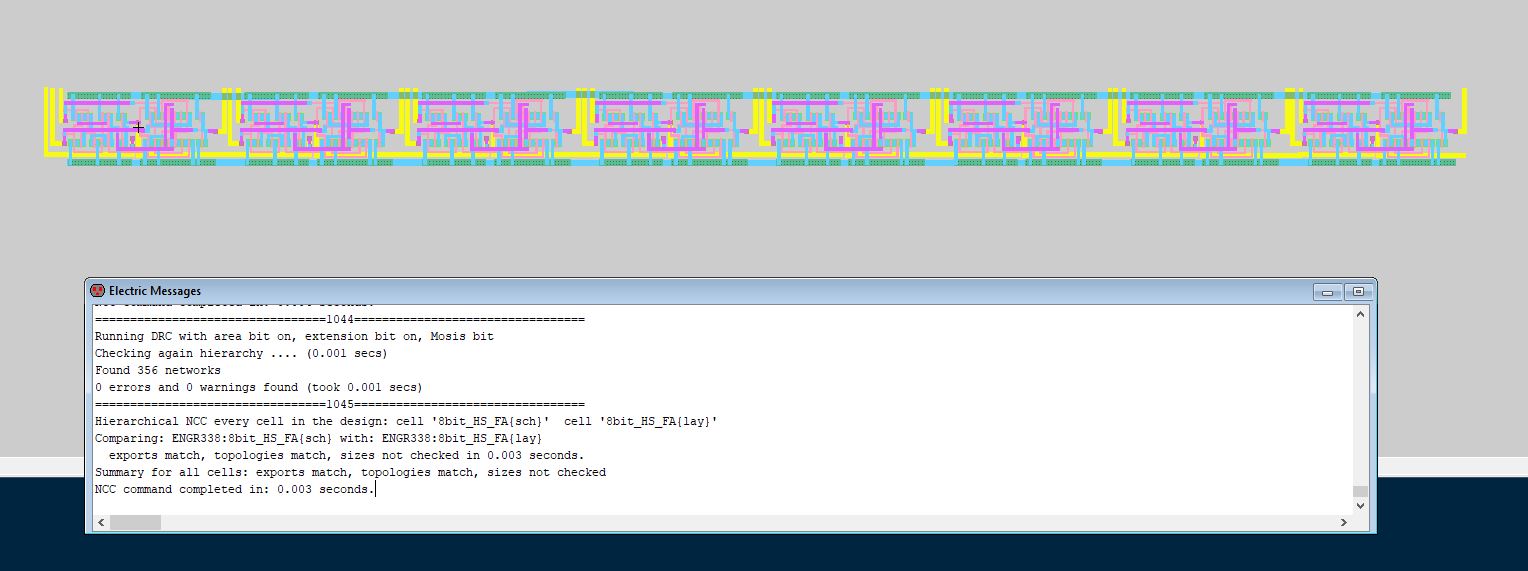

Task 3: Build an 8-bit high-speed full adder. (30 points)

Figure 7: 8-bit high speed full adder simulation.

Figure 8: 8-bit high speed full adder layout.

Conclusion: This lab was good

practice in layout design. The 8-bit implementations of these

components becomes much more complex. Makes me think of how complicated

the layouts for 64-bit components must be.