ENGR 338 - Lab 3

Name: Max Krauss

Email: mtkrauss@fortlewis.edu

Lab 3 - Layout the R-2R DAC

Objectives:

1. Layout the R-2R DAC in Electric VLSI using N-Well resistors.

2. Be familiar with Electric VLSI and LTSpice for integrated circuit design.

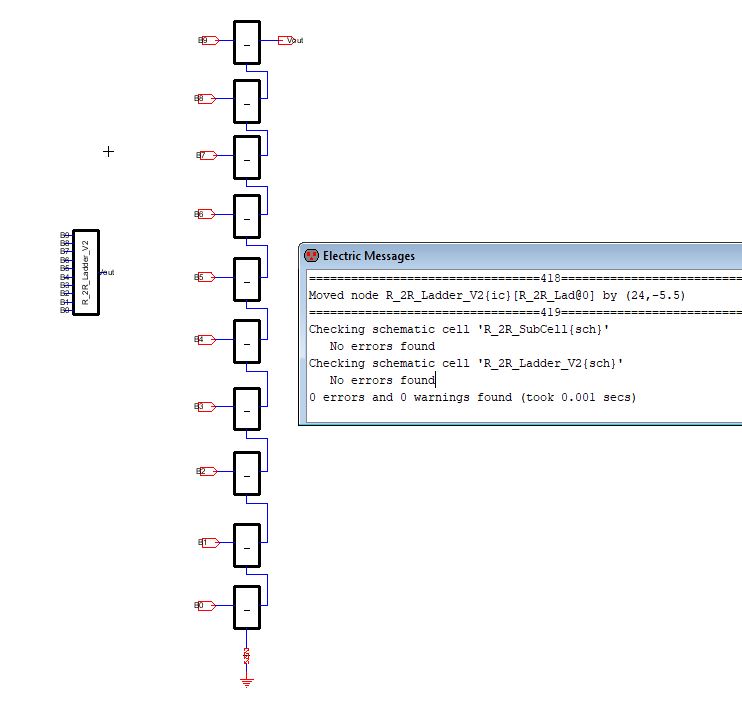

Task 1: Create the schematic of the subcells for the R-2R ladder. (40 points).

Figure 1: Schematic for the R-2R DAC made with subcells in Electric VLSI.

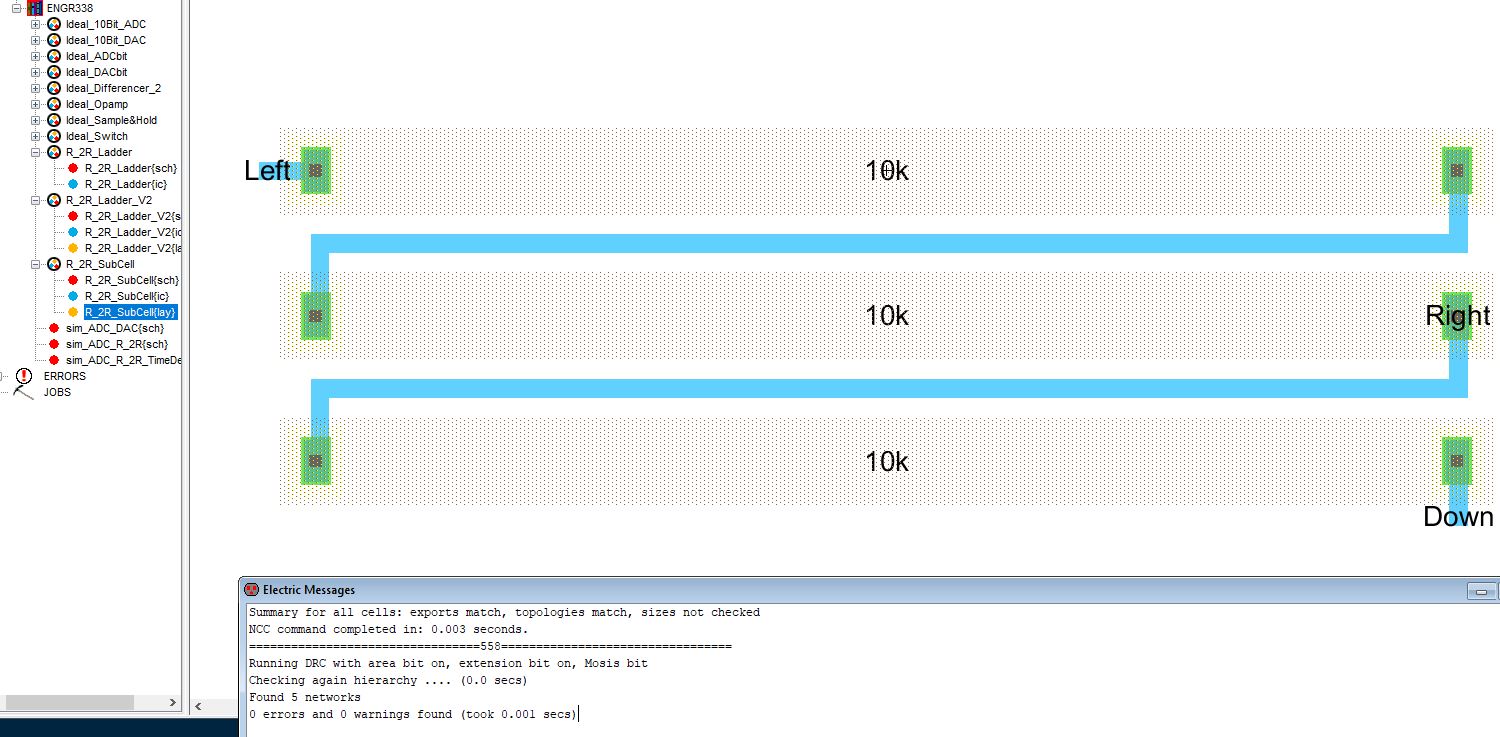

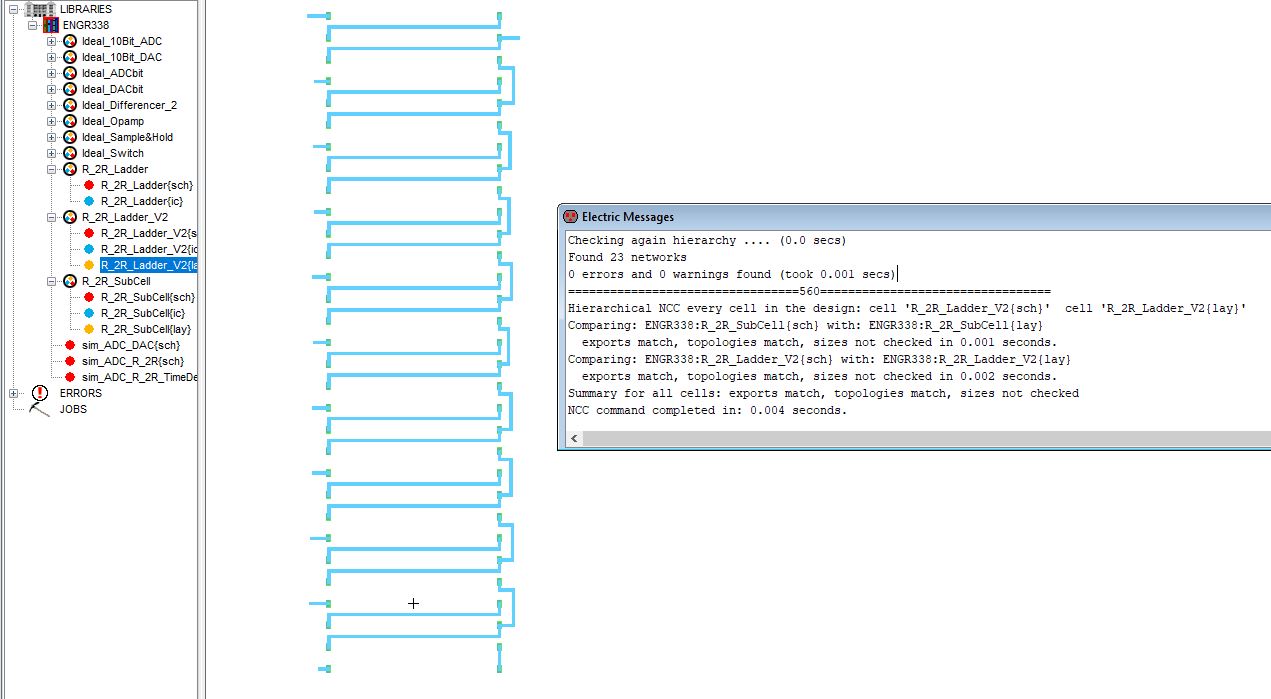

Task 2: Create the layout of the subcells for the R-2R ladder. (50 points).

Figure 2: Subcell layout for the R-2R DAC.

Figure 3: Layout for the R_2R DAC connecting the subcells together with a 10k resistor.

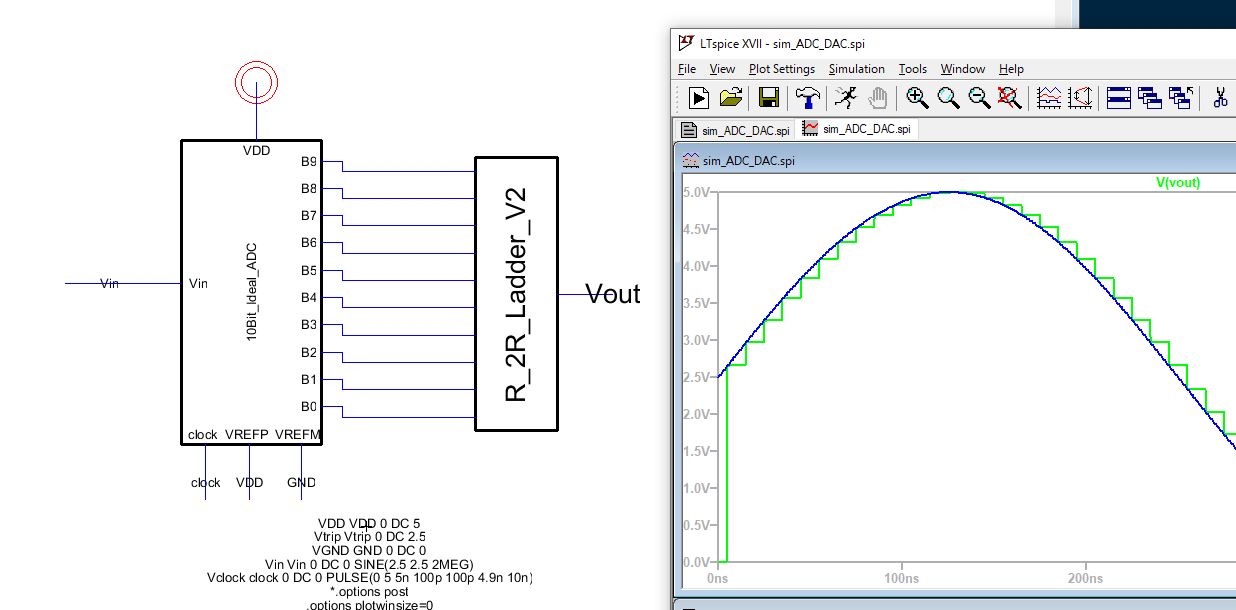

Figure 4: Ideal ADC connected to the R_2R Ladder DAC v2 with corresponding LTSpice simulation

Conclusion:

This lab helped demonstrate how to use subcells in Electric VLSI to

make larger layouts easier to construct. This lab was easier than the

last one as I am becoming more familiar with using Electric VLSI.