Electric VLSI software is very useful for modeling and simulating circuits. The software is easy to learn and has a large database of components to model with. The software checks for errors in the design and helps locate the errors for troubleshooting. The models easily export to LTSpice for simulation. Modeling and simulating circuits are both important steps in circuit design and make the design process efficient and straight forward.

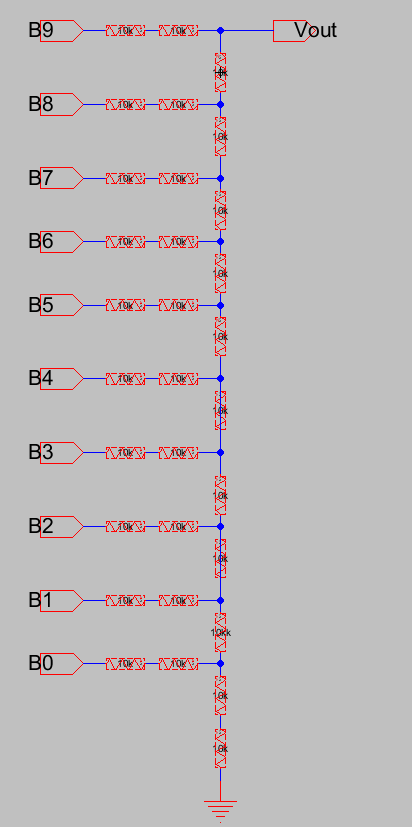

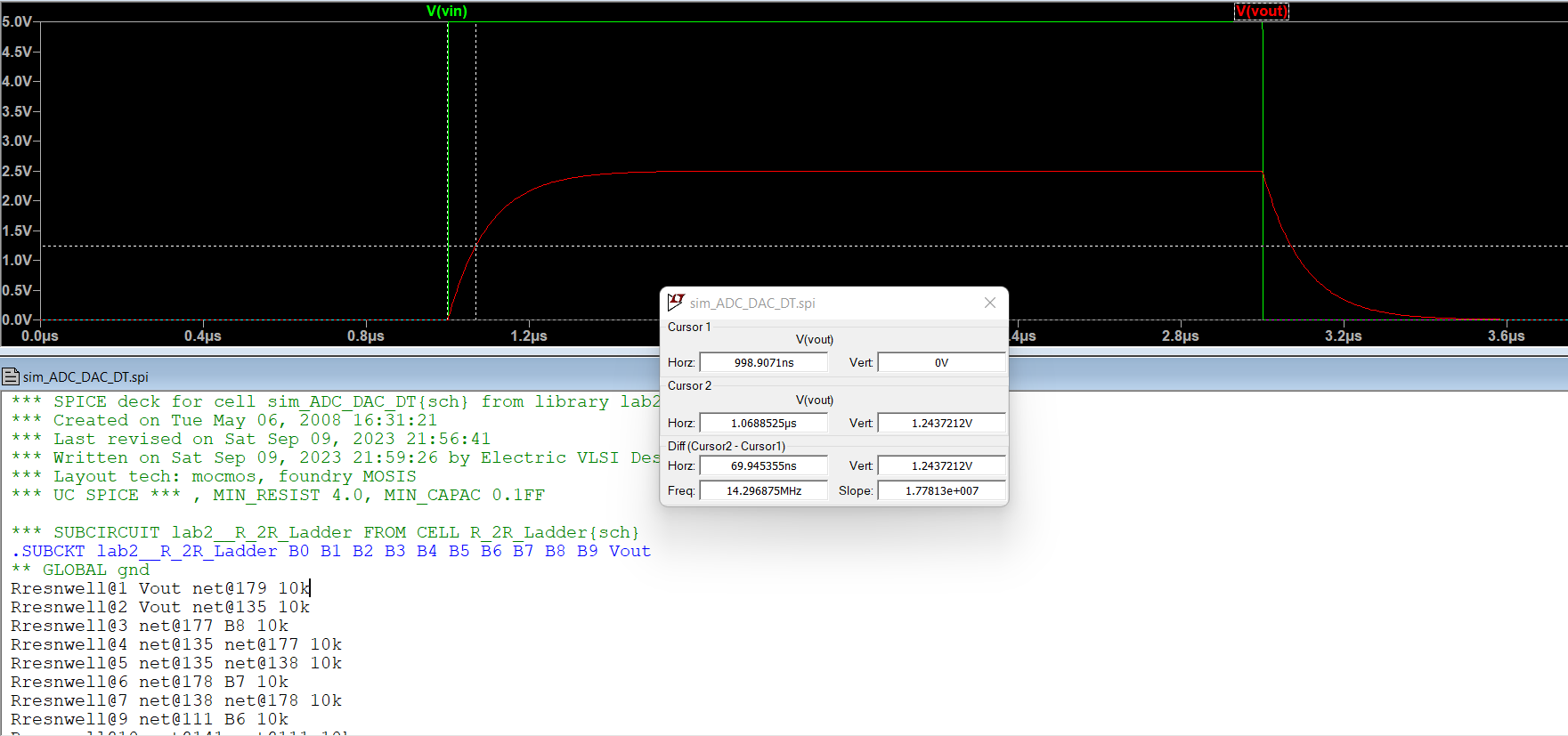

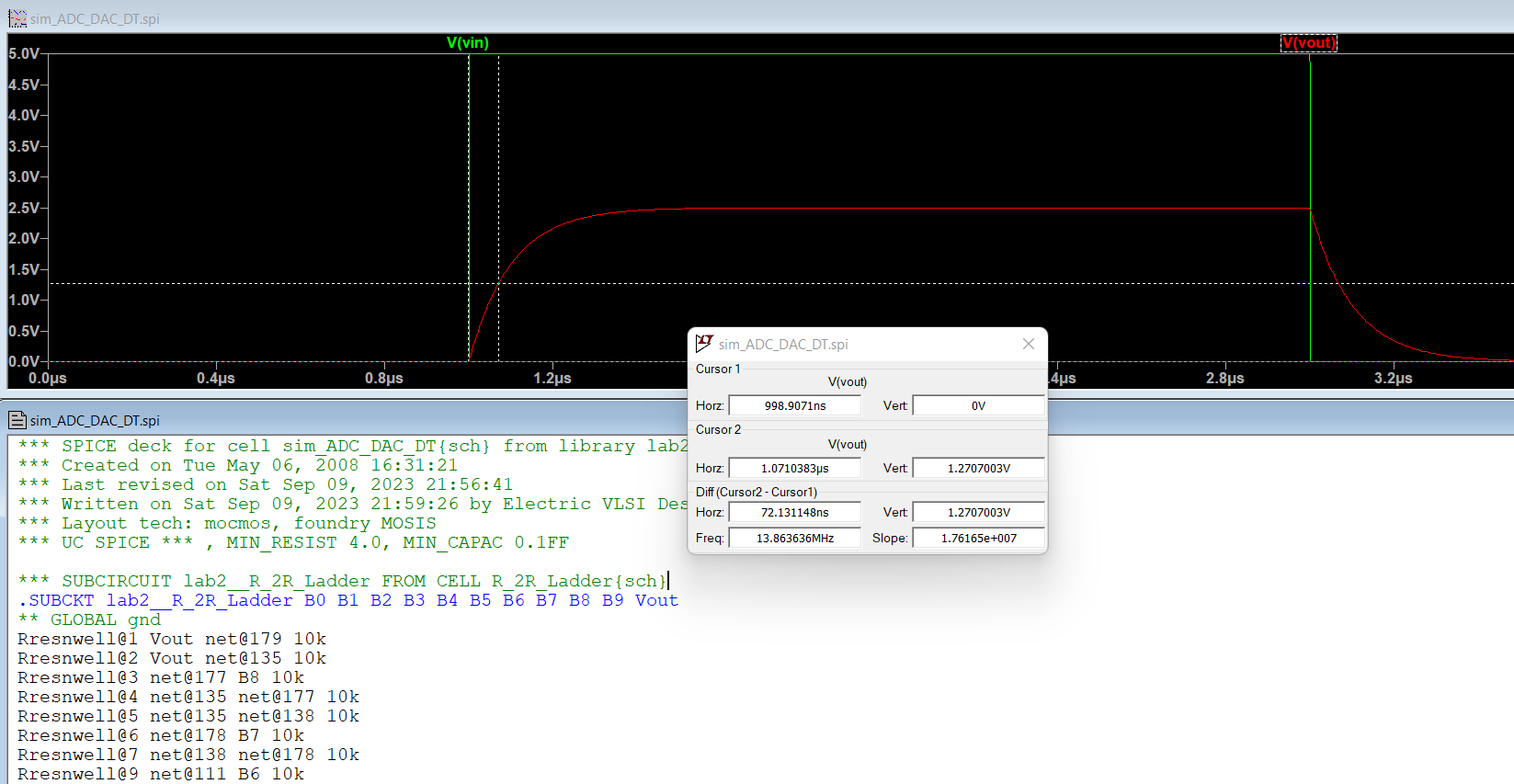

Calculated Rth for task 3: With B9 as the only input, B0-B8 were connected to ground and the circuit was reduced to the 20k resistor between B9 and Vout parallel with the equivalent resistance of the rest of the circuit. The rest of the circuit resistance simplified to 20k.

(1/20k+1/20k)^-1 = 10k

Calculated Vdd = 5V * 10k/20k = 2/5V

Calculated time delay for task 3: time delay = 0.7RC = 0.7*10*(10^3 ohm)*10*(10^-9 F) = 70 ns

3. Materials and Methods

Task 1:

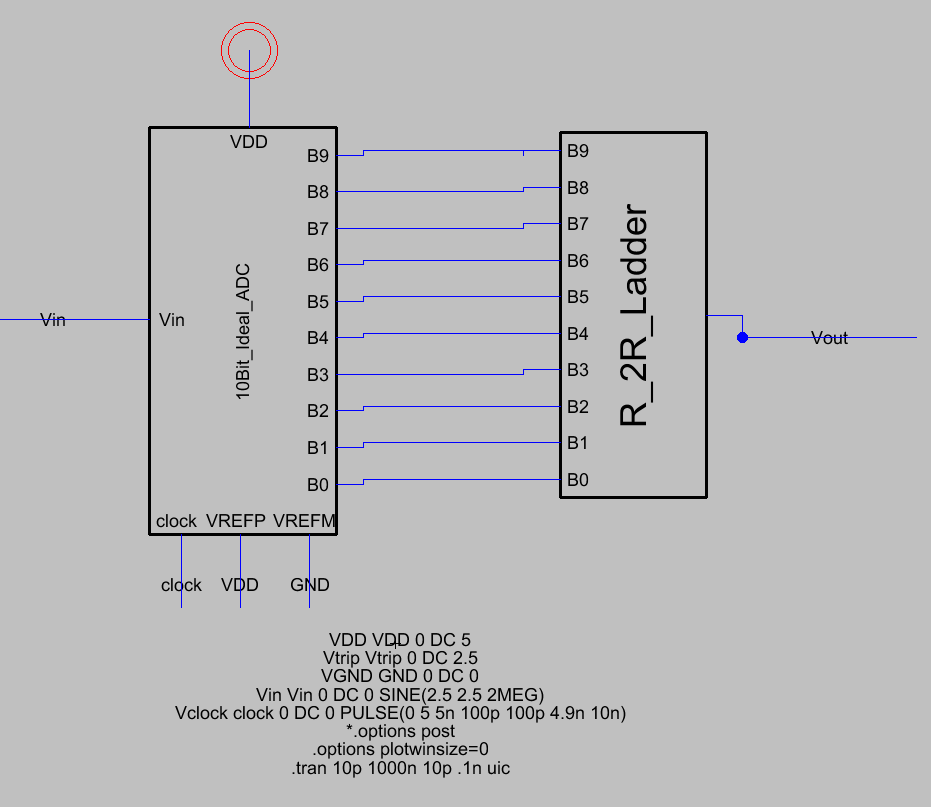

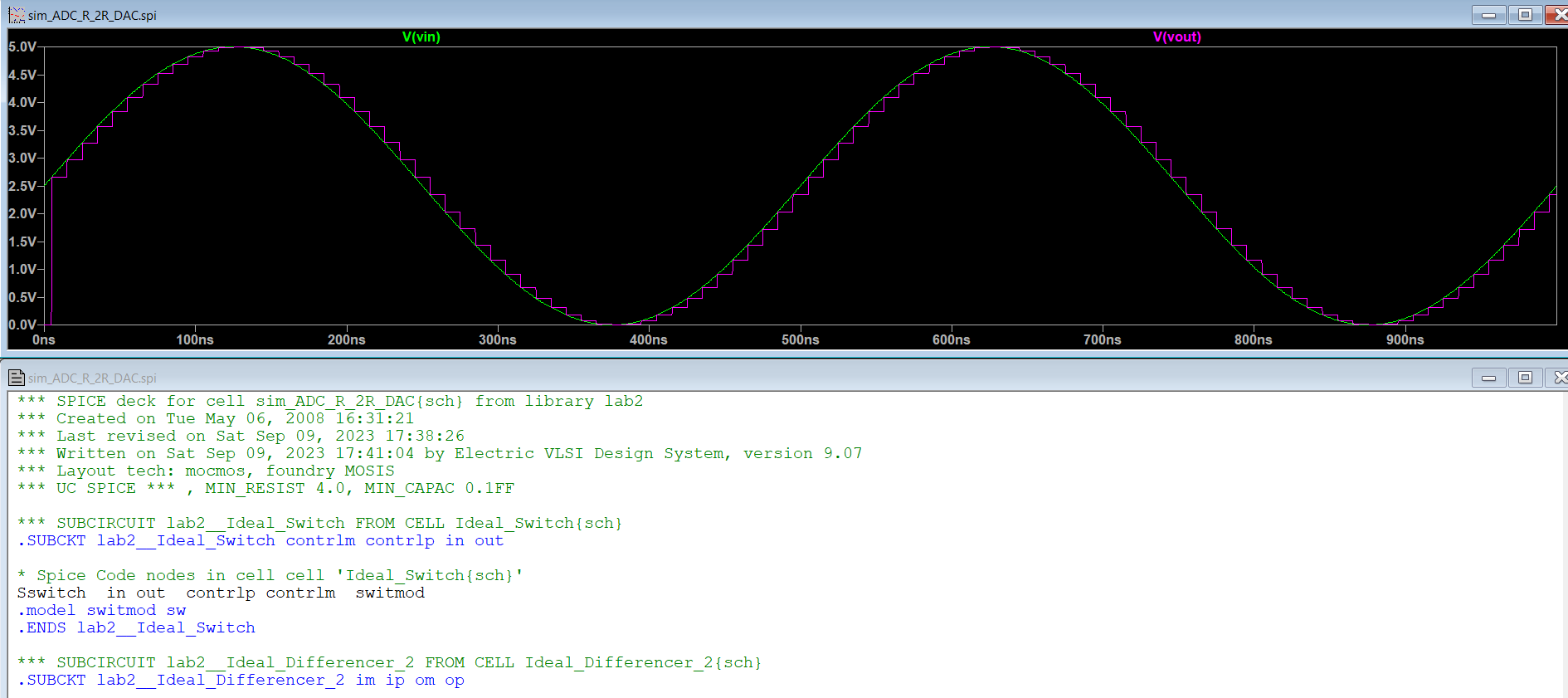

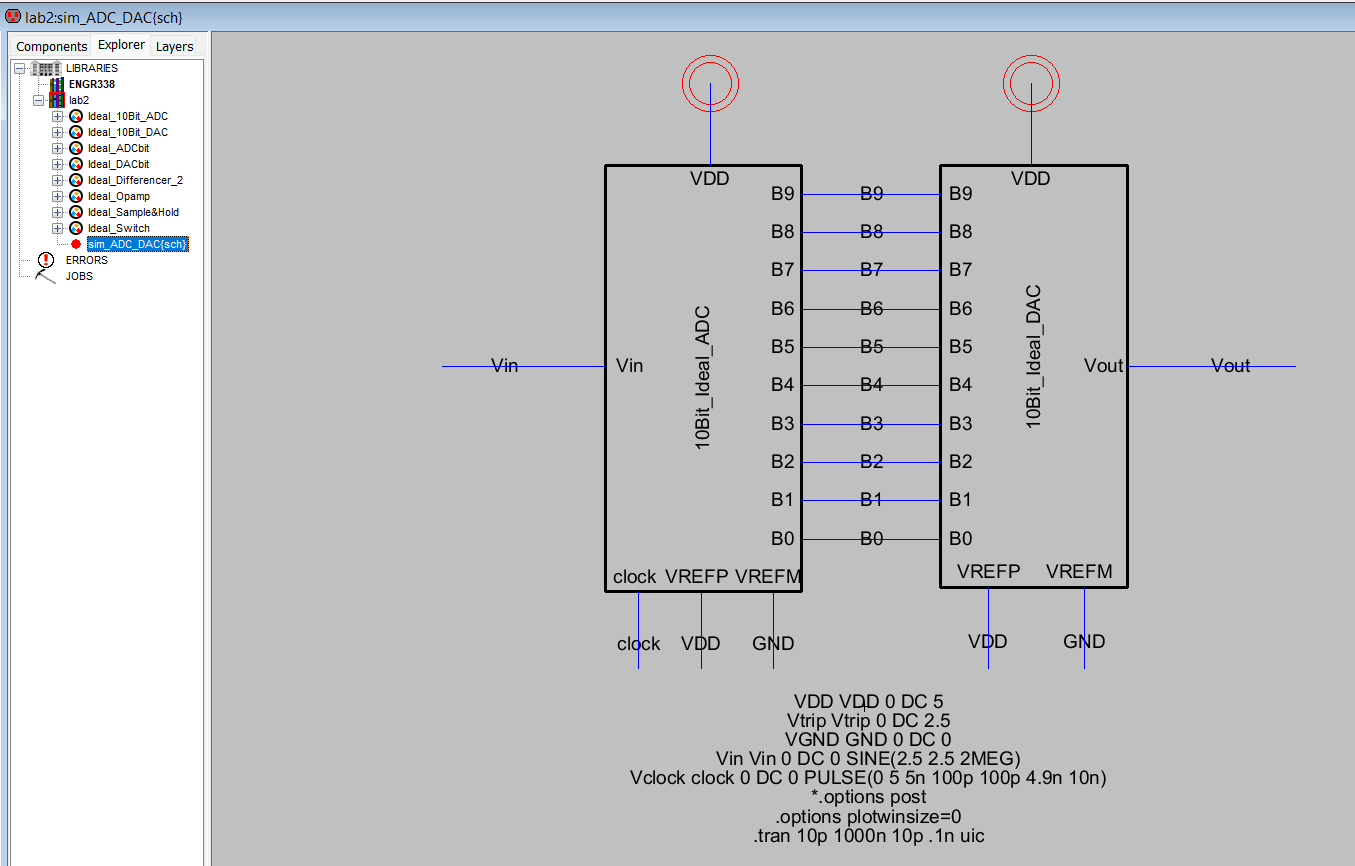

The ENGR 338 Electric VLSI libraries were imported and the 10-bit ADC to DAC schematic was selected for simulation. The schematic was exported to LTSpice for simulation to confirm the libraries and file paths were correct.

Task 2:

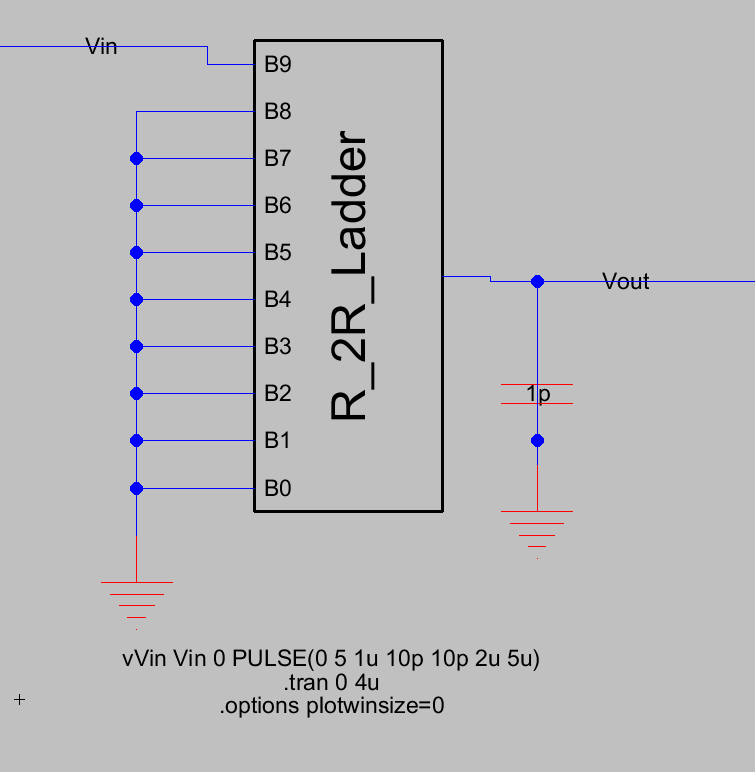

Electric VLSI was used to create a schematic of the R2_R ladder. An imported model of an analog to digital converter (ADC) was connected to the schematic of the R2_R ladder. The shematic was exported to LTSpice and was simulated with an input of 5V.

Task 3:

The R2_R ladder was simulated with an input to node B9 while the other nodes B0-B8 were connected to ground. A 10pF capacitor was connected to Vout. The input voltage was set to 5V. The time delay was measured using two cursers on the plot measuring the difference between 0V and 1/2 of the full scale voltage 1/2 Vdd, which is 1/4 Vdd or 1.25V. This value was compared to the theoretical value of 0.7RC, or 70ns.

4. Results (Your data/figure should have a caption. Figures should be labeled/numbered.)

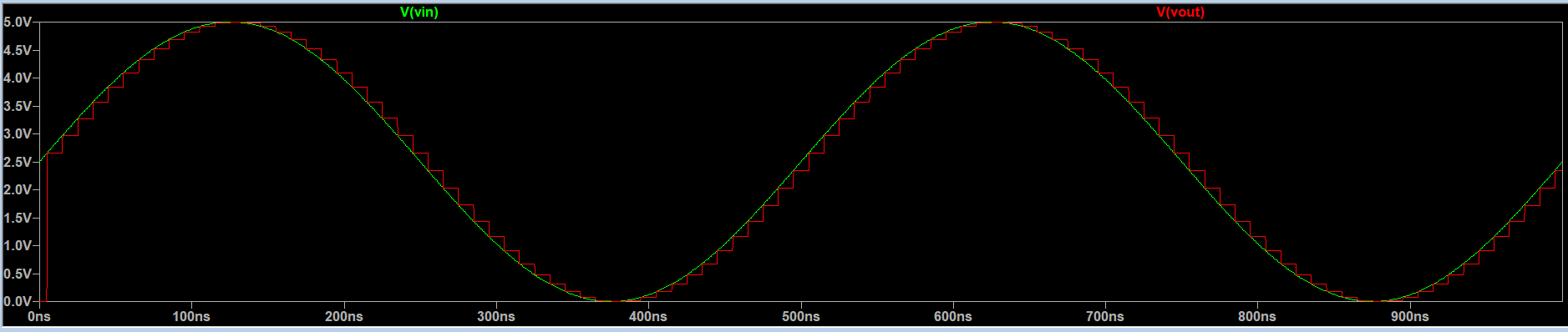

Figure 1 shows the libraries were installed correctly and the ADC_DAQ loaded the correct scehmatic into Electric. Figure confirms the file path to load the spice deck was working and the voltage in and out were 5V, as expected.

Figure 1: The shchematic of the ADC_DAQ loaded into Electric.