CE433 2022 Spring

Week 4

John Hitti

jdhitti@fortlewis.edu

Week 4

Introduction

In this week's

project we will be exploring different memory storage capabilities with

Verilog and Vivado simulations. We will be creating and simulating

various latch and flip-flops as well as working with rom memory files

and the IP core capabilities of Vivado.

Task 1

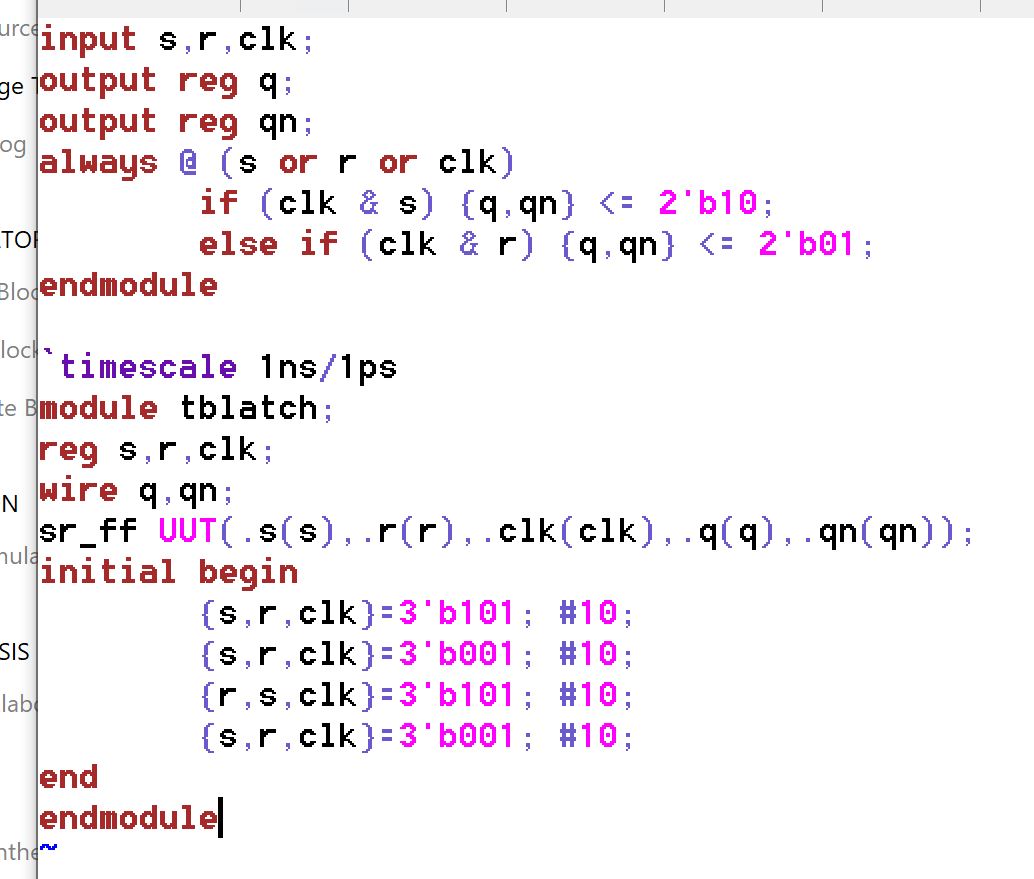

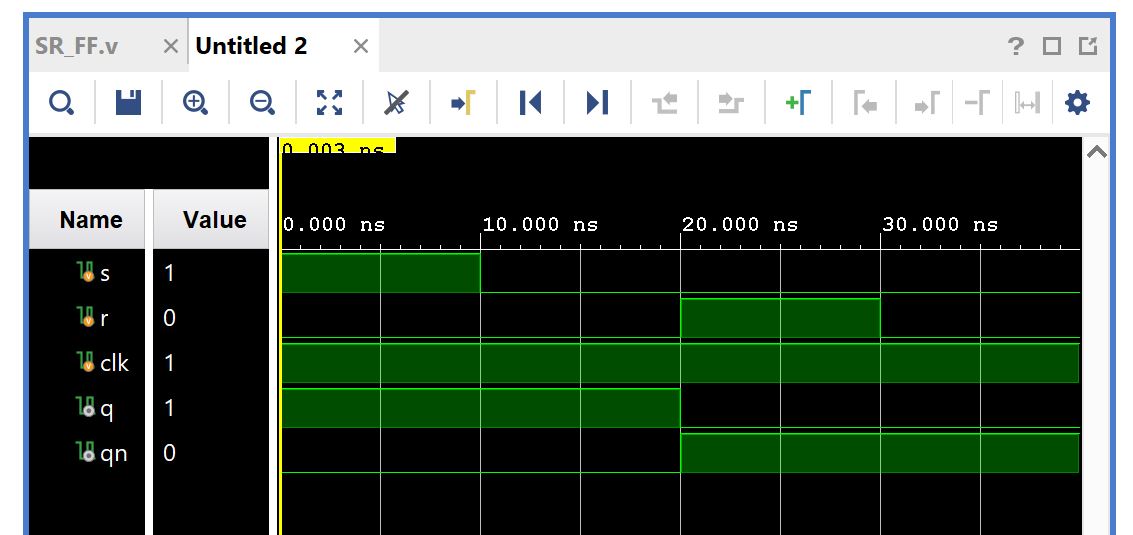

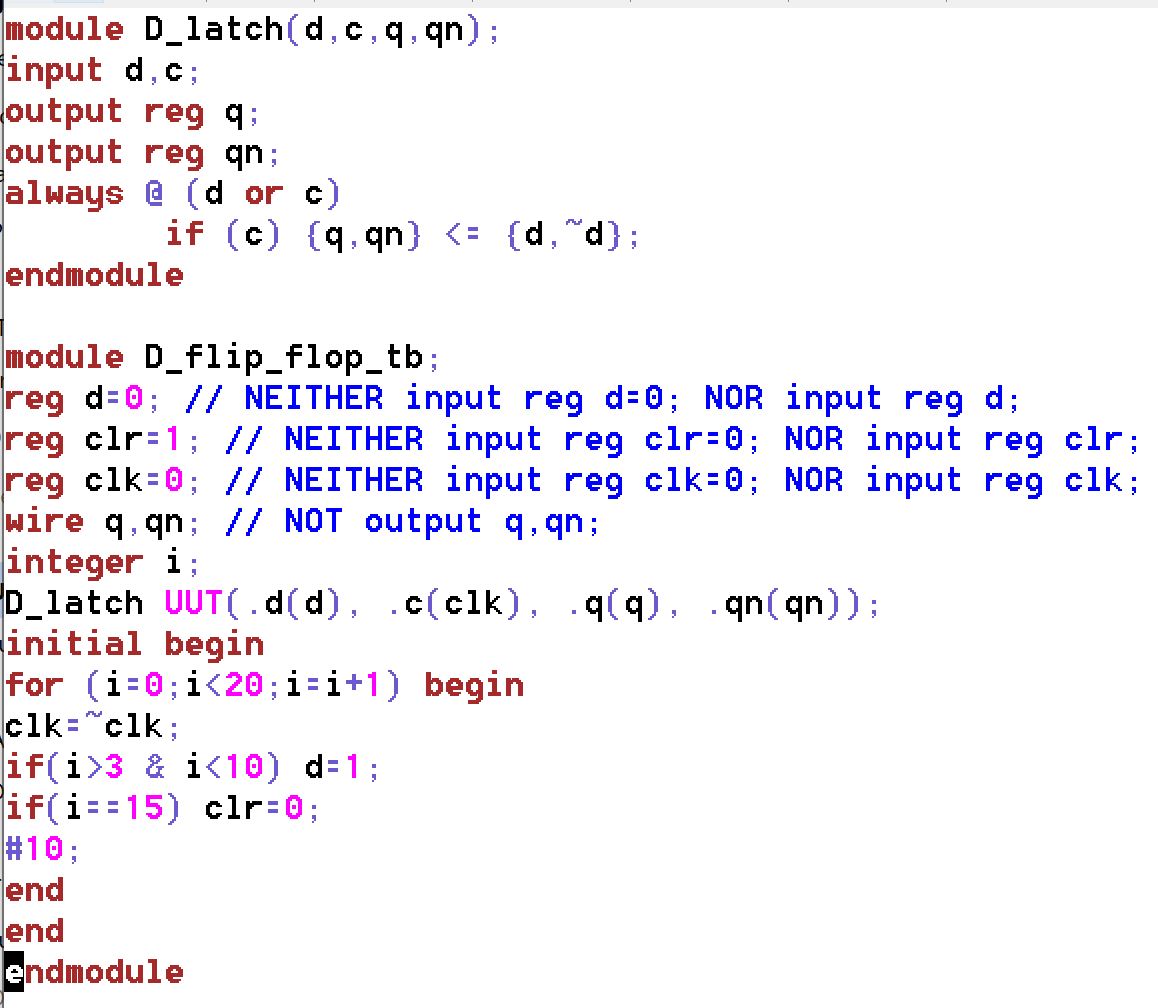

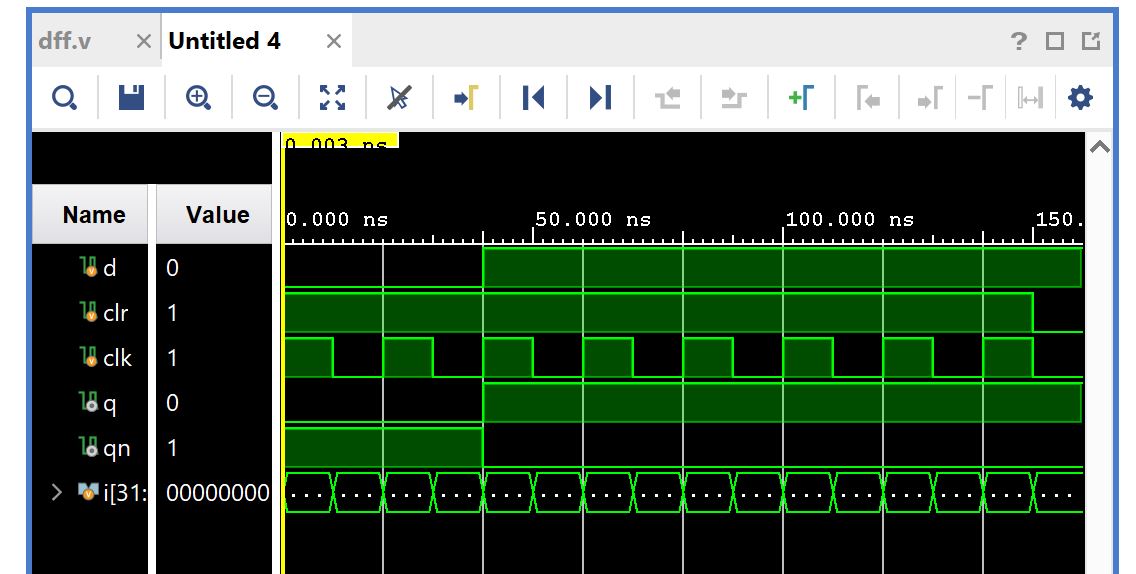

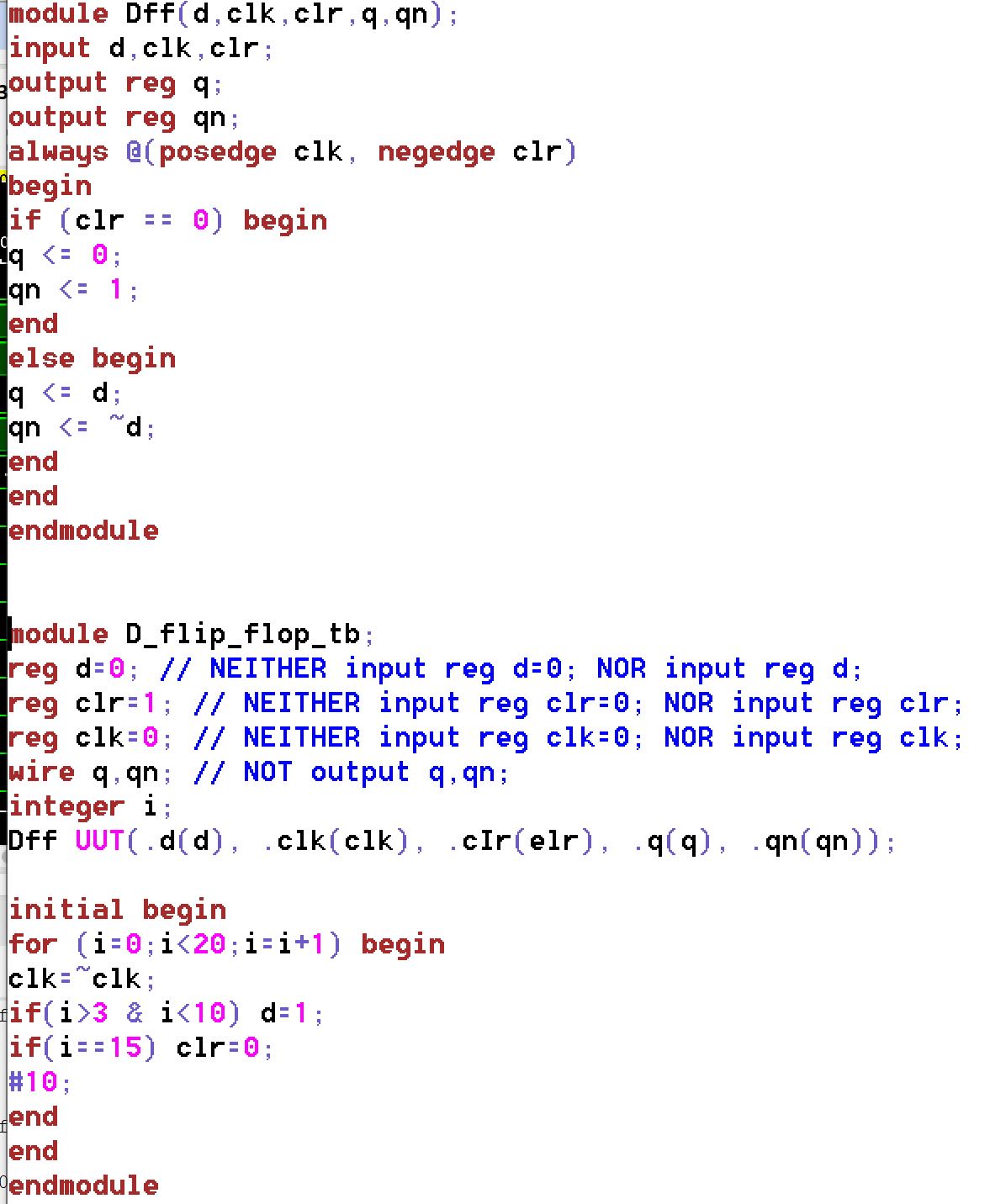

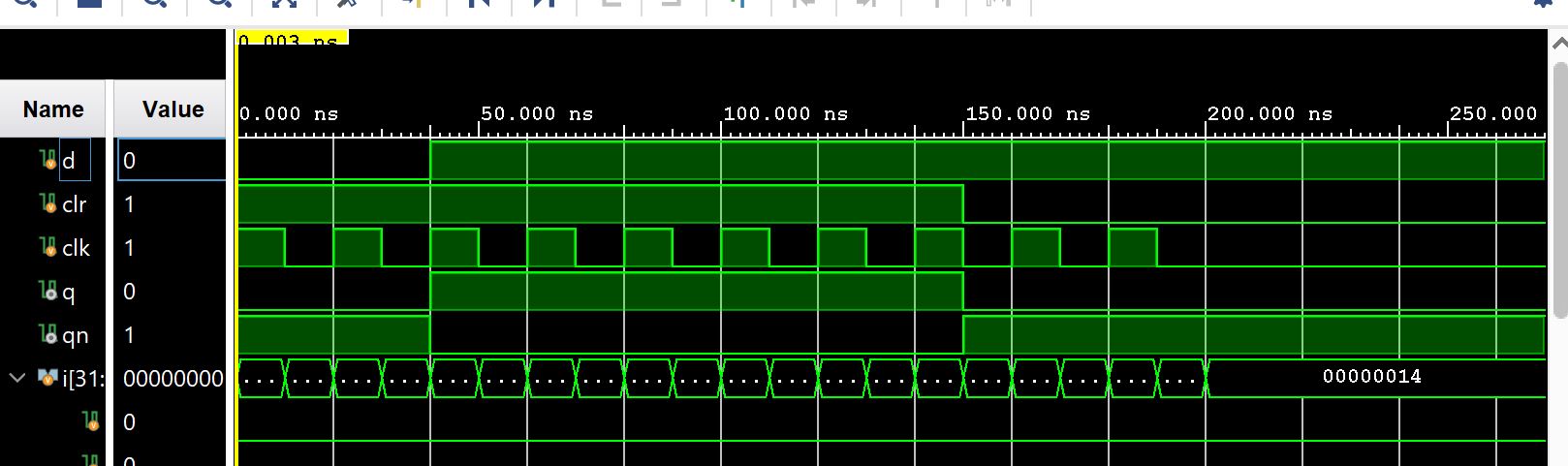

In this task we will repeat the simulations in section 1-3 by coding them in Verilog and running a simulation.

SR Flip-Flop

D Latch

Edge Triggered D Flip-Flop

Task 2

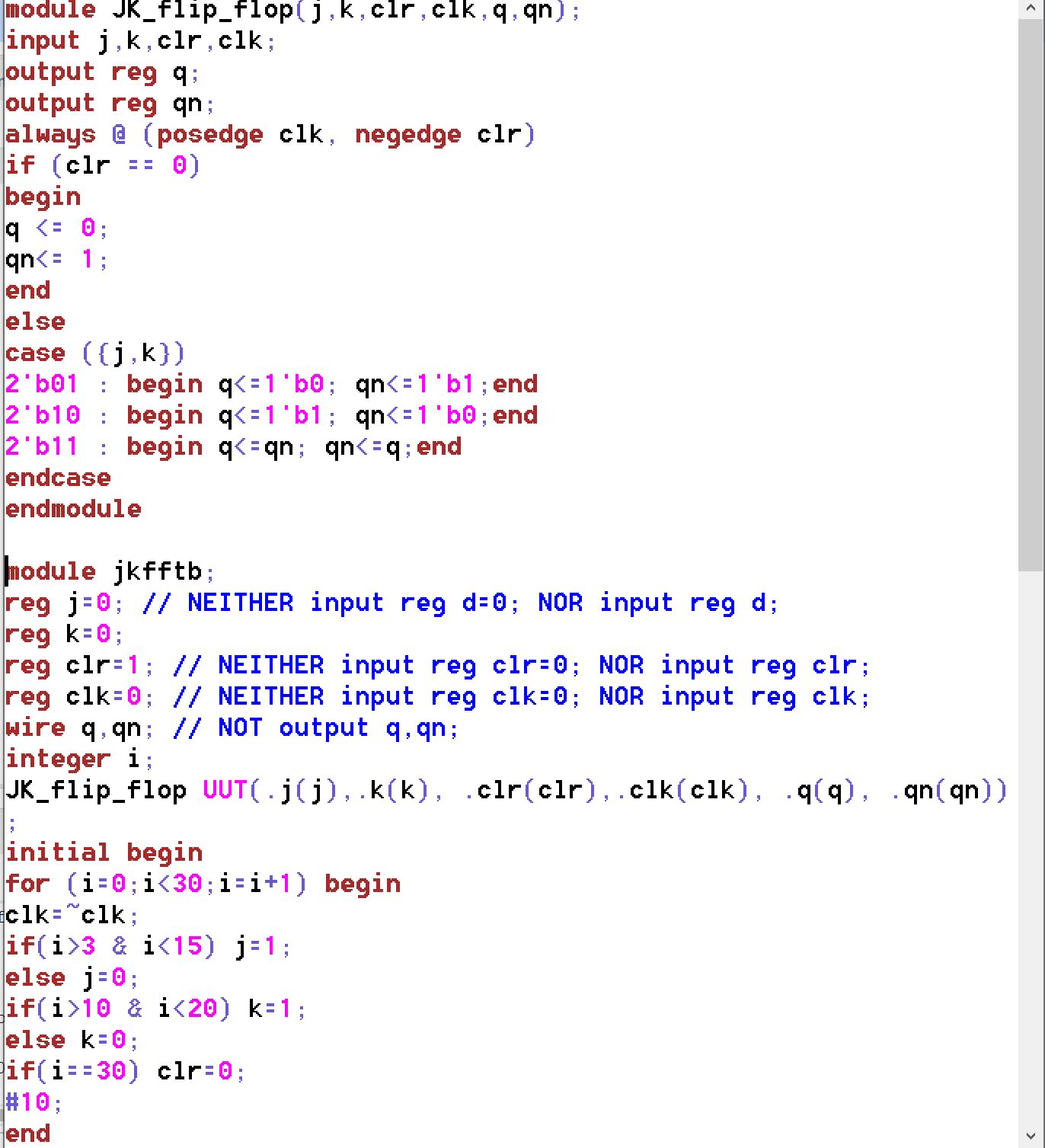

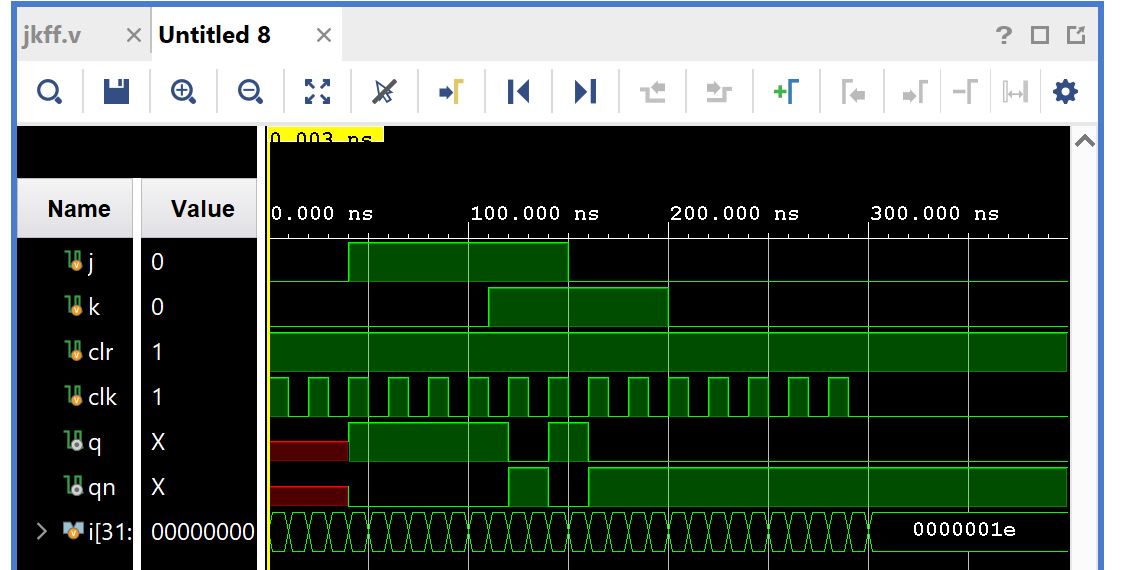

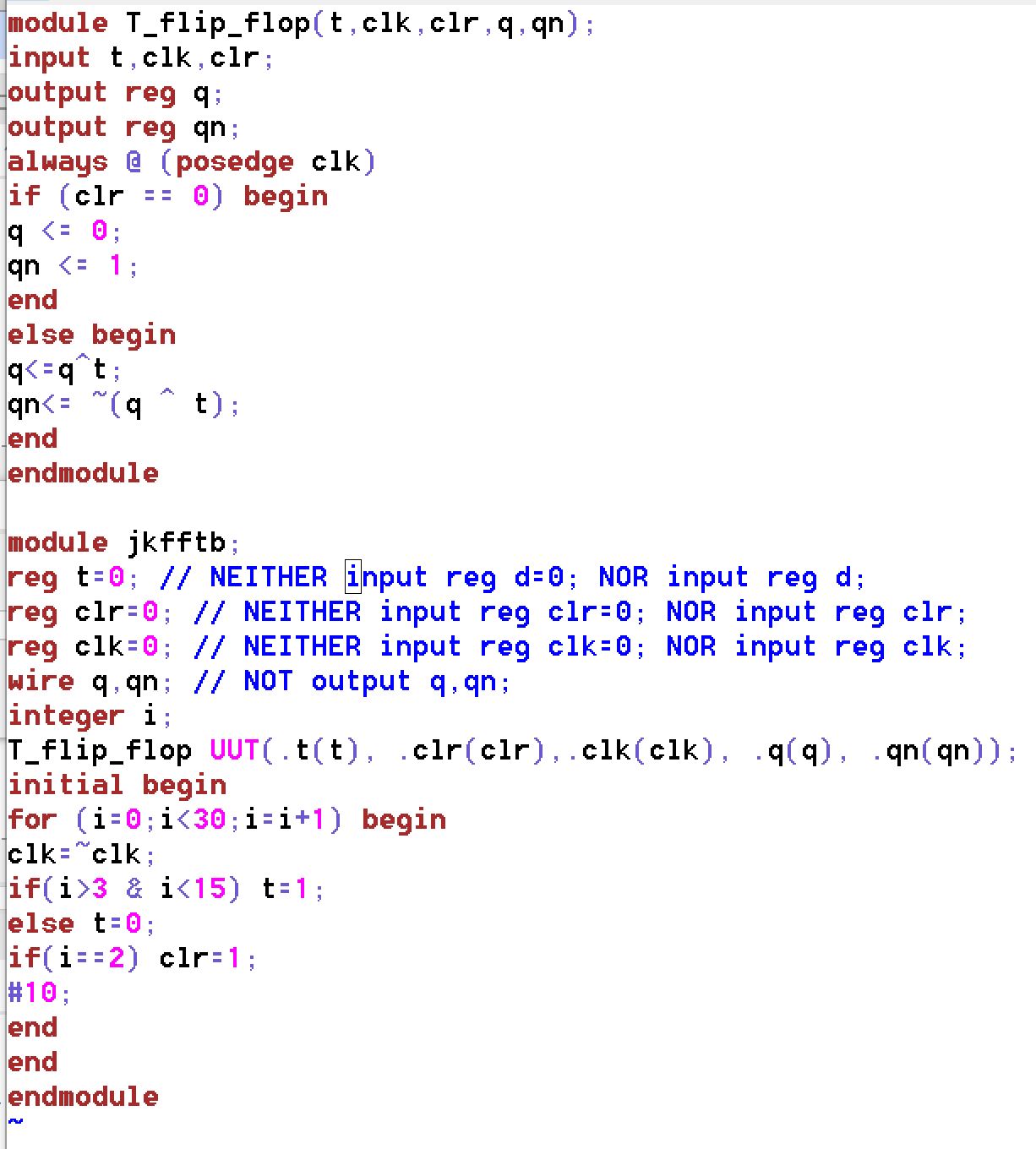

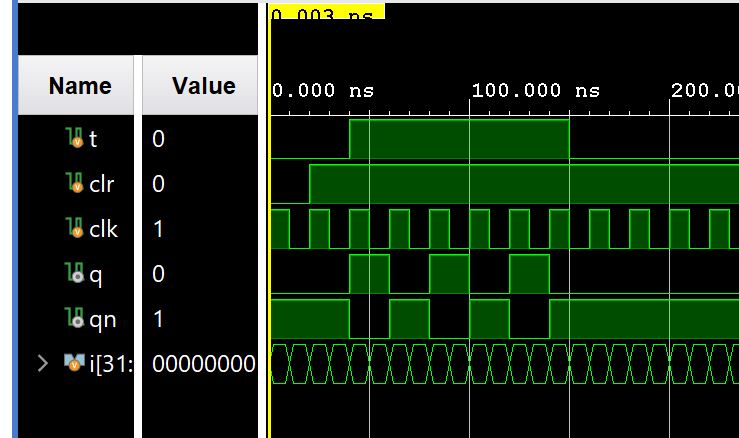

In this task we will write test benches for and run simulations for sections 4 and 5.

Edge Triggered JK Flip-Flop

The T Flip-Flop

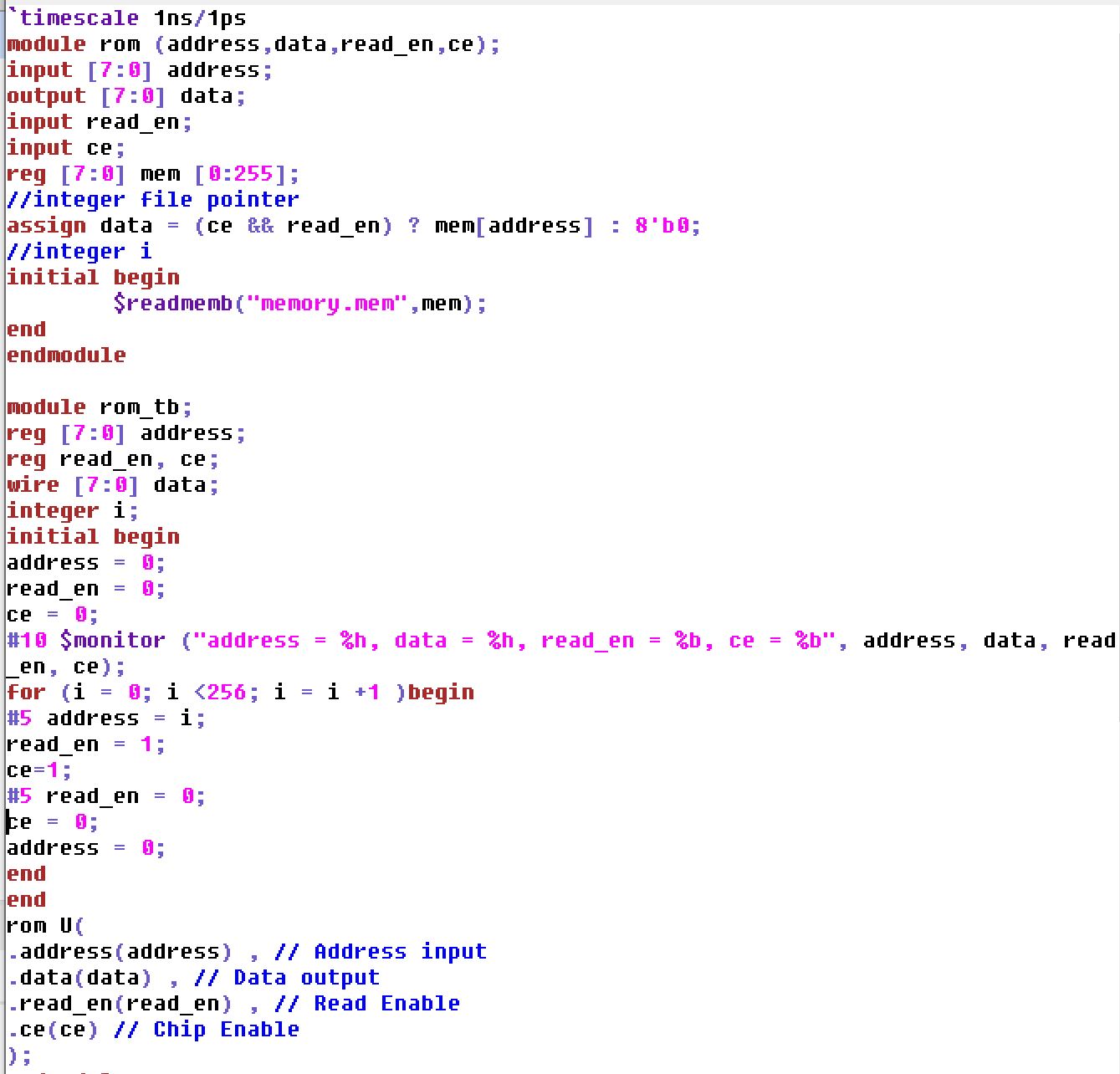

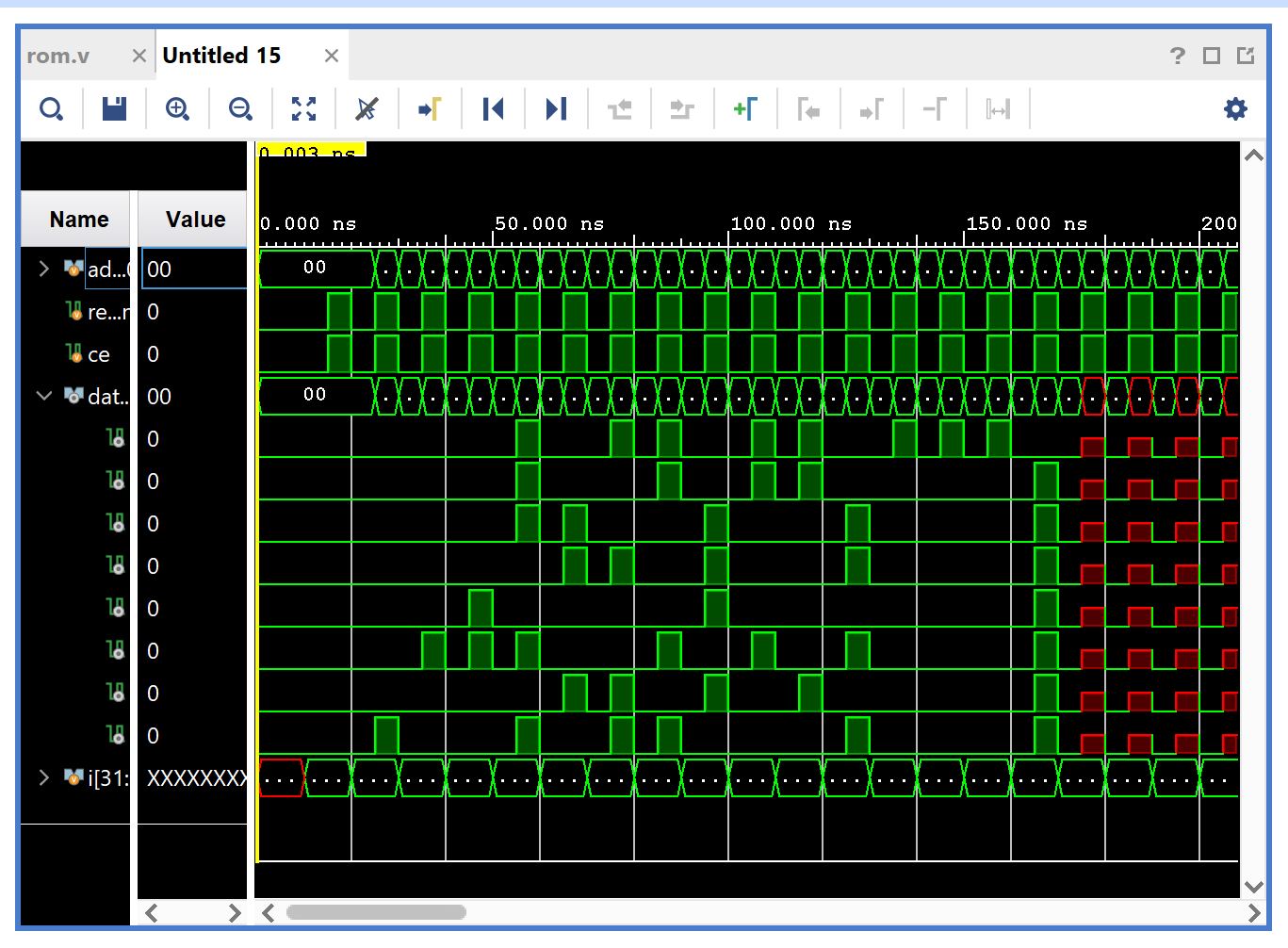

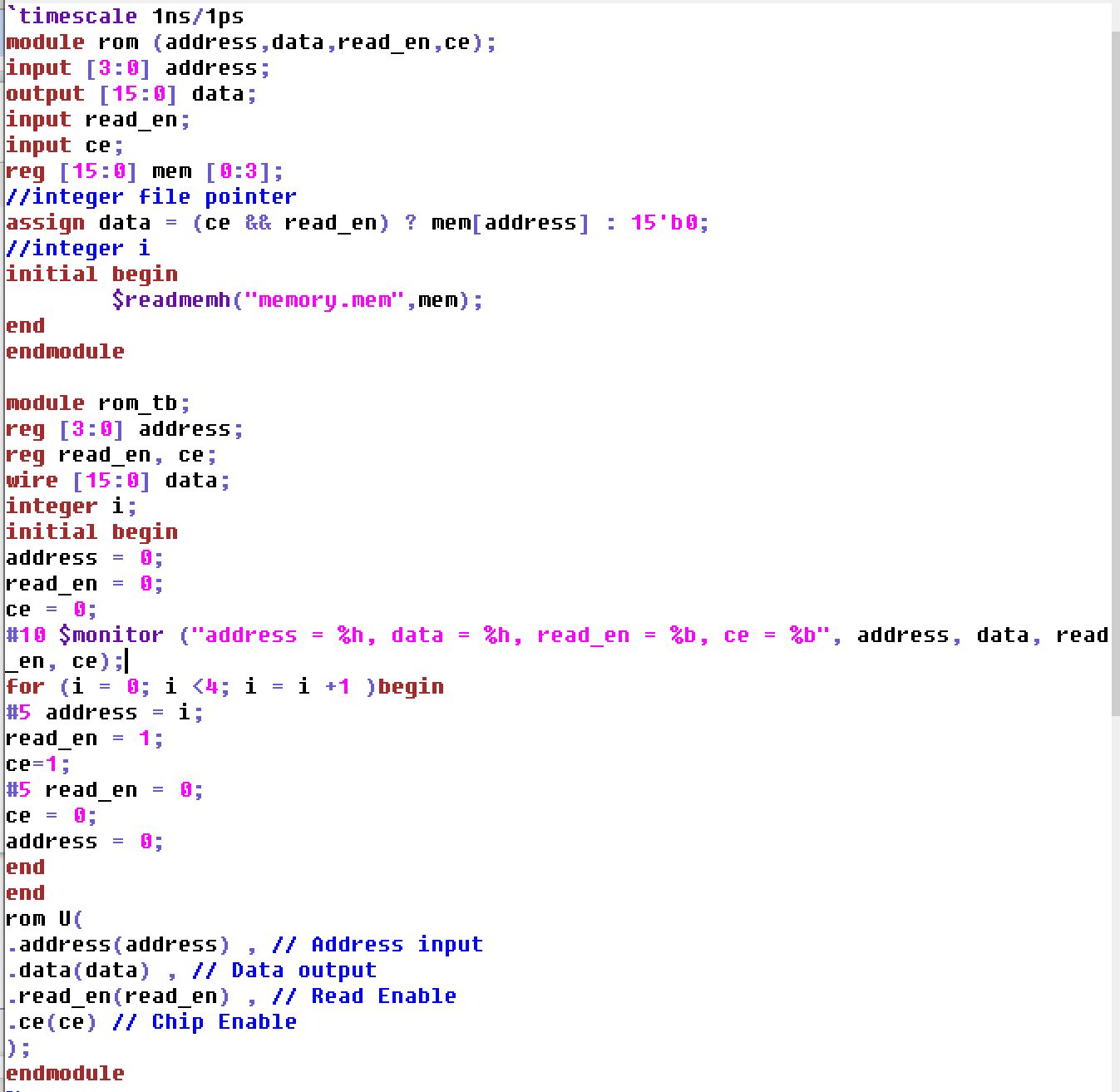

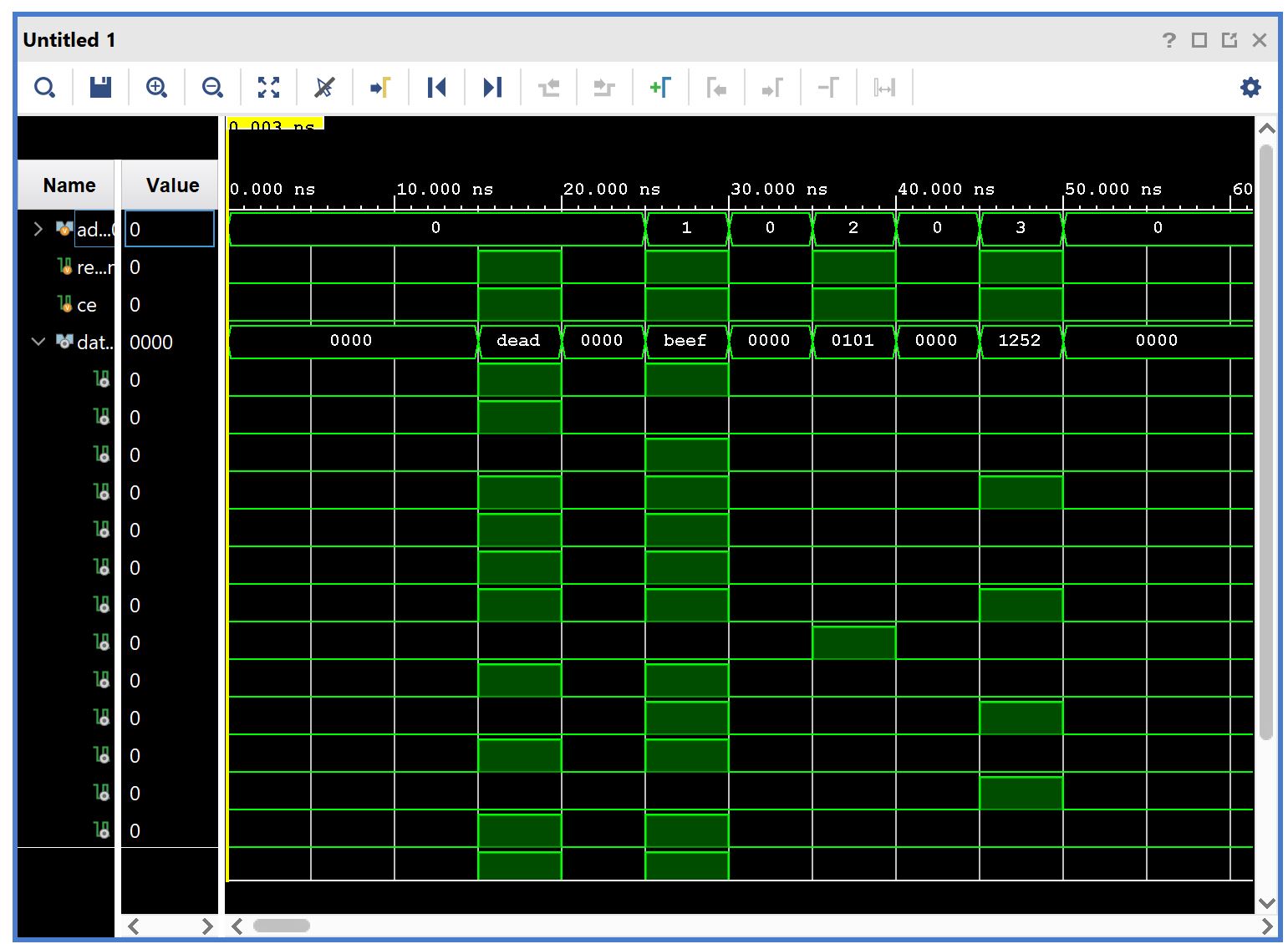

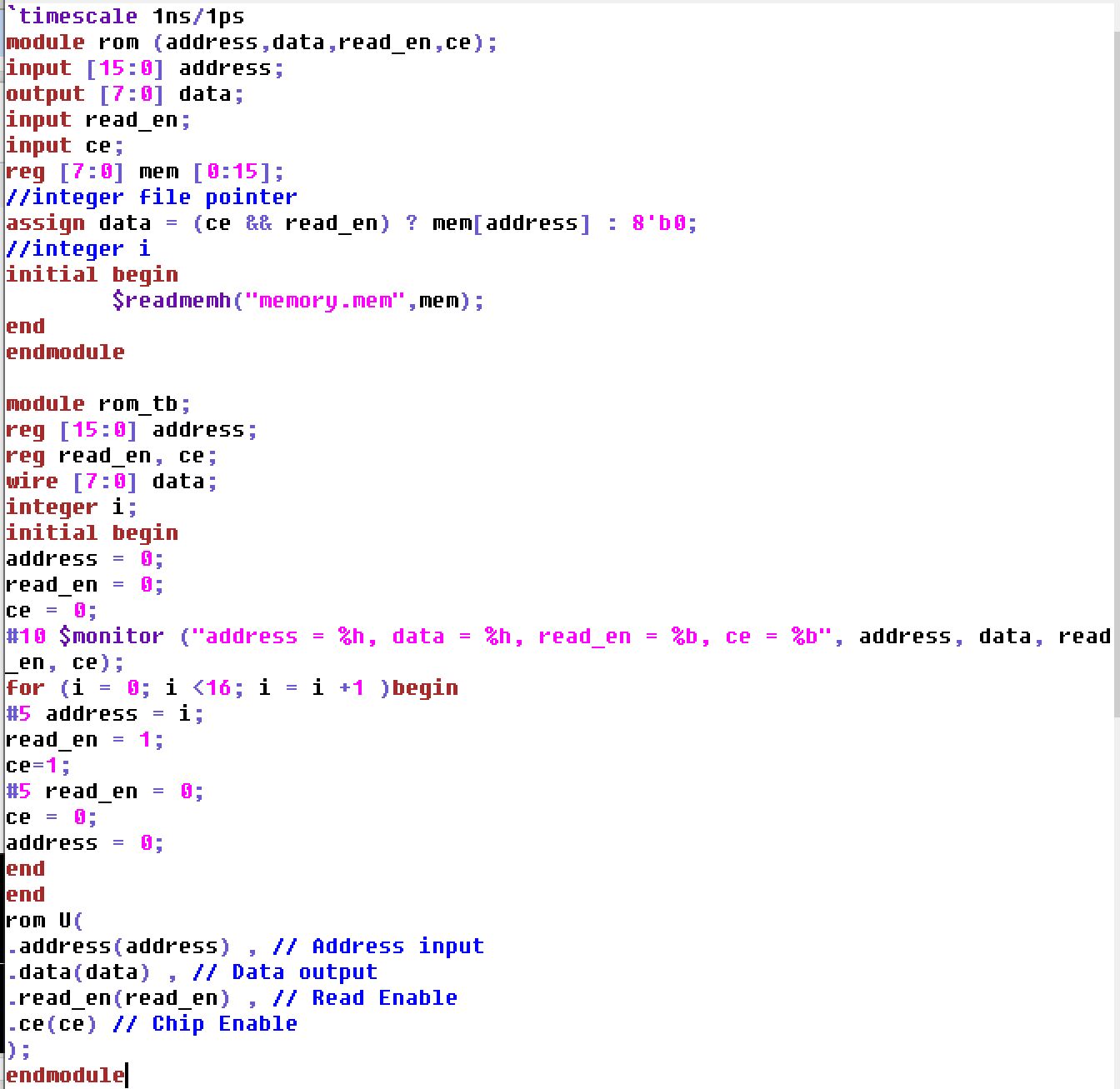

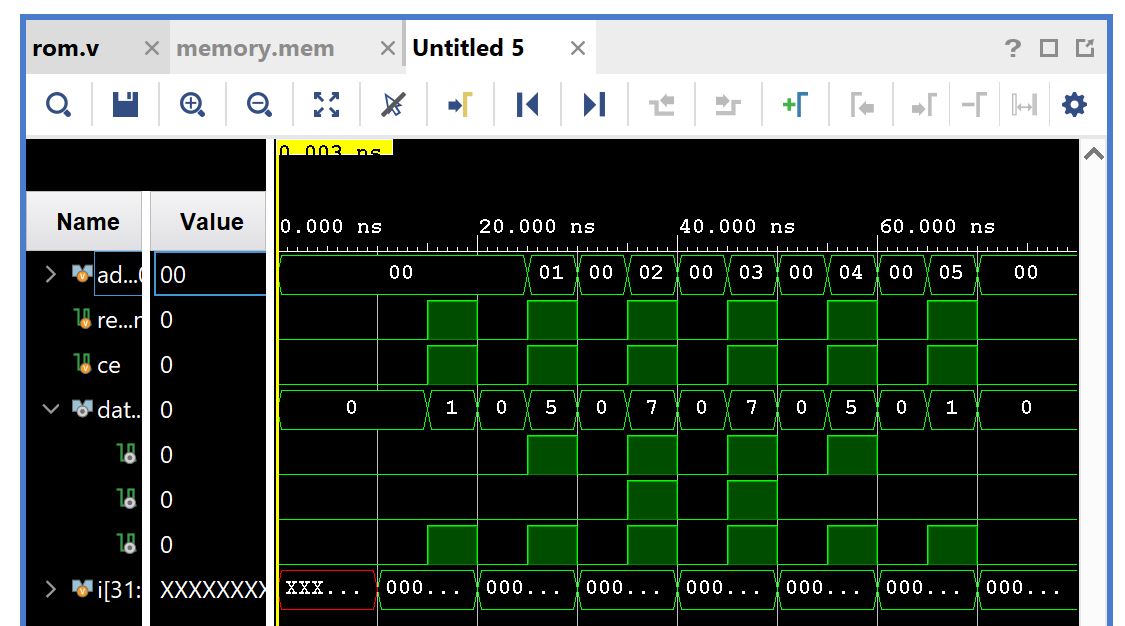

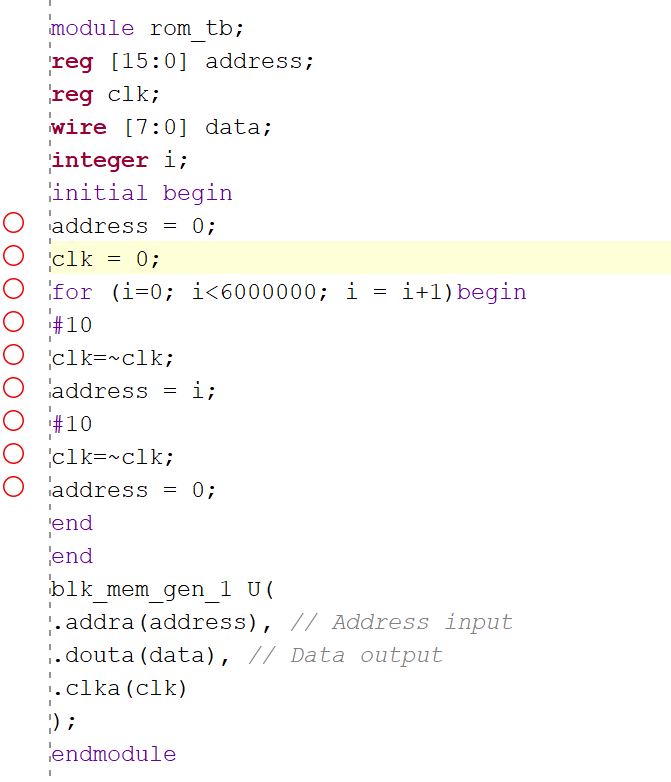

Task 3

In this task we will repeat the work in section 8.

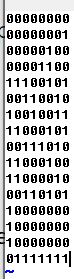

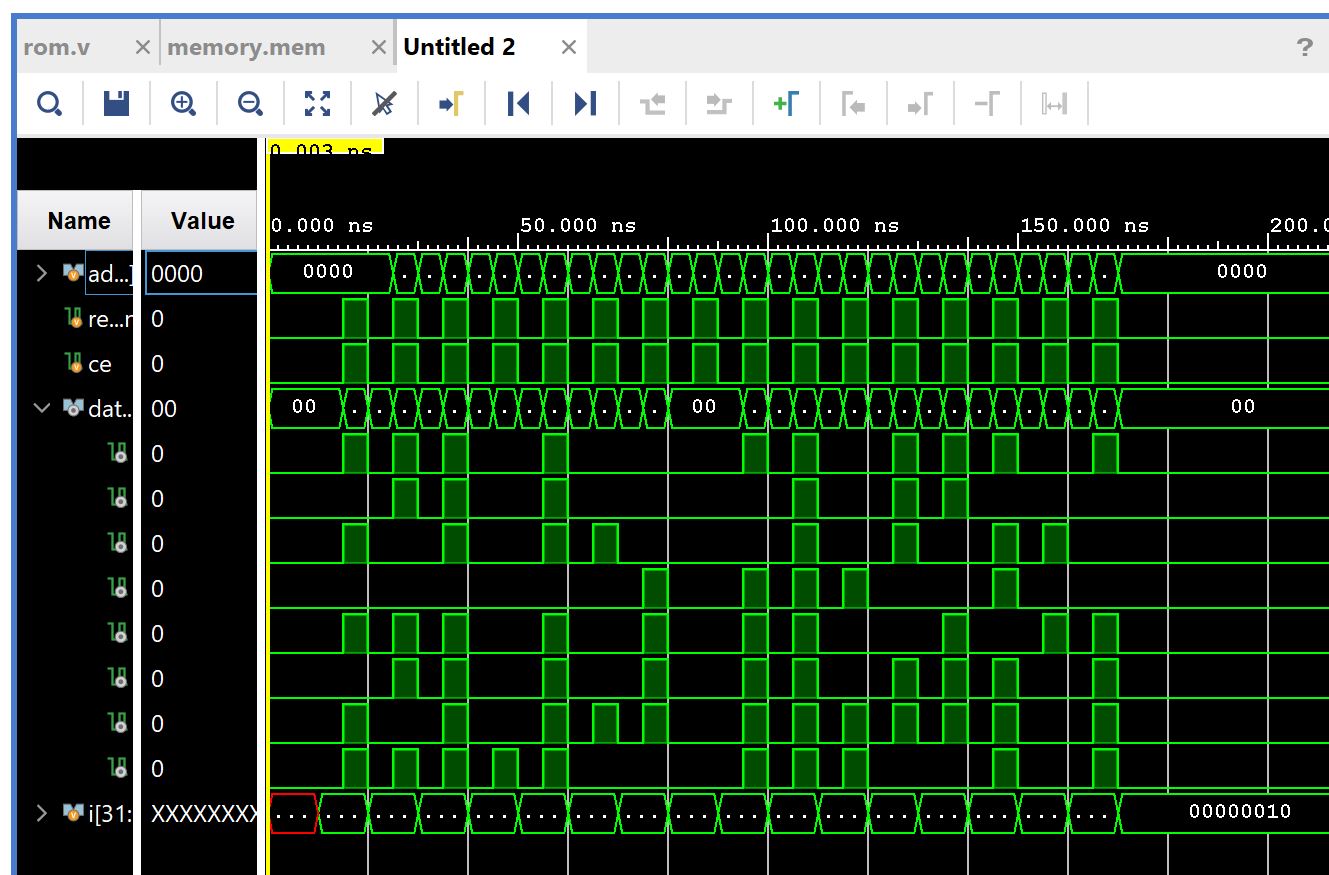

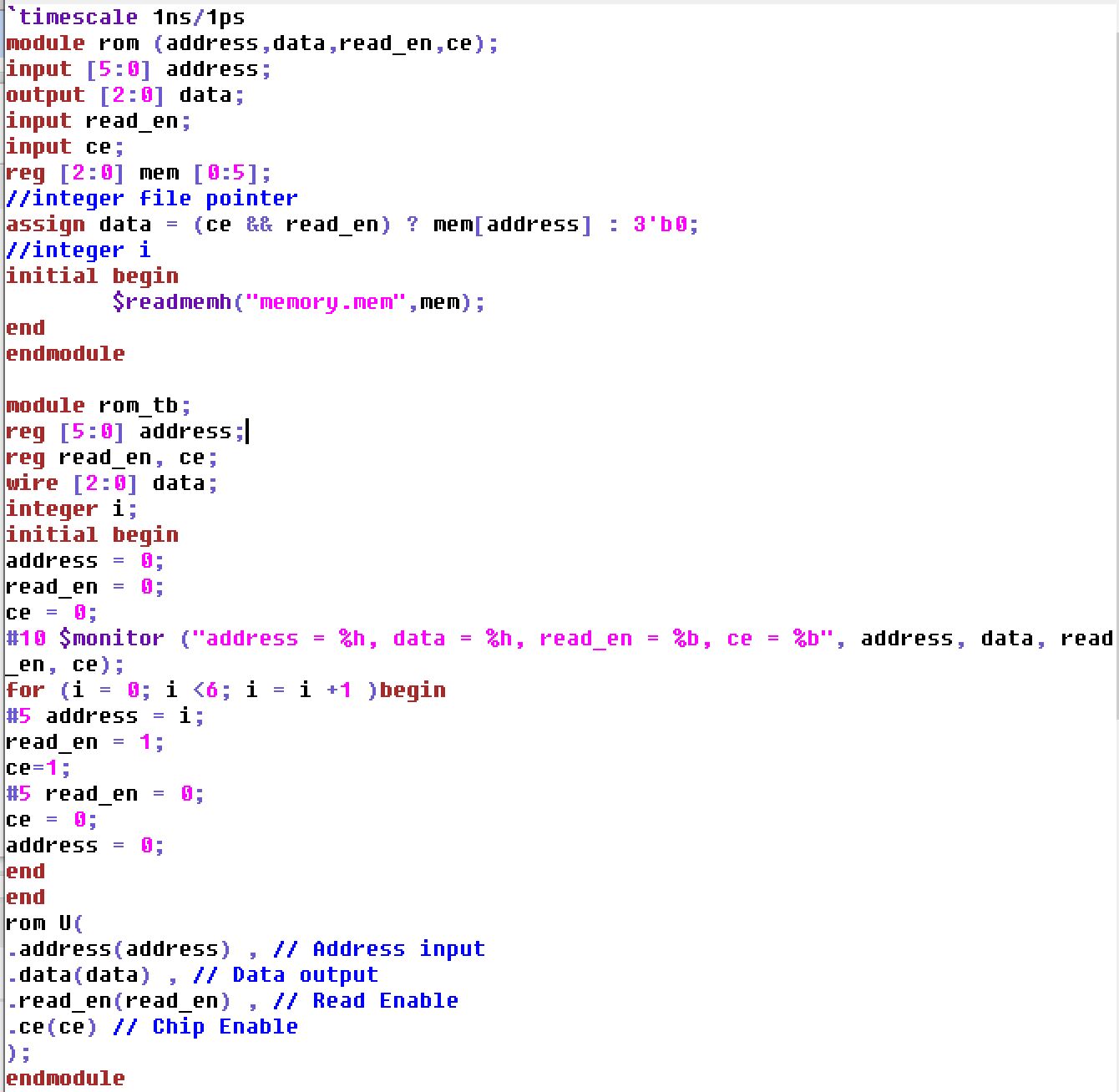

First we will make a program that can access a ROM file storing 8-bit hex information.

This is coded in Verilog and then tested with a simulation.

Now we can repeat this using a four hex data memory file.

Now we can repeat this for an 8-bit memory file.

Now we can repeat this for a 3-bit memory file.

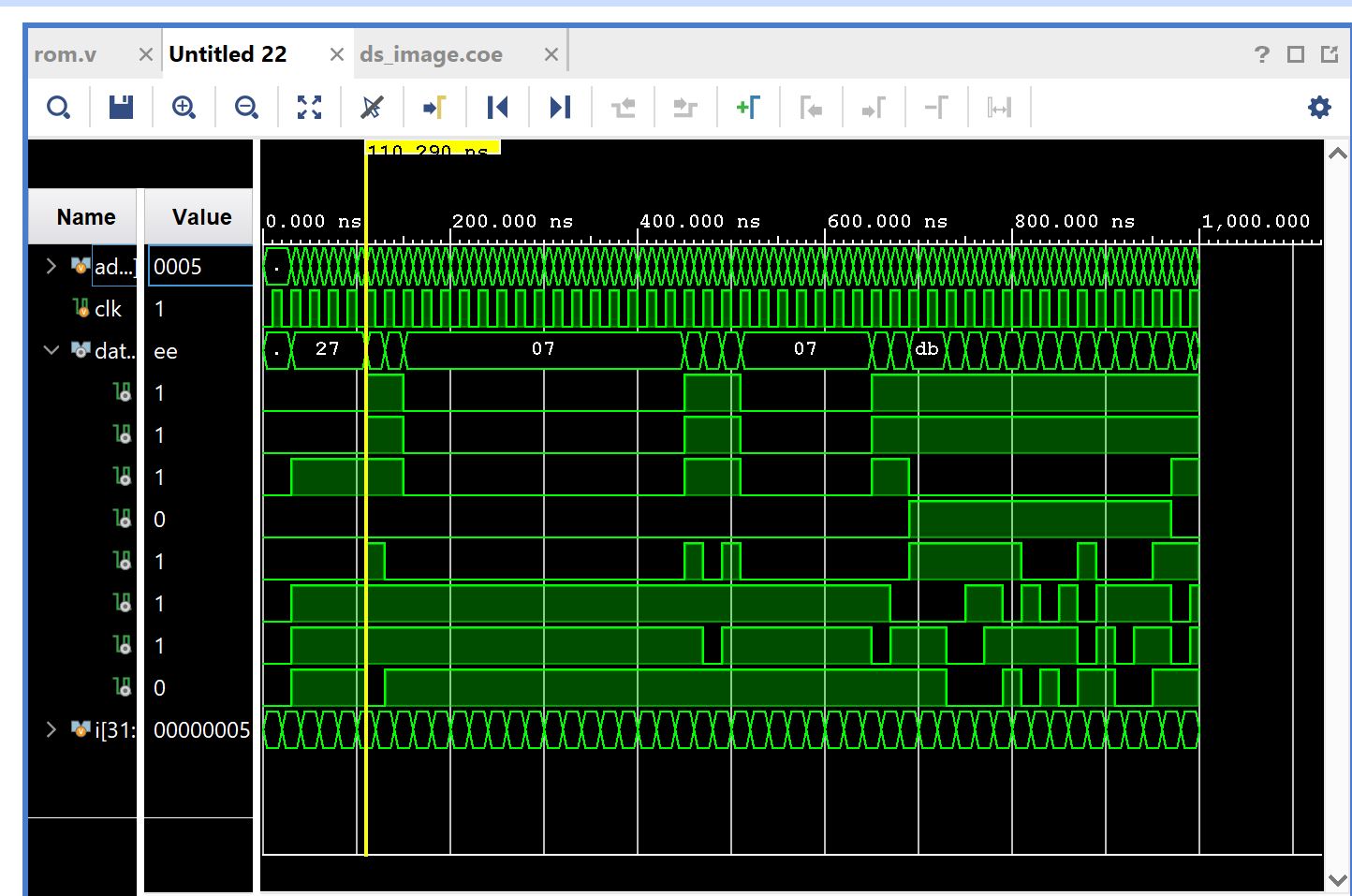

Now we can repeat this for the ROM IP Core (with an edited COE file to better illustrate the results)

Discussion

This

project is a great introduction to the wide variety of memory

capabilities in Verilog and Vivado and will help in further projects

that require this form of data processing.