CE 497 Xcelium Tutorial

Name: David Lee

Email:

djlee1@fortlewis.edu

Xcelium Tutorial

Introduction:

This

tutorial lays out methods which allow you to simulate verilog code in

Xcelium. The work flow of this program is similar to that of Vivado

which was learned in CE433 Embedded Devices. While working through this

tutorial if you want to create different simulations that you did in

vivado make sure that the outputs are the same and that is a way to

verify the correct output.

Materials and Methods:

Using the Cadence

Server, Xcelium Software installed on the Server, MobaXterm to log into

the server and basic Verilog coding practices.

Results:

Task 1: Change the .bashrc file on the server to be able to launch Xcelium

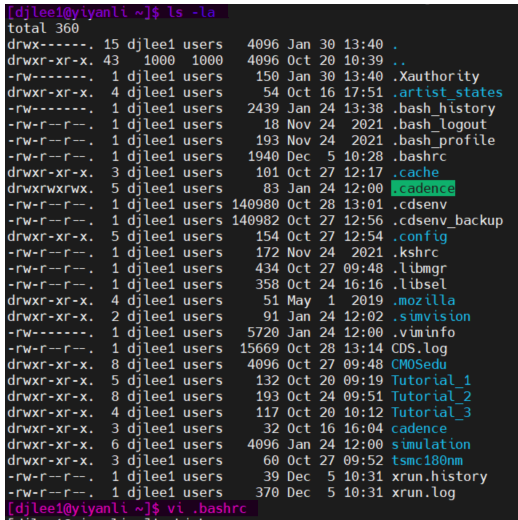

# .bashrc

# Source global definitions

if [ -f /etc/bashrc ]; then

. /etc/bashrc

fi

export CDSHOME=/4Tbhardrive/cadence/cadence/installs/IC618

export MMSIMHOME=/cadence/SPECTRE181/

export XCELIUMHOME=/4Tbhardrive/home/Xcelium

export LANG=C

export ASSURAHOME=/4Tbhardrive/cadence/cadence/installs/ASSURA41

export

PATH=$CDSHOME/tools/bin:$CDSHOME/tools/dfII/bin:$MMSIMHOME/tools/bin:$MMSIMHOME/tools/dfII/bin:$ASSURAHOME/tools/assura/bin:

$ASSURAHOME/tools/bin:$XCELIUMHOME/tools/bin:$PATH

export CDS_AUTO_64BIT=ALL

export

LD_LIBRARY_PATH=$AMSHOME/tools/lib:$CDSHOME/tools.lnx86/lib:/usr/lib:/usr/dt/lib:/usr/openwin/lib/usr/lib:$AMSHOME/tools/lib:/usr/dt/lib:/usr/openwin/lib:

$CDSHOME/tools.lnx86/lib:$AMSHOME/tools/lib/64bit:$AMSHOME/tools/lib:$ASSURAHOME/tools/lib:/usr/lib/libstdc++.so.6:$LD_LIBRARY_PATH

export CDS_LIC_FILE=5280@obelisk.srv.fortlewis.edu

export SPECTRE_DEFAULTS=-E

export CDS_Netlisting_Mode=Analog

export CDS_LOAD_ENV=CWDElseHome

export CDK_DIR=/4Tbhardrive/ncsu-cdk-1.6.0.beta

export tsmc=/4Tbhardrive/Users/djlee1/tsmc180nm/180_MS_RF_G/PDK/Cadence_OA/t018cmsp018k3_1_0a/tsmc180nm

export SUBSTRATESTORMHOME=$ASSURAHOME

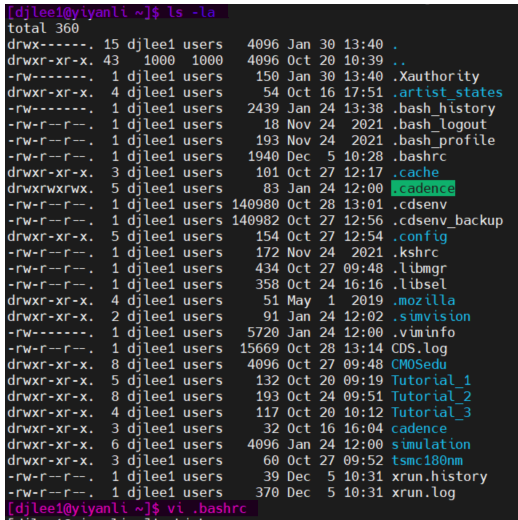

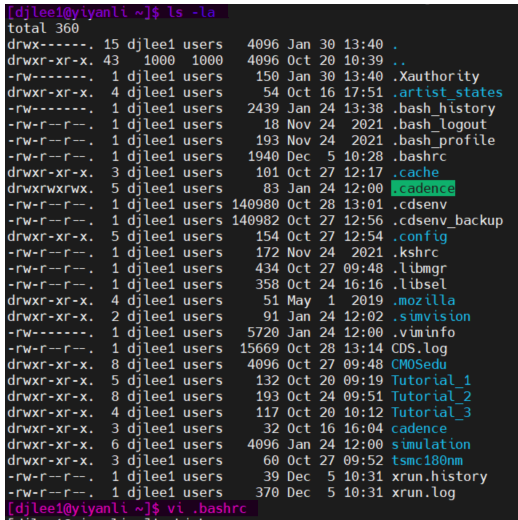

Figure 1: Purple

Highlight at the top shows how to access the hidden directory that the

.bashrc file is in. Pink Highlight at the bottom shows how to open the

.bashrc file.

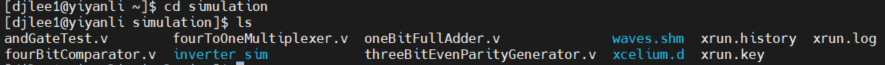

Figure 2: Shows the edited .bashrc file

Figure 3: Shows the successful completion of the bashrc file and shows that Xcelium will launch correctly

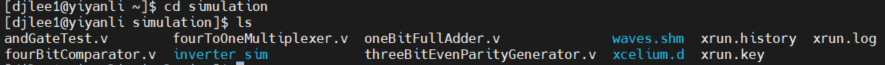

Task

2: Create a new folder that is called Simulations and create andGate.v to simulate

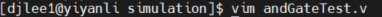

Figure 4: Shows the created simulation folder with the files that will be ran in the simulation

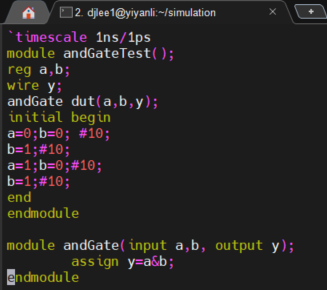

Figure

5: Shows prompt needed to create a new verilog file

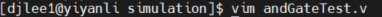

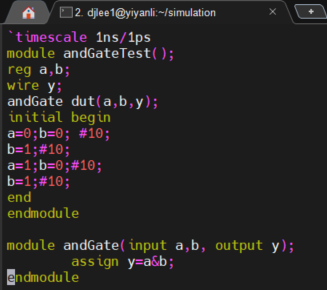

Figure 6: Shows the

code needed for the andGateTest

Task 3: Simulate the andGateTest.v File

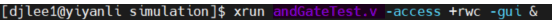

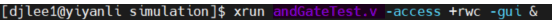

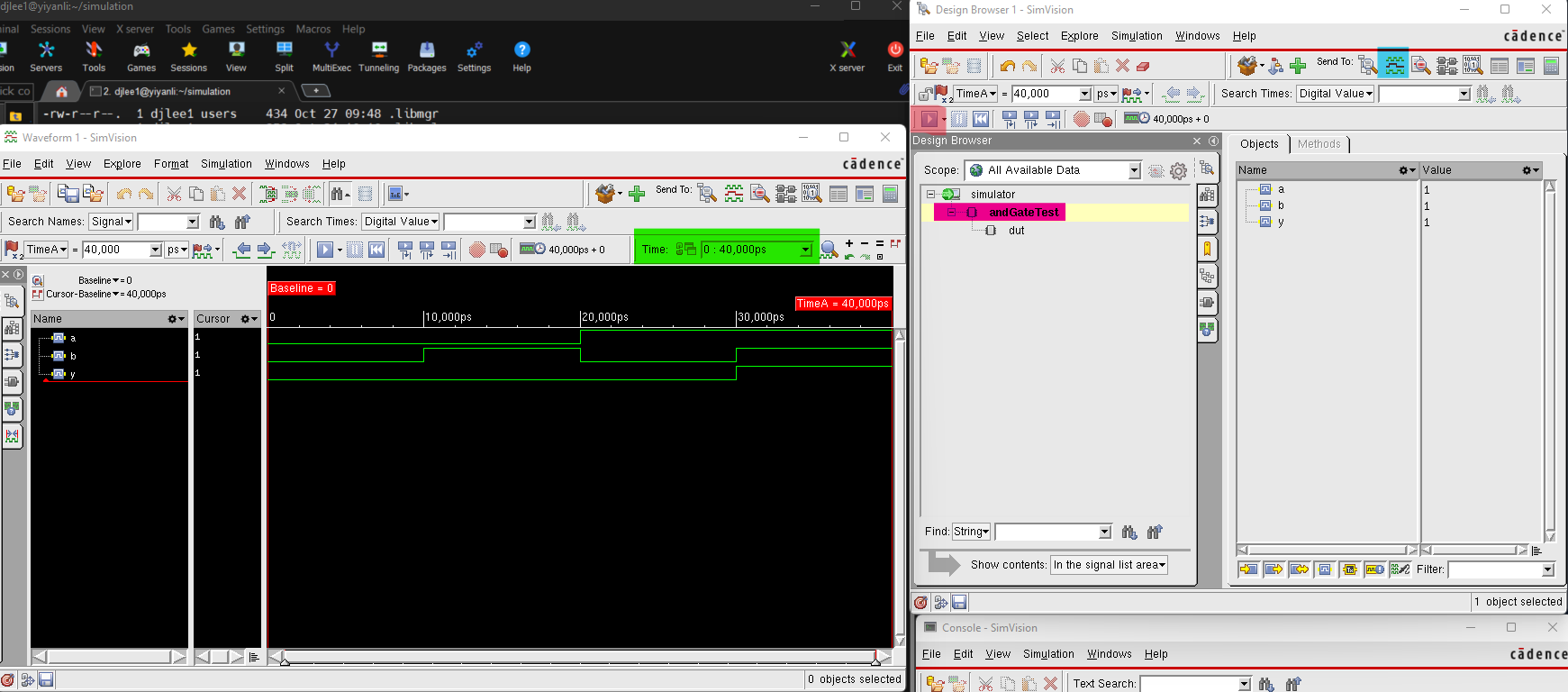

Figure 7: Shows the command to start simulation. The Purple highlight is the file which you will be wanting to simulate.

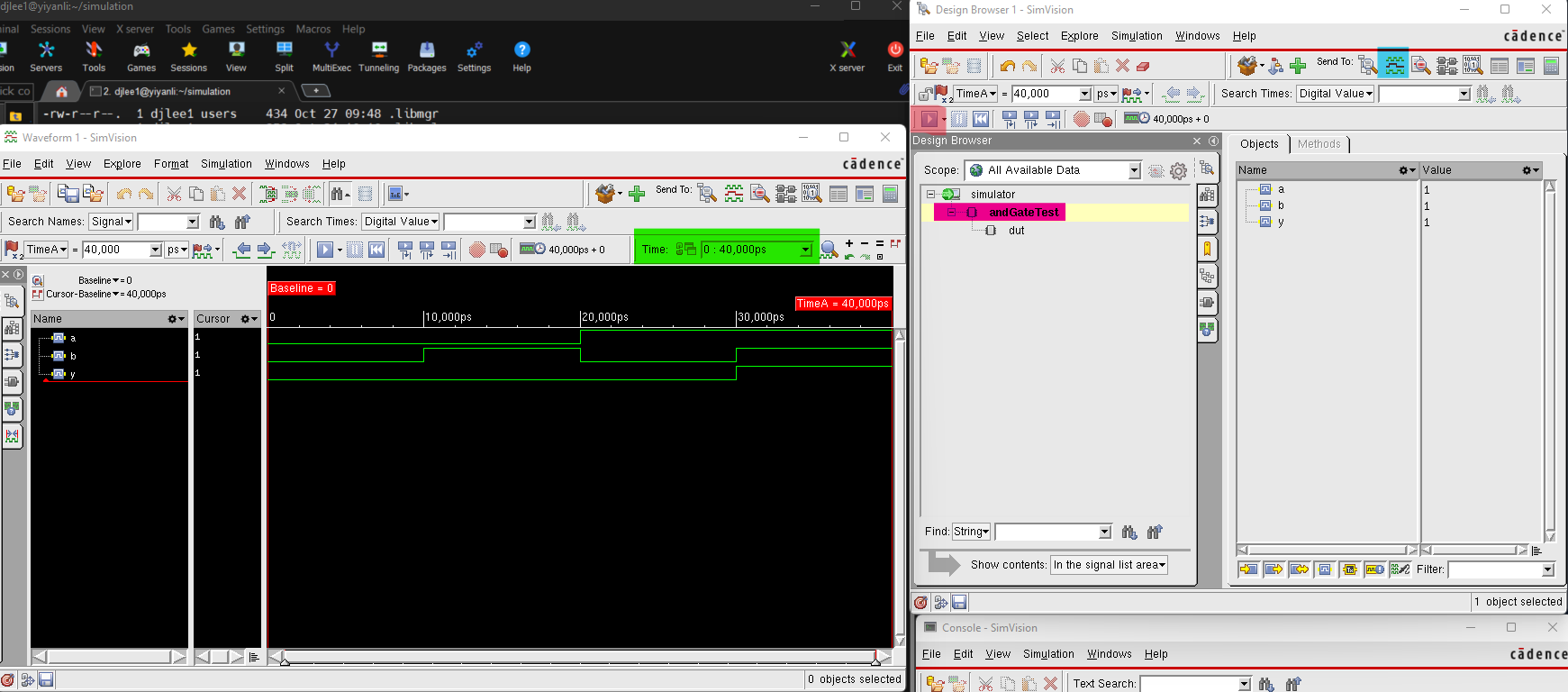

Figure 8: Shows results of the andGate simulation.

Inorder to get the waveform on the right to show up you need to make

sure that andGateTest is selected, highlighted in pink. Once selected

click show Waveform, blue highlighted box. Then a new window will pop

up but it will be blank. Next Click the Run simulation button,

Highlighted light red. Then the wave form will show up and you might

need to adjust the time scale, highlighted in green, to see the

complete simulation.

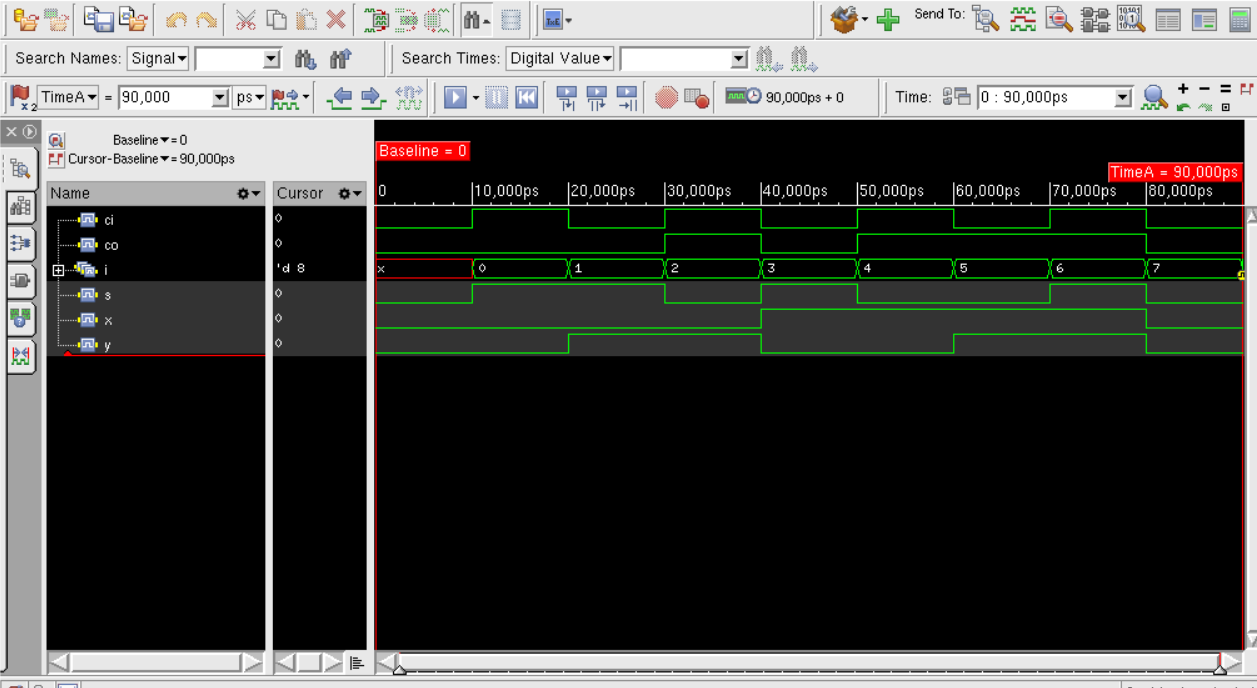

Task 4: Simulate 3 other complex simulations to show you understand

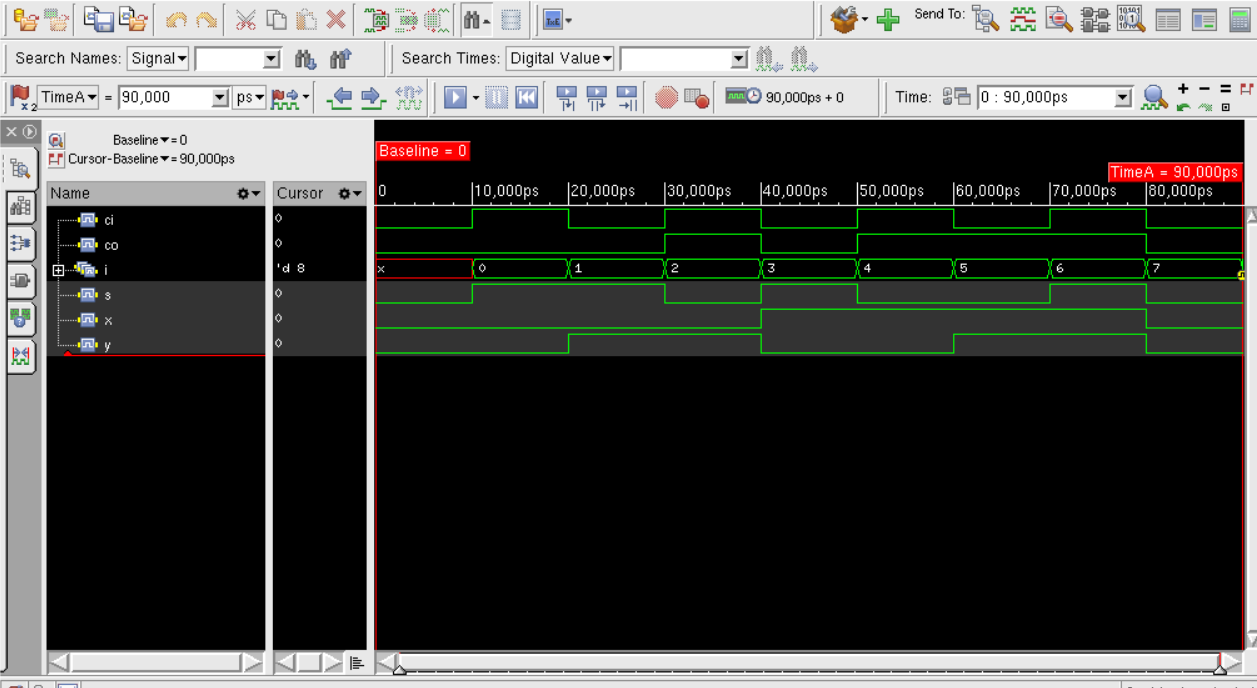

Figure 9: Shows simulation of a four bit comparitor

Figure 10: Shows simulation of an one bit full adder

Figure 11: Shows simulation of three bit parity generator.

Discussion:

After

completeing all the tasks you should be familar with how to use

Xcelium, simvison, to complete logic simulation on the cadence server.