CE 433 Spring 2022

Homework 4

Name: David Lee

Email:

djlee1@fortlewis.edu

Data

Storage

Introduction:

In

this homework assignment we use create simulations to see the functions

of many different storage compents.

Materials and Methods:

vim, Vivado and a FPGA board

Results:

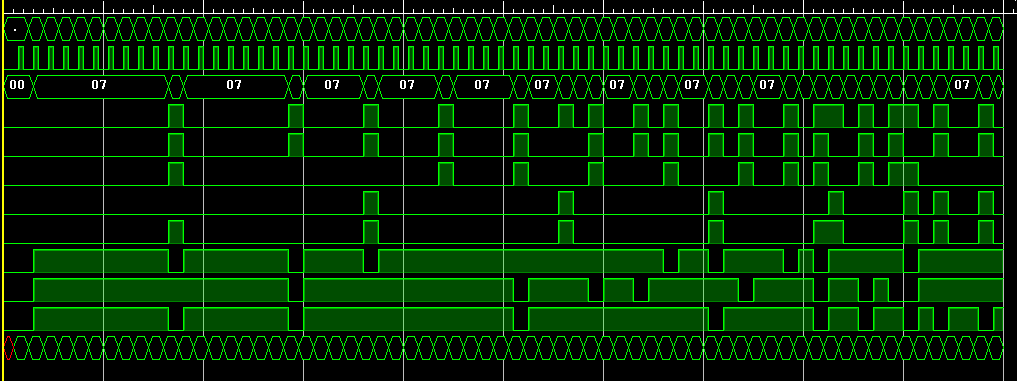

Task 1: Repeat the Simulation in Section 1-3

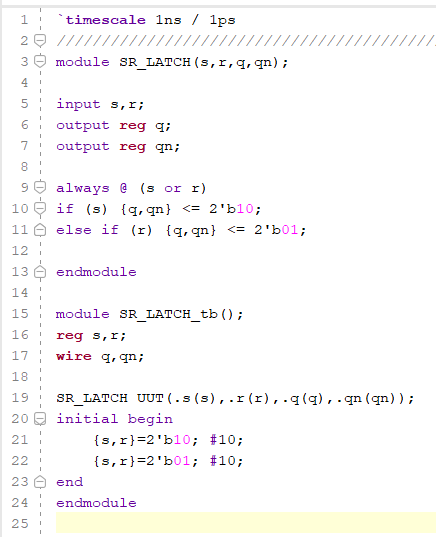

Figure 1: Shows The code

for the SR Latch

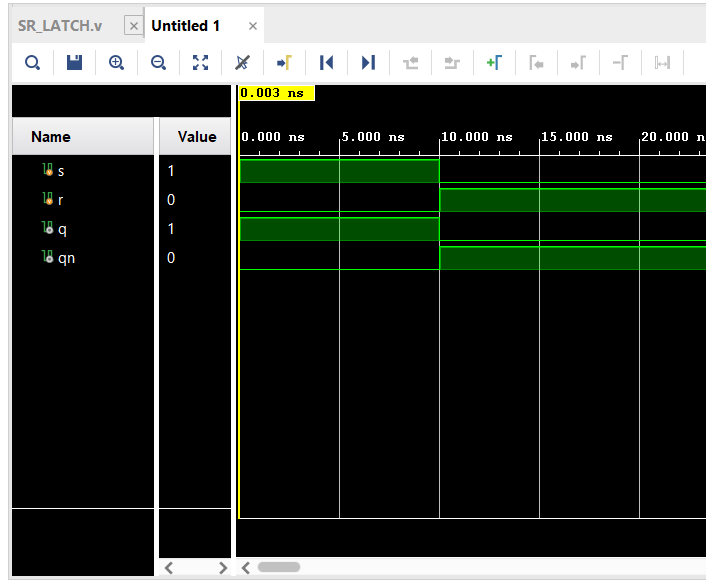

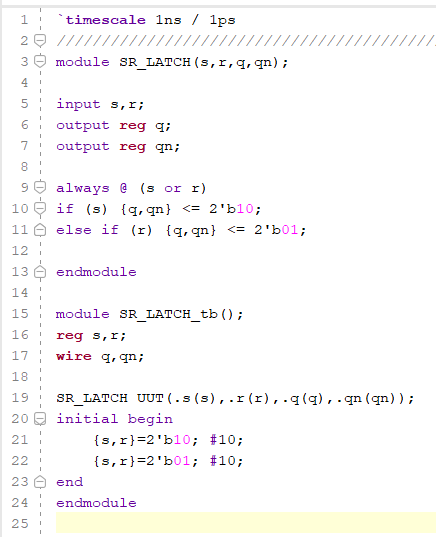

Figure 2: Shows The simulation results of

the SR Latch

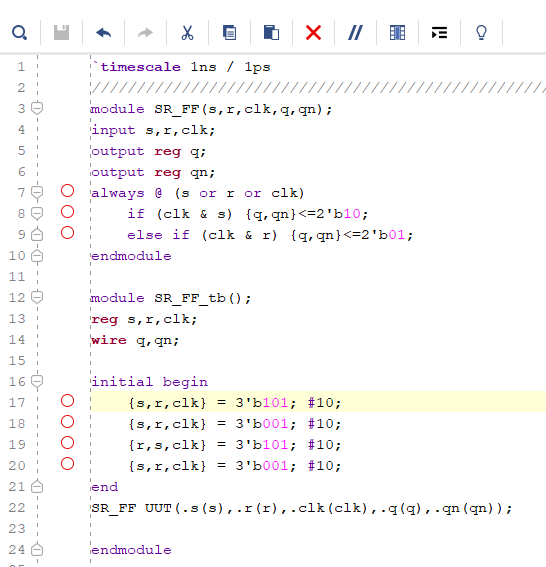

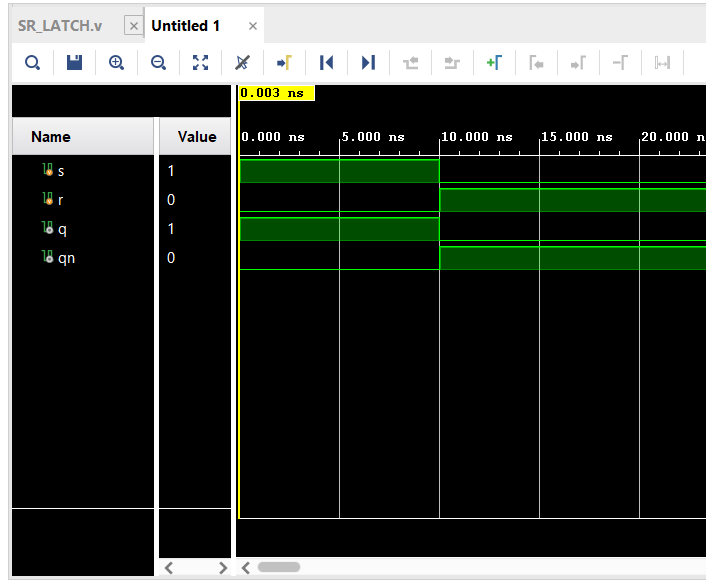

Figure 3: Shows The Code for the SR

Flip Flop

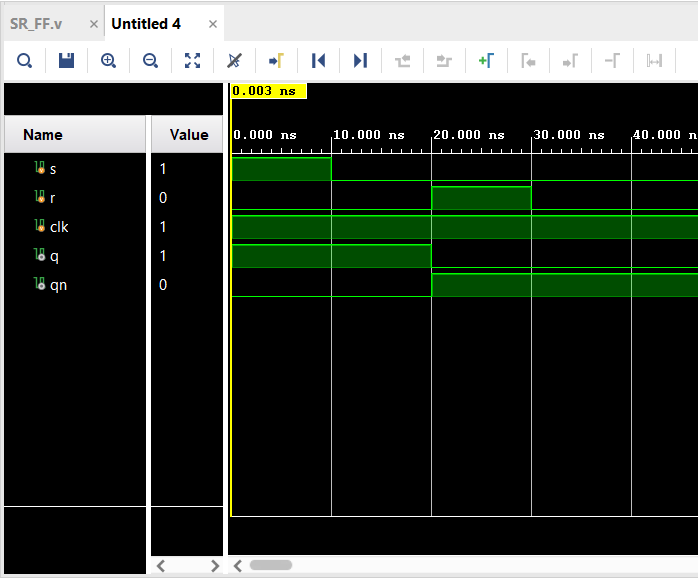

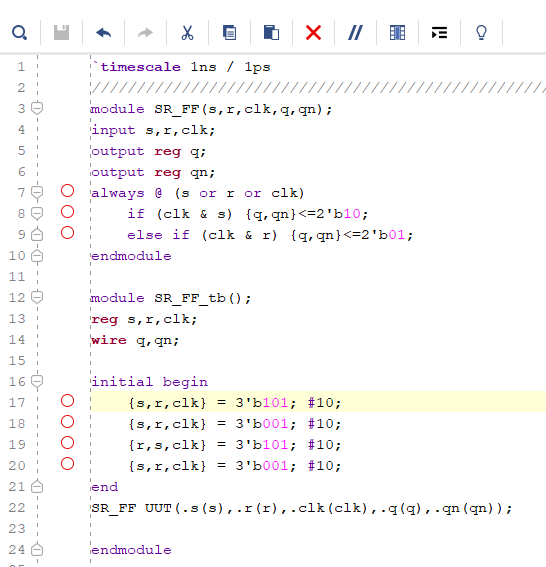

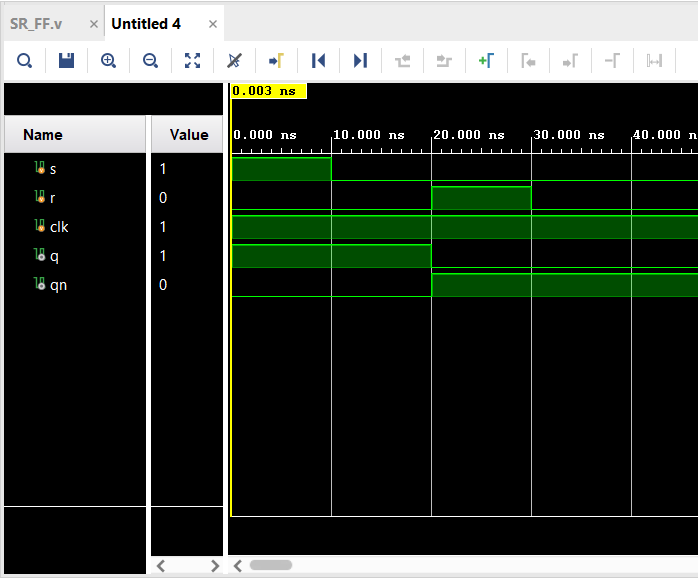

Figure 4: Shows The Simulation of

the SR FF

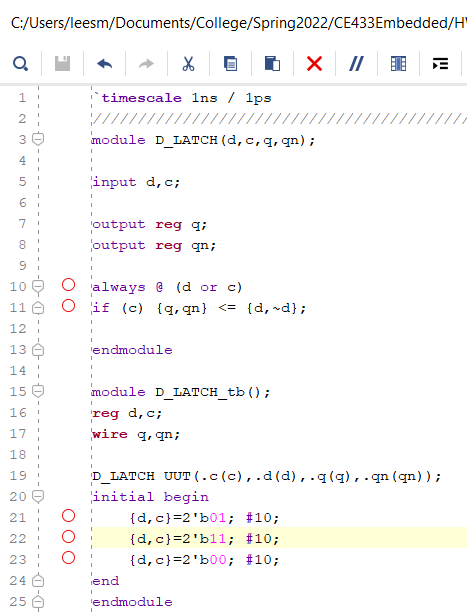

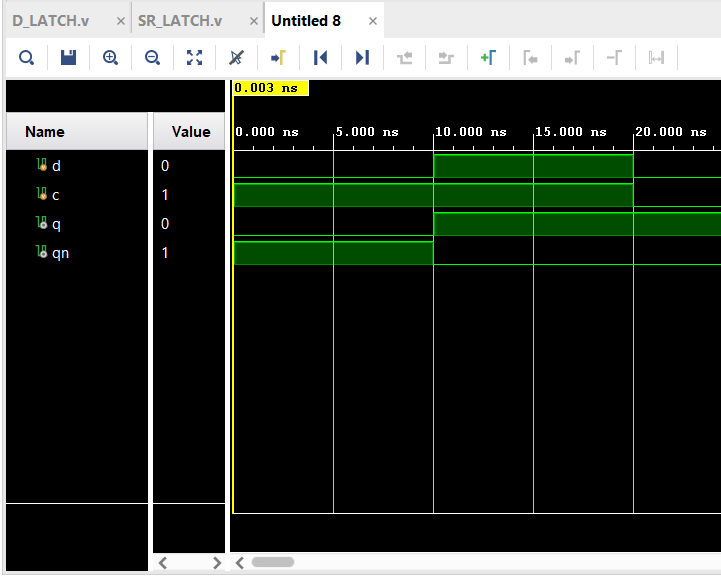

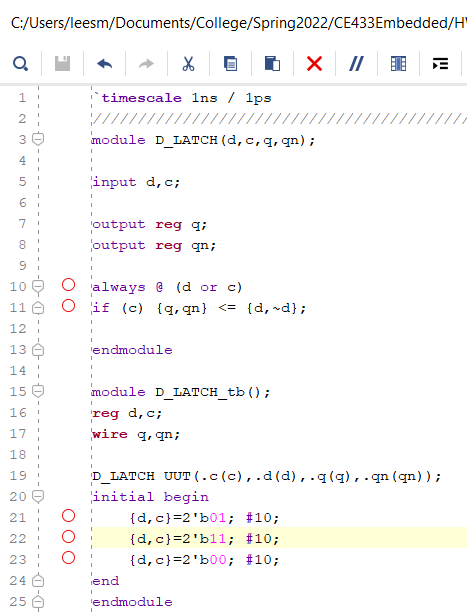

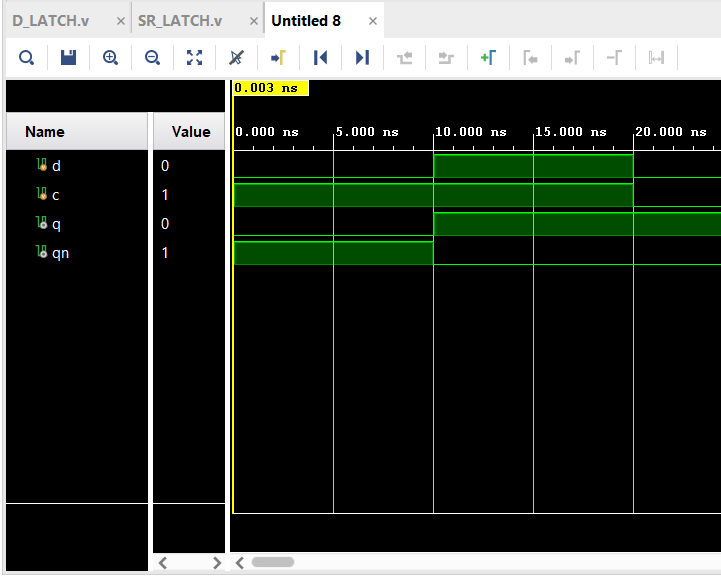

Figure

5: Shows the Code of the D_latch

Figure

6: Shows the

code for the D_latch

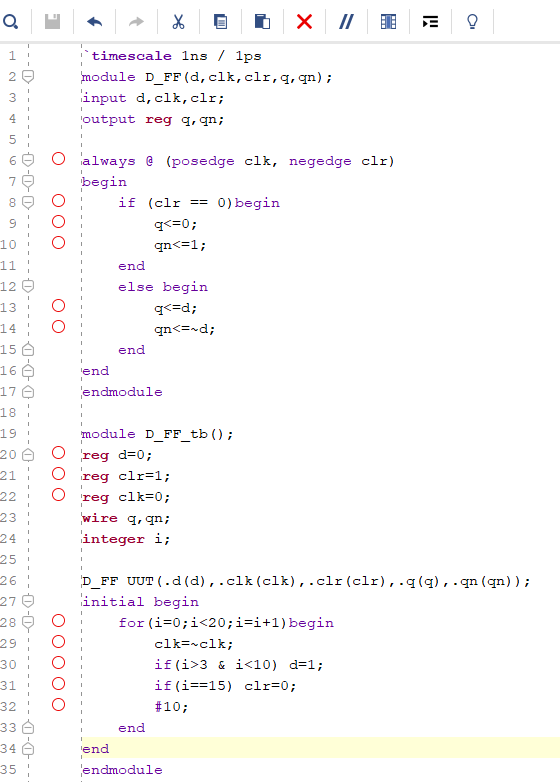

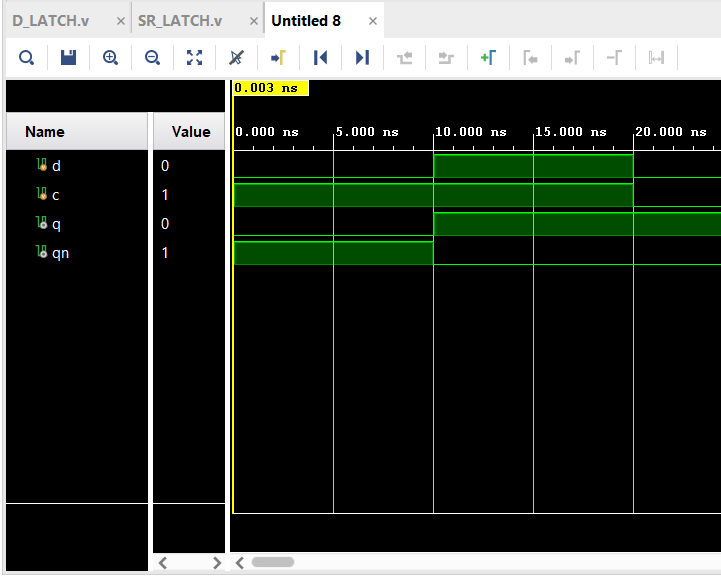

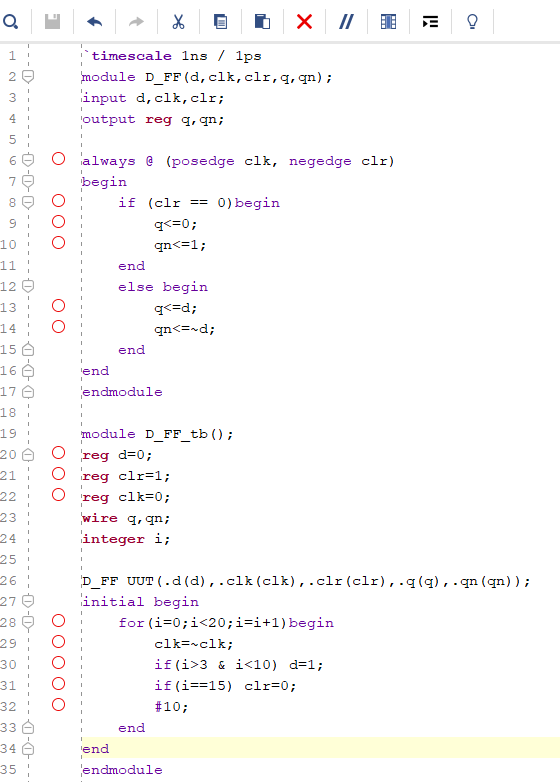

Figure 7: Shows the Code of the

D_Flip FLop

Figure 8: Shows the Simulation of

the D Flip Flop

Task 2: Write the Test

Bench and Run Simulations for Section 4 and Section 5

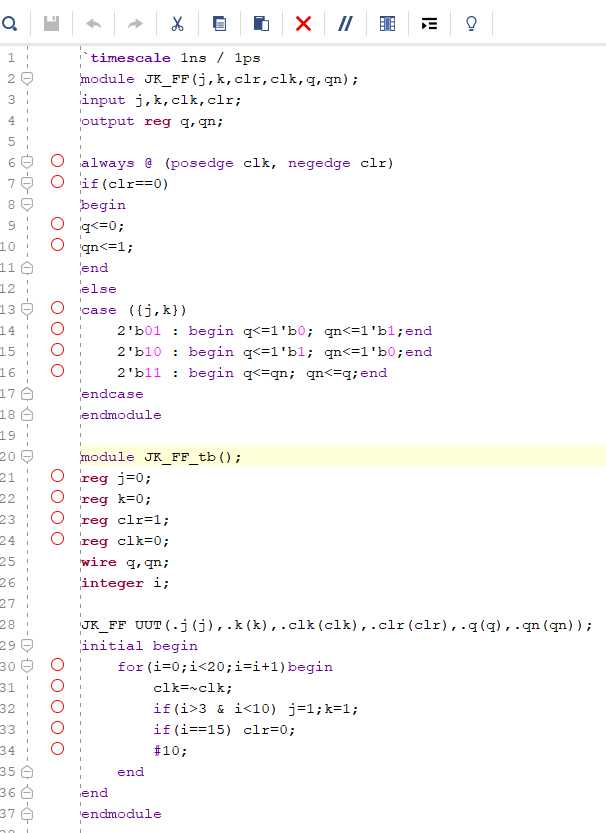

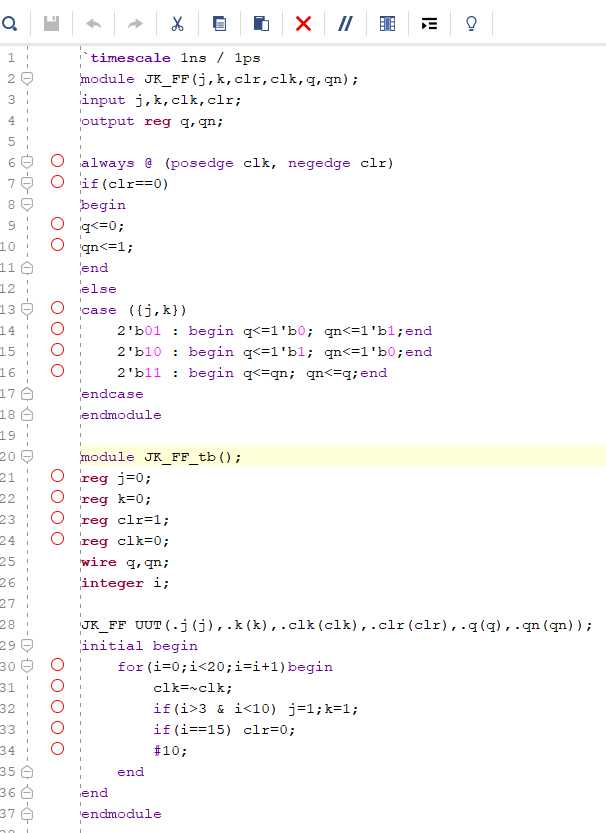

Figure 9: Shows

the Code of the JK Flip Flop

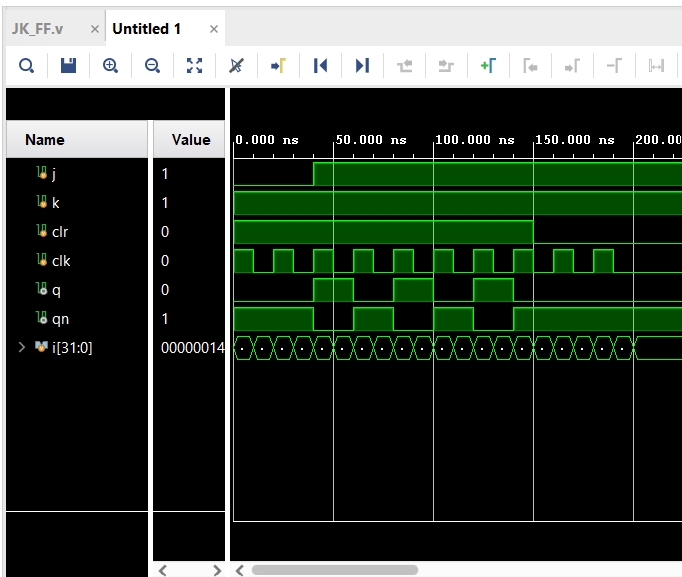

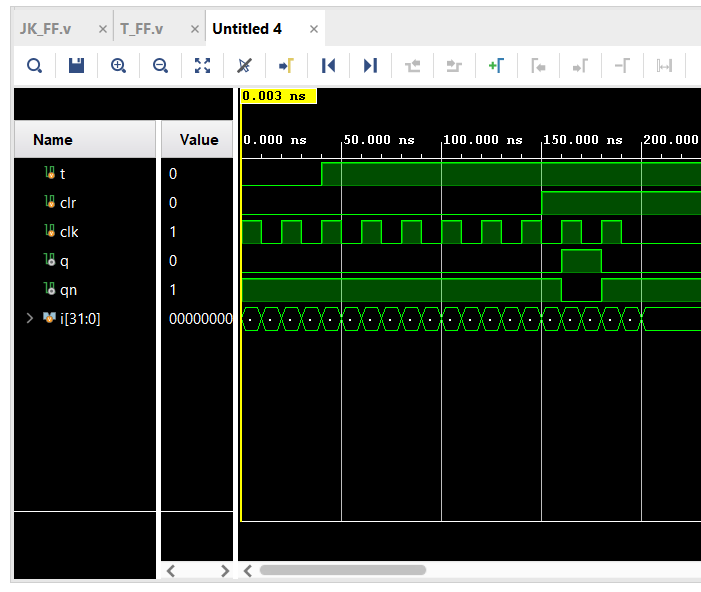

Figure 10: Shows the

Simulation Results for the JK Flip Flop

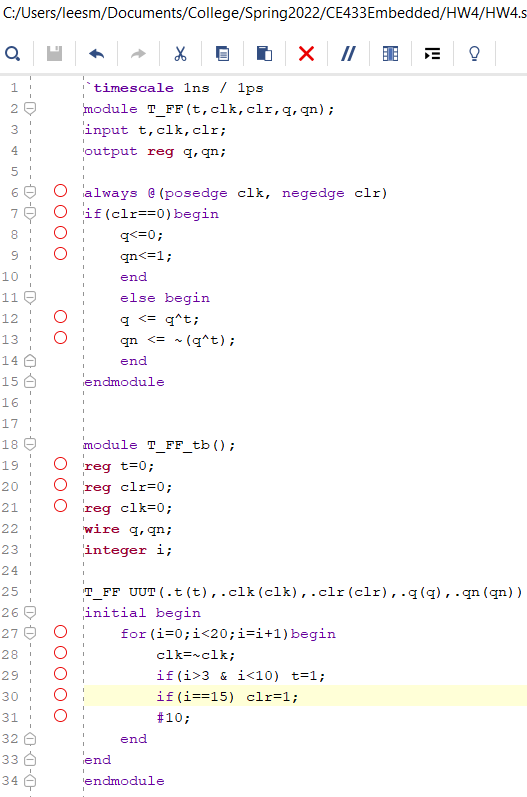

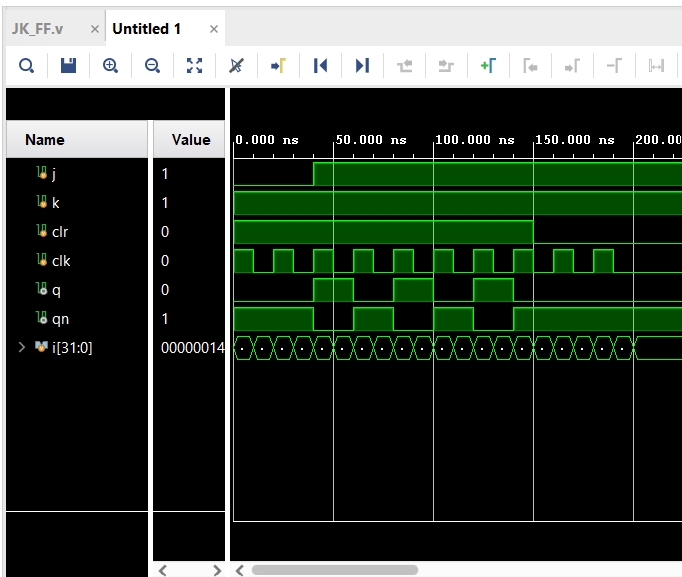

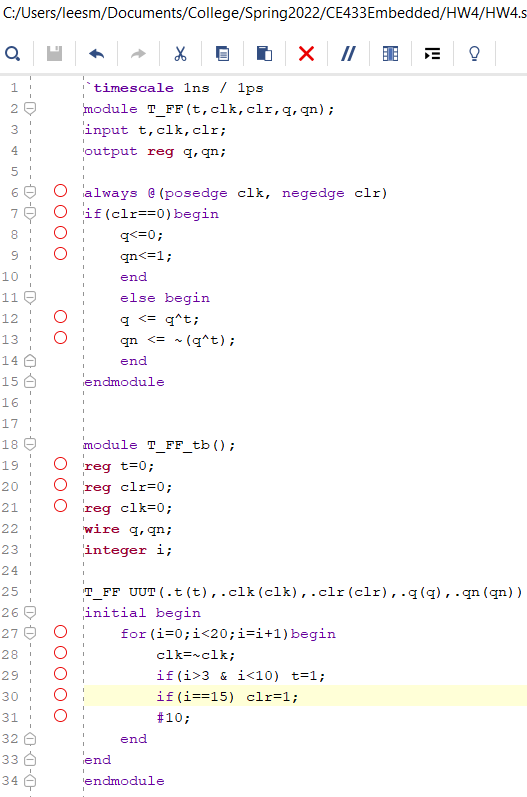

Figure 11: Shows

the code for the T Flip Flop

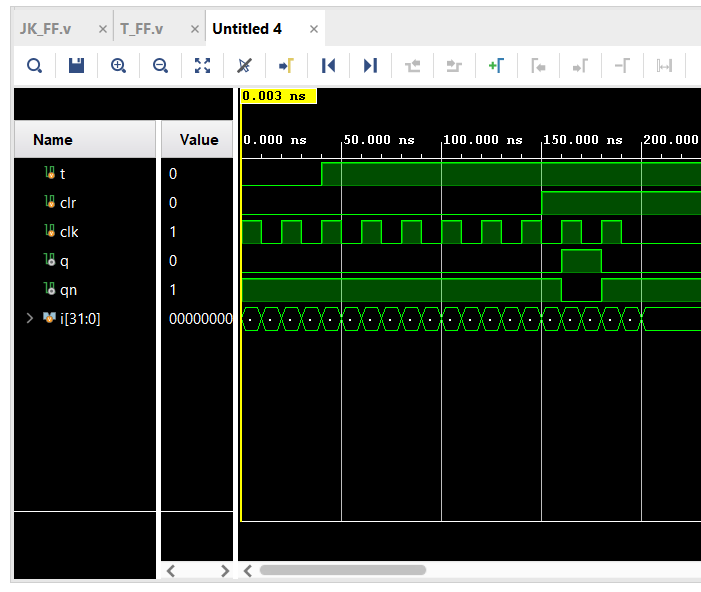

Figure 12: Shows the Simulation of

the T Flip Flop

Task 3: Repeat

All work in section 8

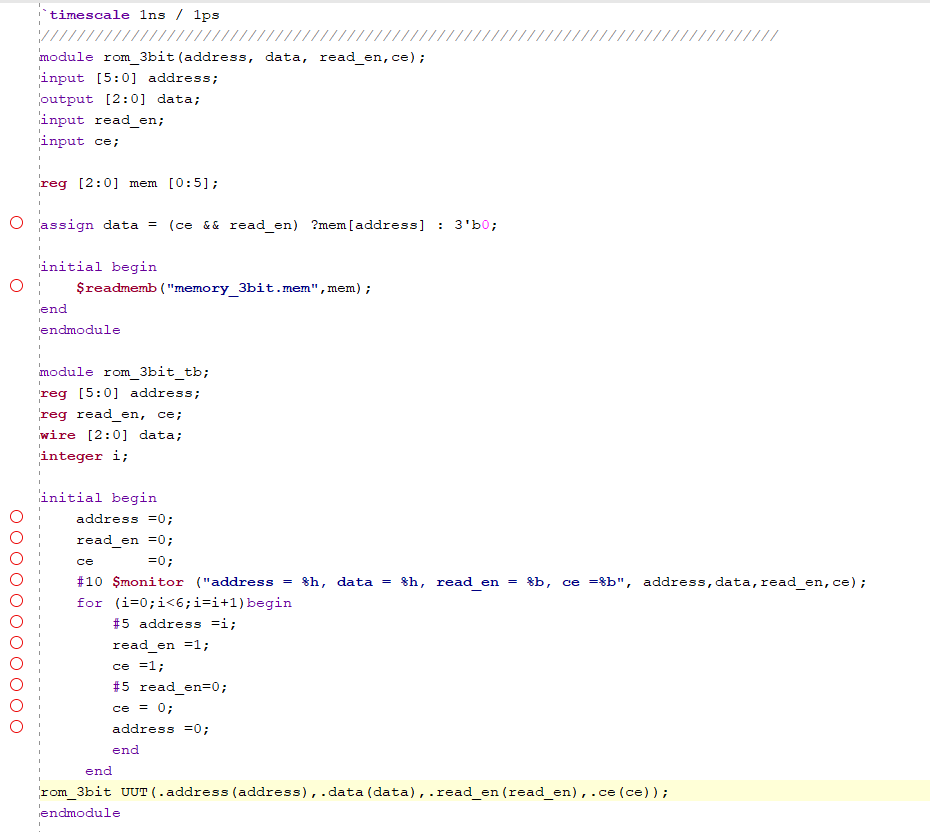

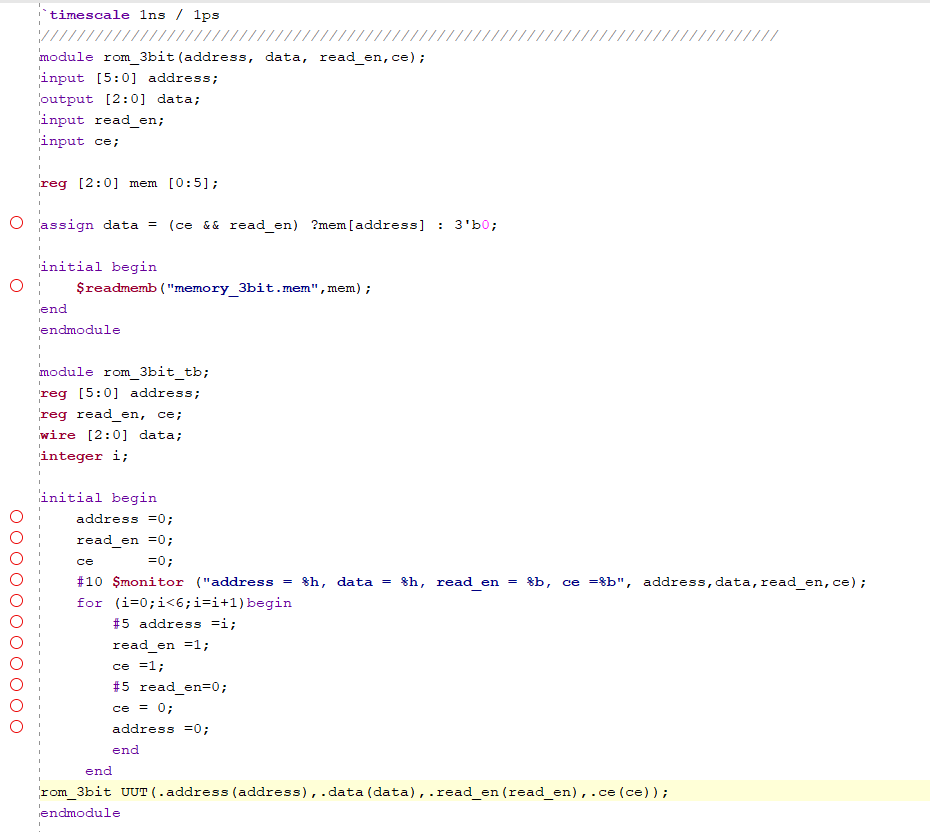

Figure 13: Shows

the Code for Reading 3bit Binary

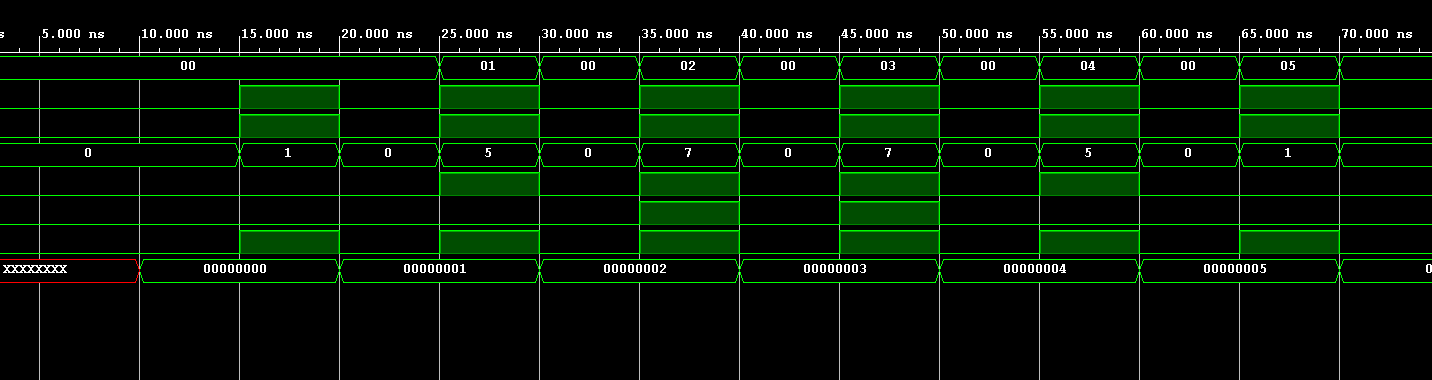

Figure 14: Shows the

Simulation for the reading the 3Bit Binary

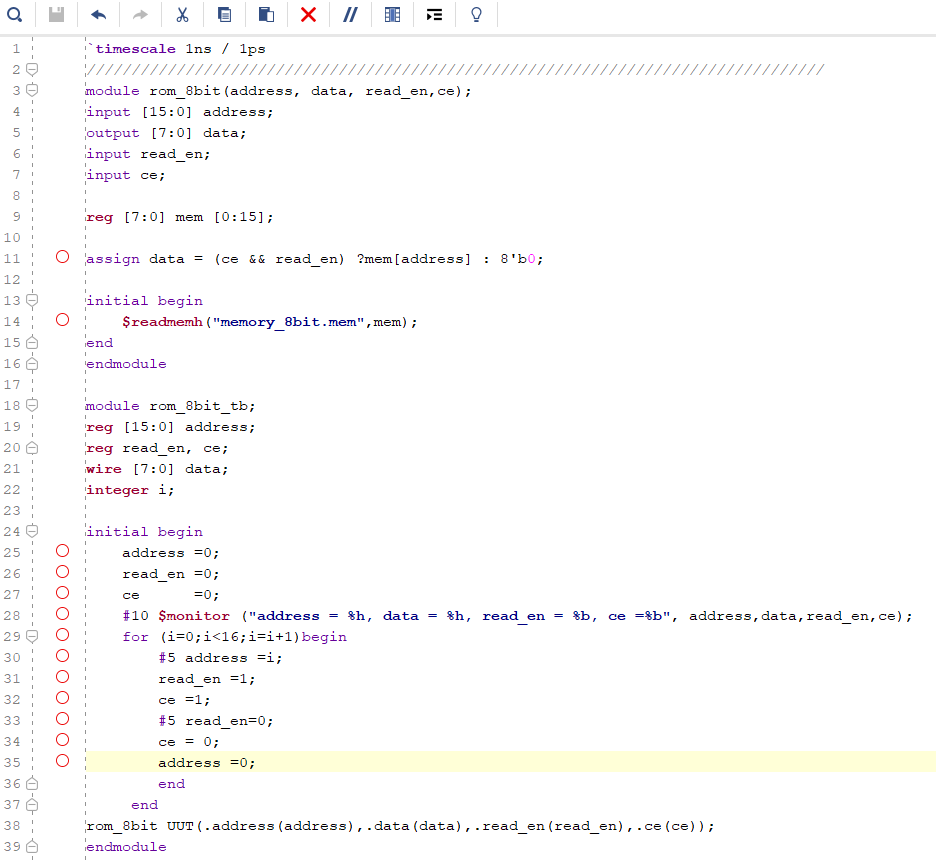

Figure 15: Shows

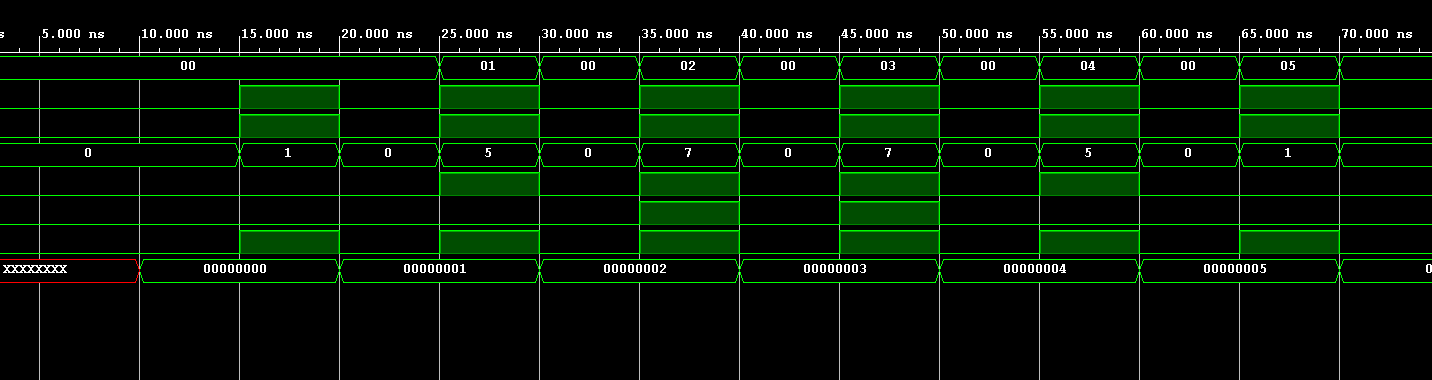

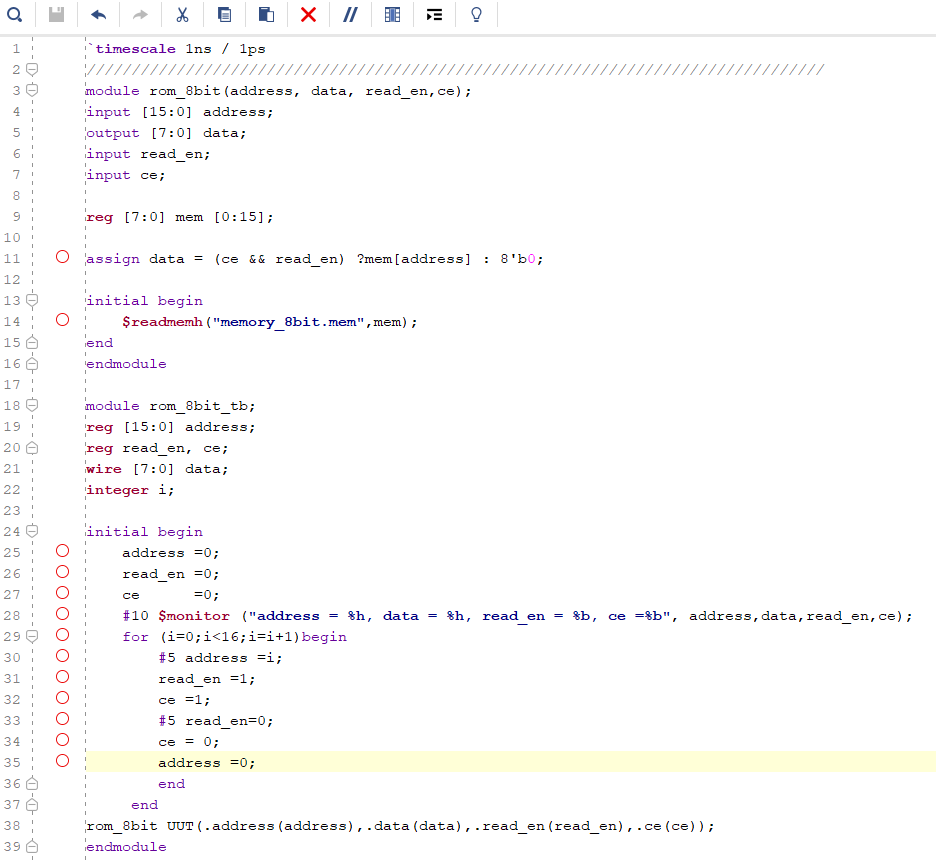

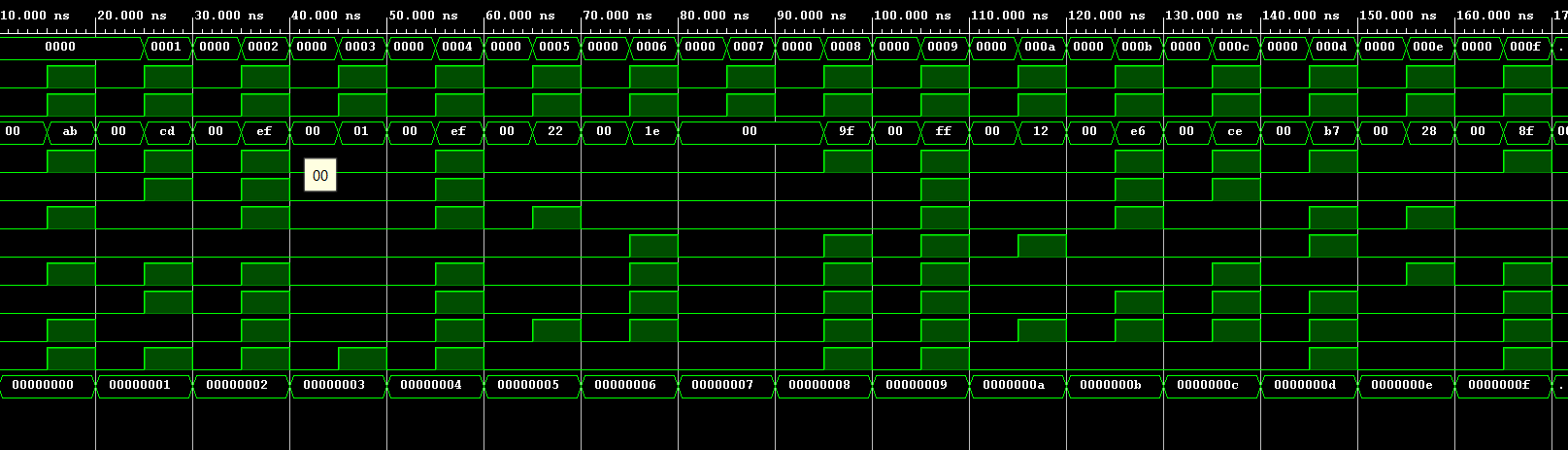

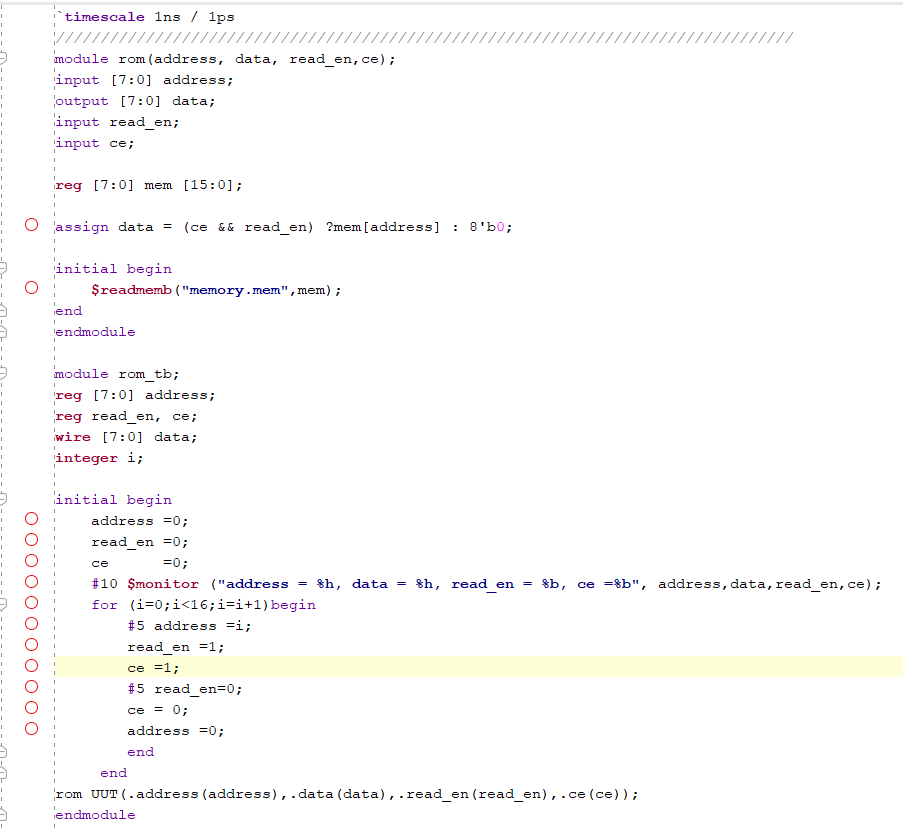

the Code of the 8bit HEX Memory

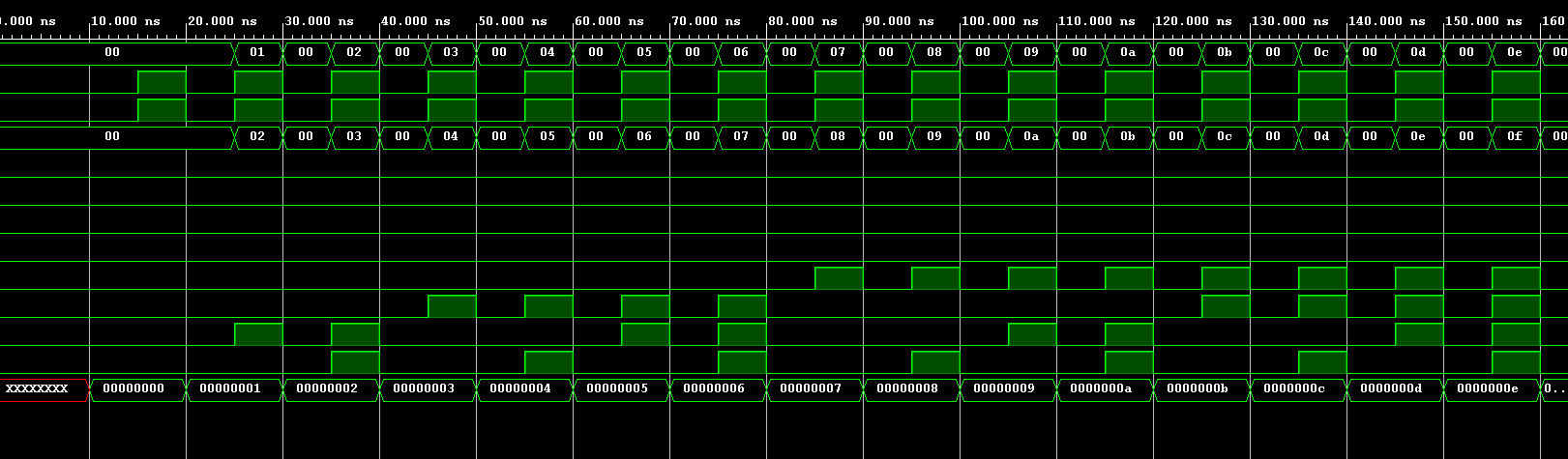

Figure 16: Shows the Simulation of

the 8Bit HEX

Figure 17: Shows

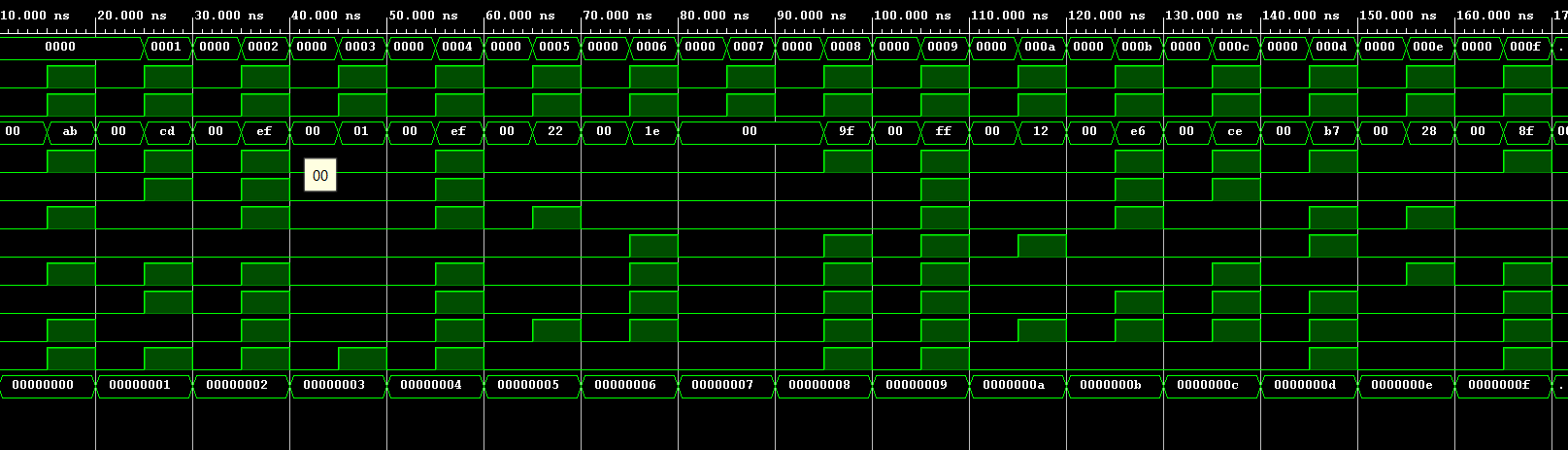

the Code of the 8Bit Binary

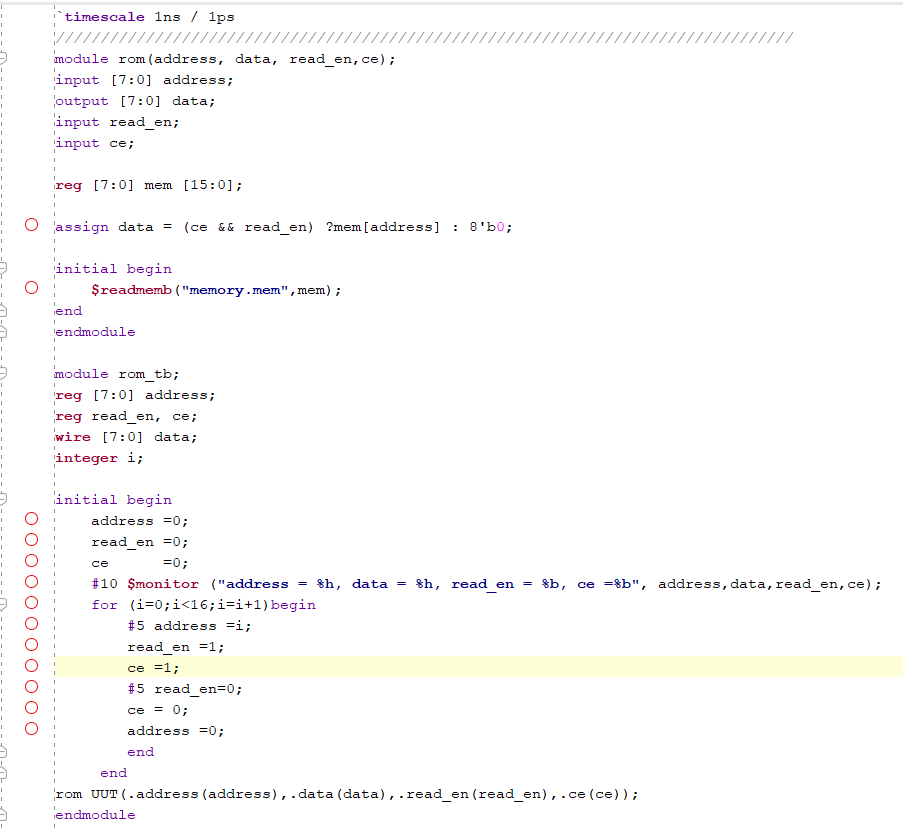

Figure 18: Shows the Simulation of

the 8bit Binary

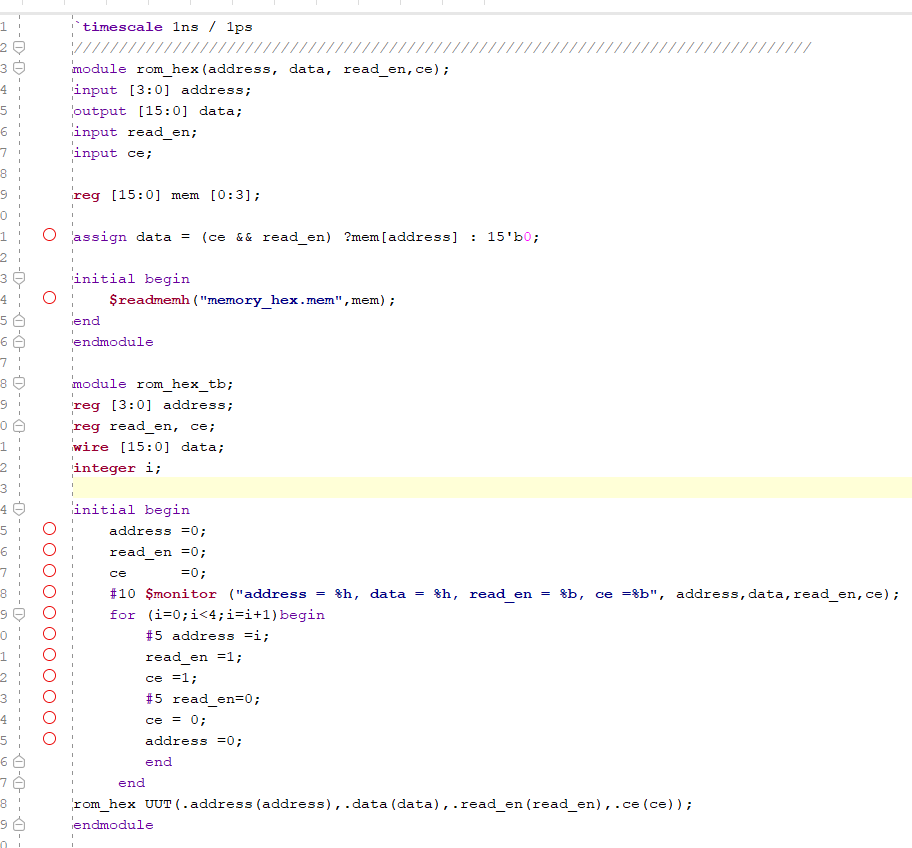

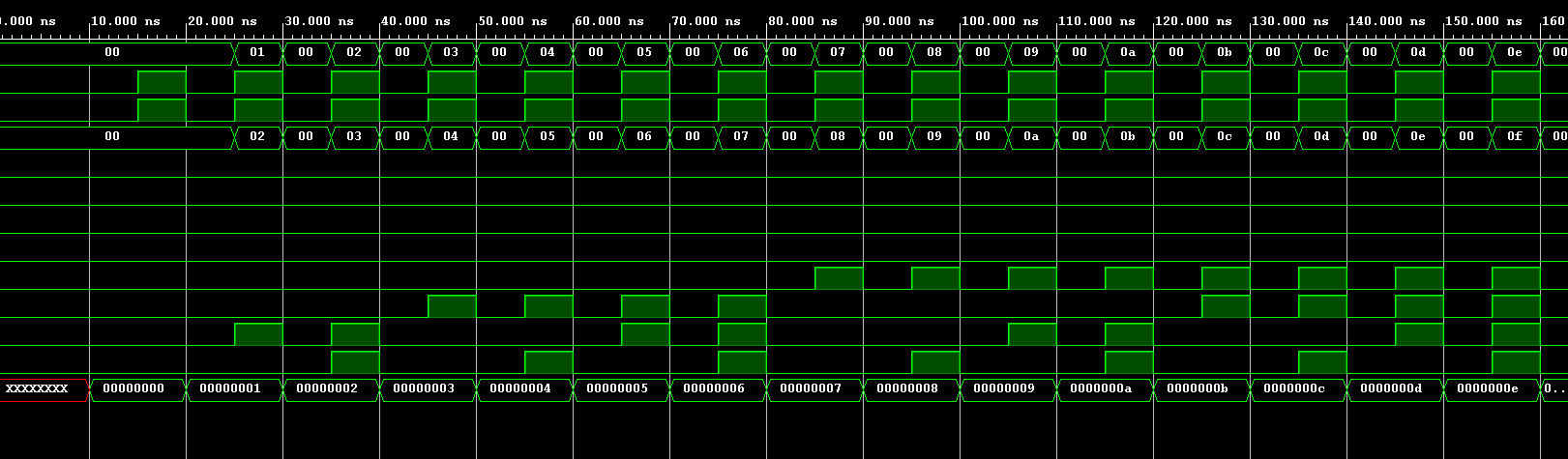

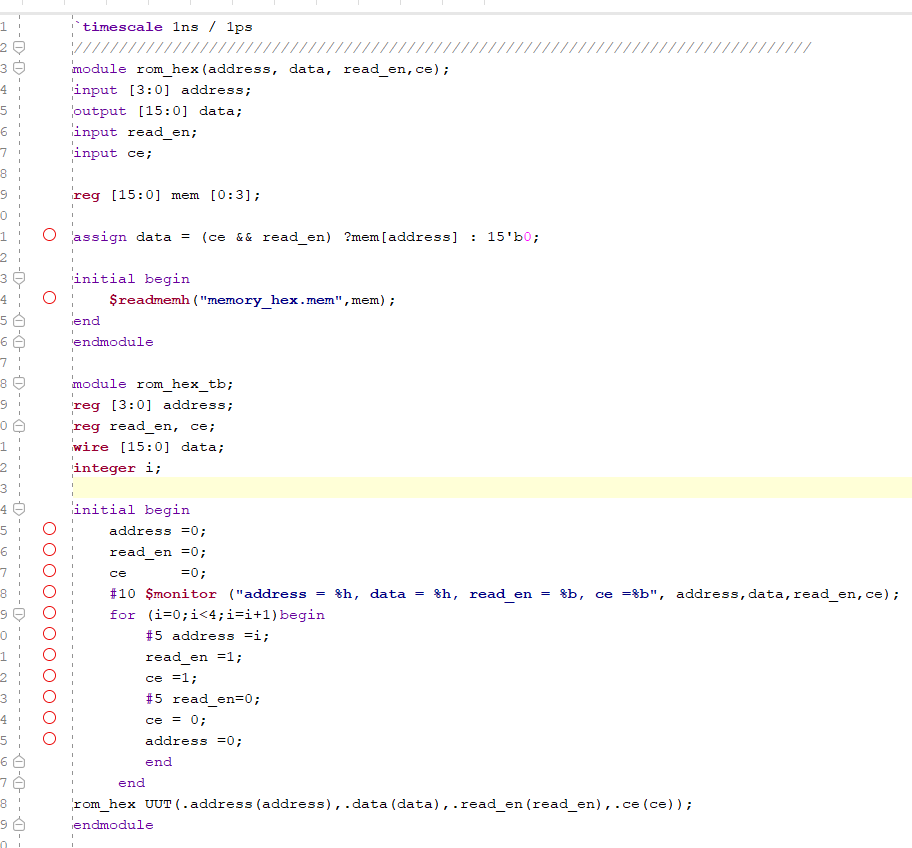

Figure 19: Shows

the Code for the HEX Input

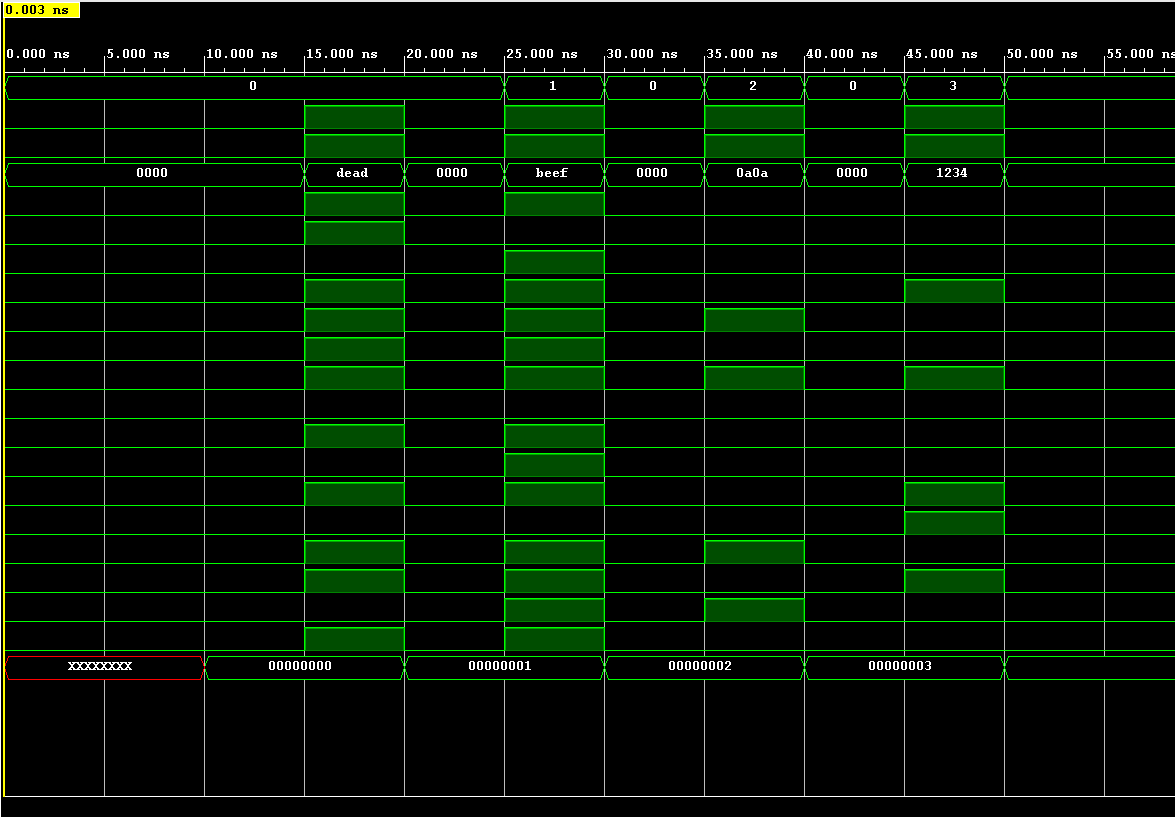

Figure 20: Shows

the Simulation of the HEX

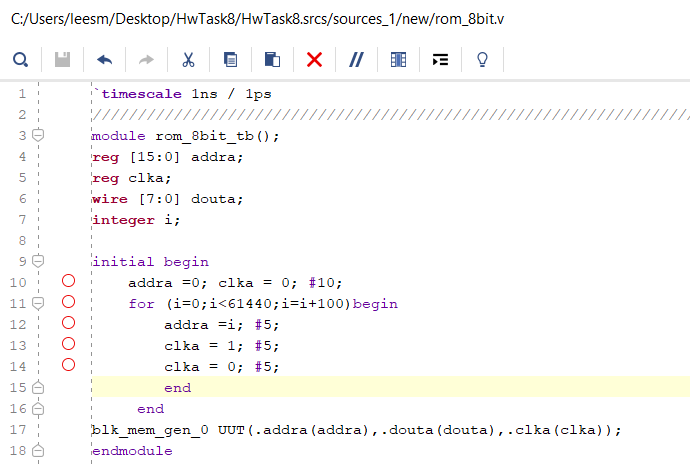

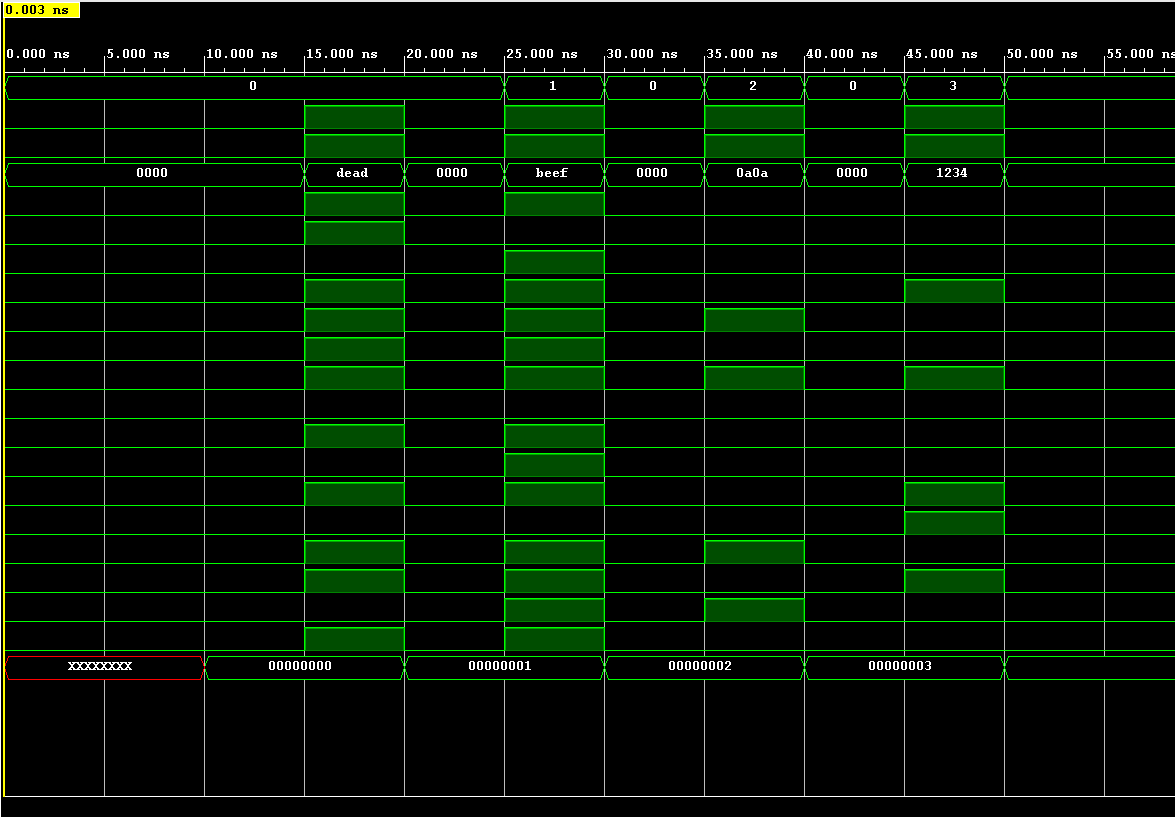

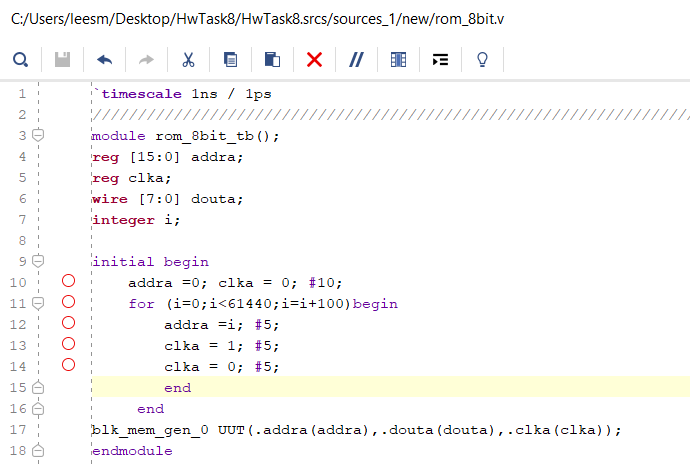

Figure 20: Shows

the Code used for the last part of task 3 Using the IP in Vivado using

ROM

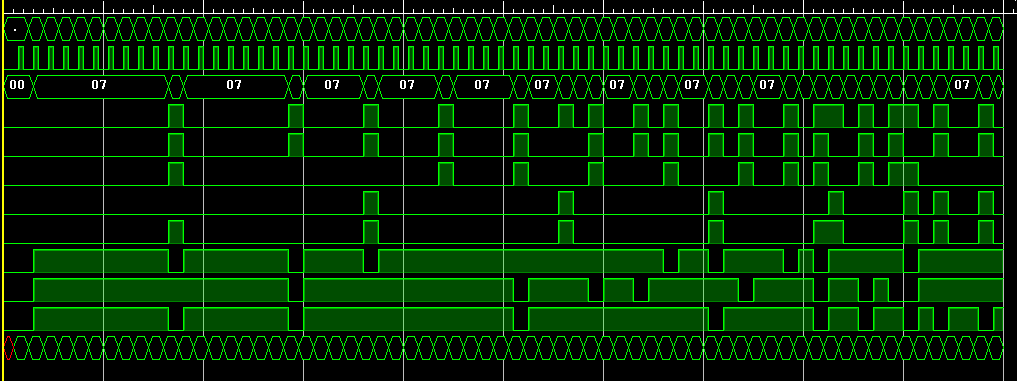

Figure 21: Shows the

Simulation of the IP ROM.

Discussion:

This was assignment was straight

forward for the All the tasks execpt for the last part of task three. I

had a hard time getting the understanding of what the IP core was doing

within the program. Once this was explained to me I was able to get a

better Idea on what to do for the remainder of the task. Then once I

felt like I got it My simulation results looked incorrect because

everything was the same on the output. This was because the address' in

the file were all the same for most of the file. That is why I

incremented by 100 each iteration because of the limited simulation run

time in vivado. This allowed me to have an output that is able to

produce a varitey of results.