CE 433 Spring 2022

Homework 2

Name: David Lee

Email:

djlee1@fortlewis.edu

Data Types, Operators, Combinational Logic

Introduction:

In

this homework assignment we reviewed number systems, number conversions

and got fimilar with the way verilog interacts with an FPGA

Materials and Methods:

vim, Vivado and a FPGA board

Results:

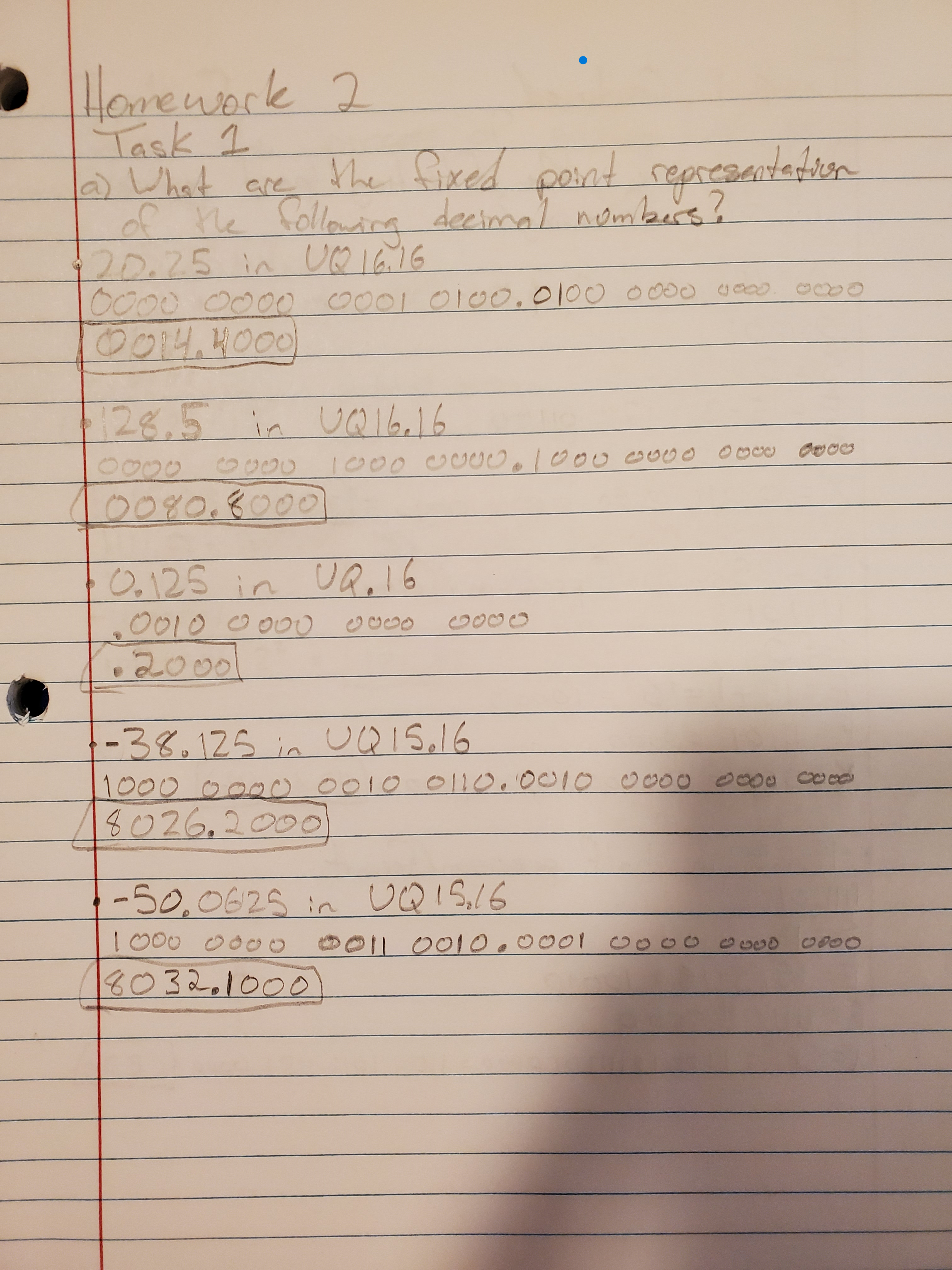

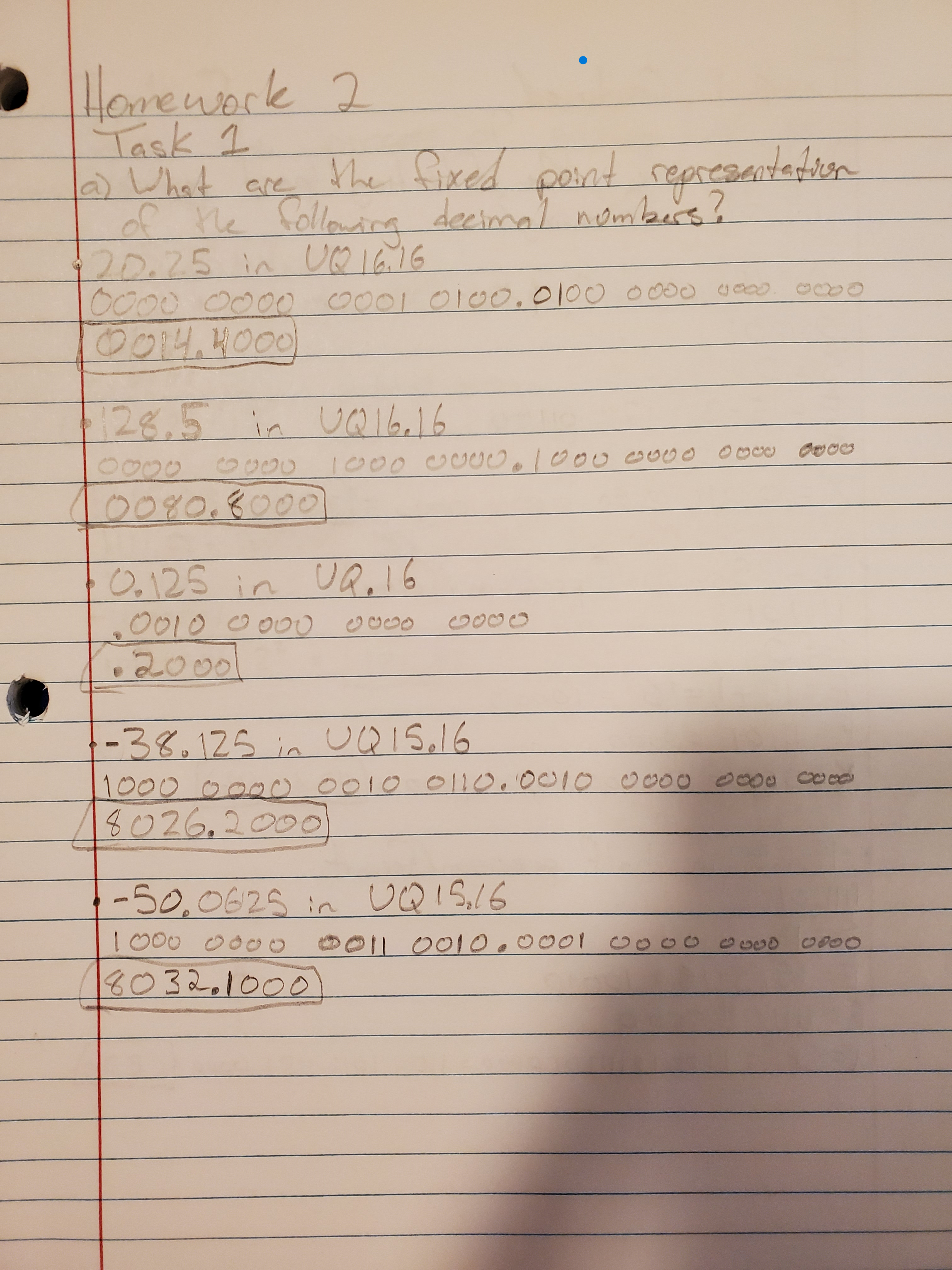

Task 1: Work the Following Problems

Figure 1: Shows Part A of Task 1 worked Problems

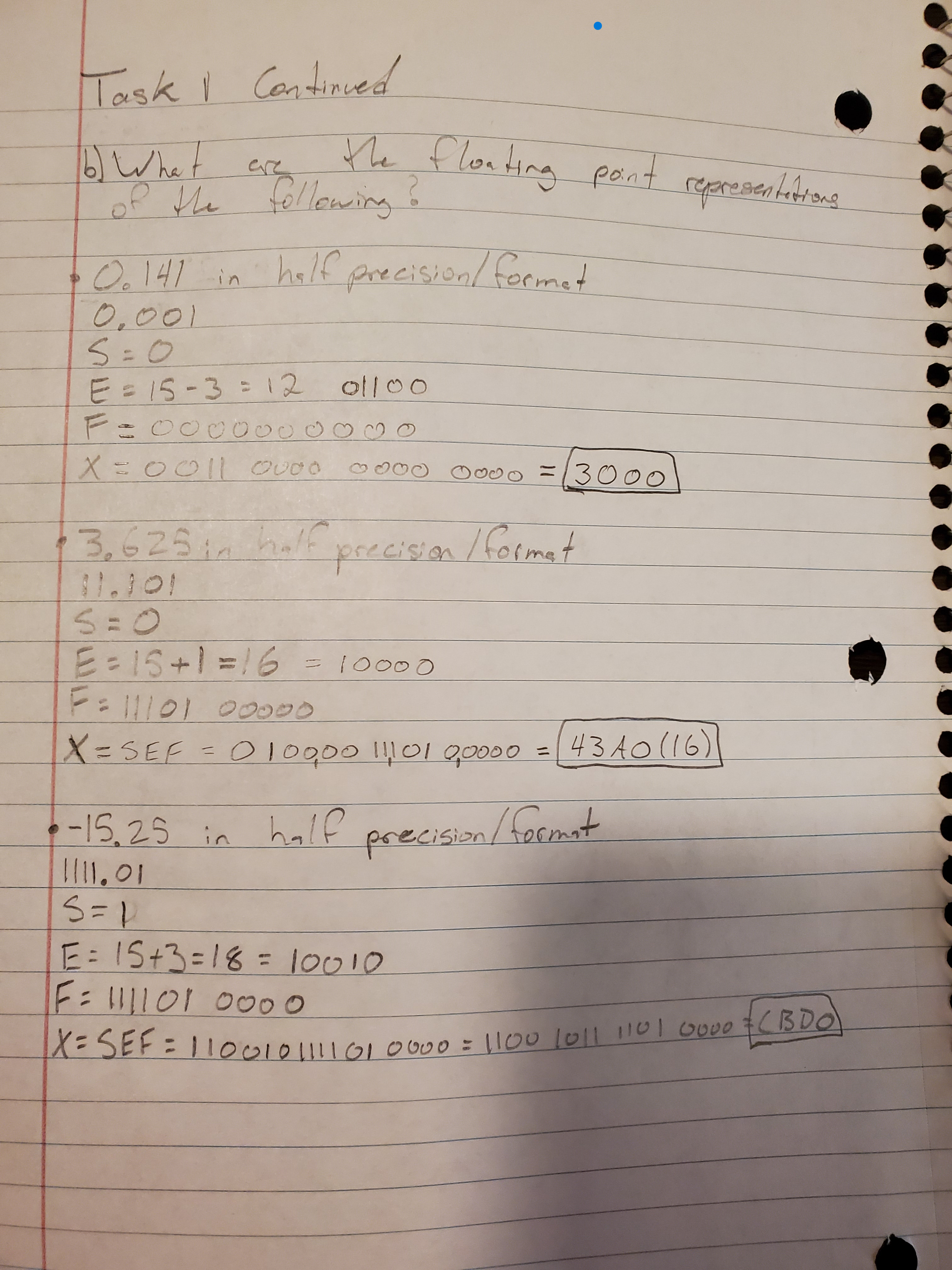

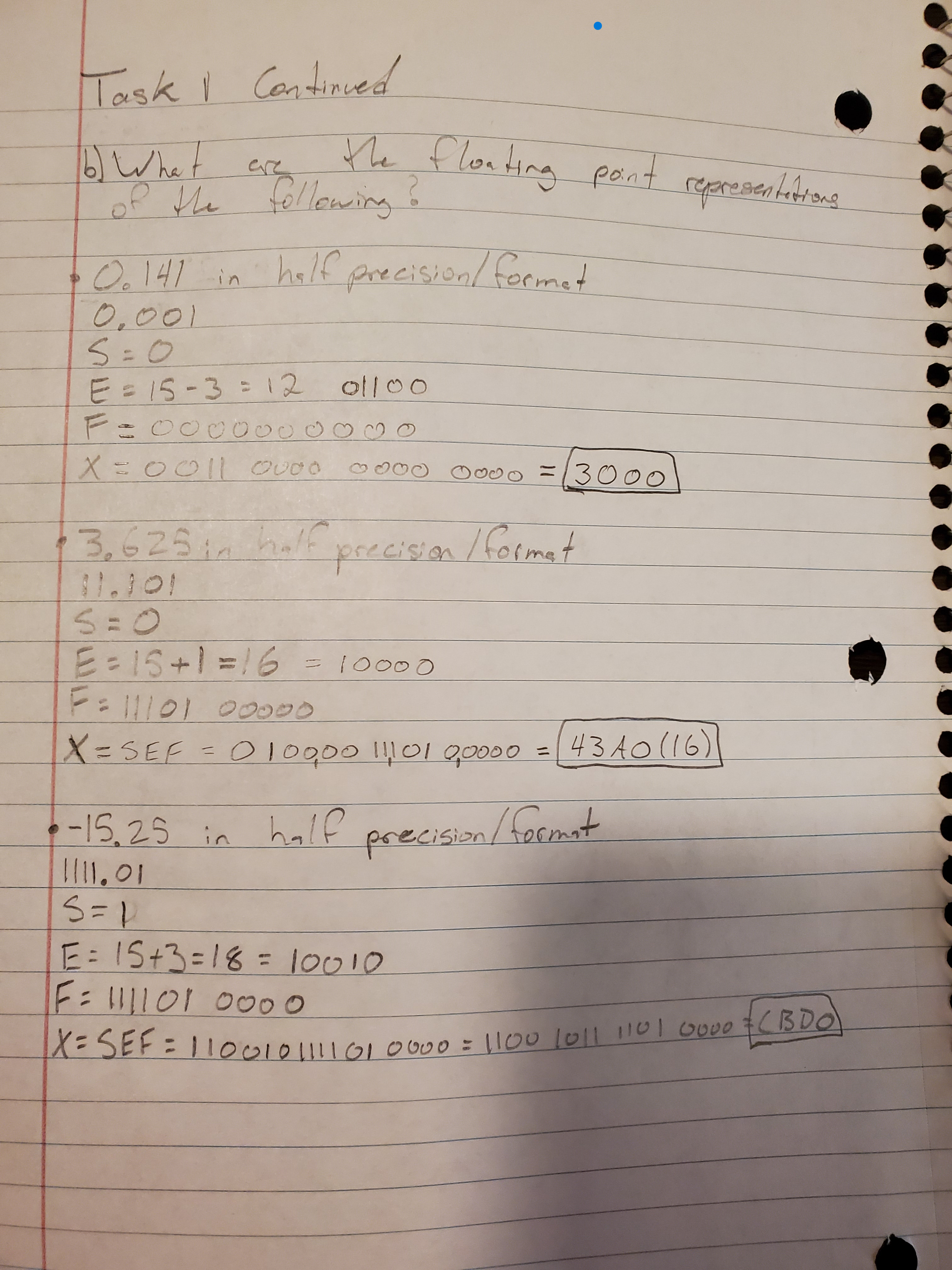

Figure 2: Shows Part B of Task 1 worked Problems

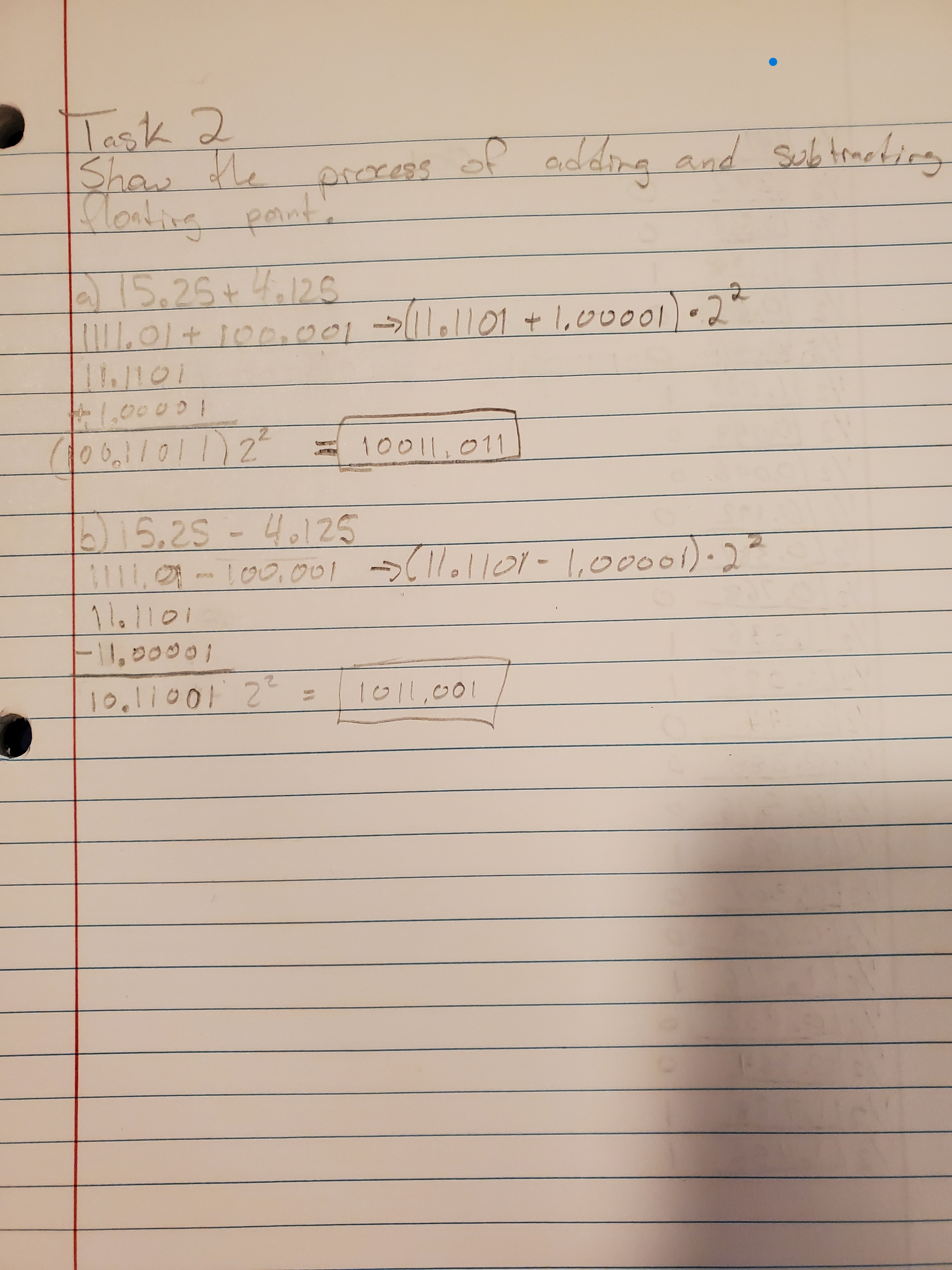

Task 2: Show the Process of floating point addition and subtraction of the following operations

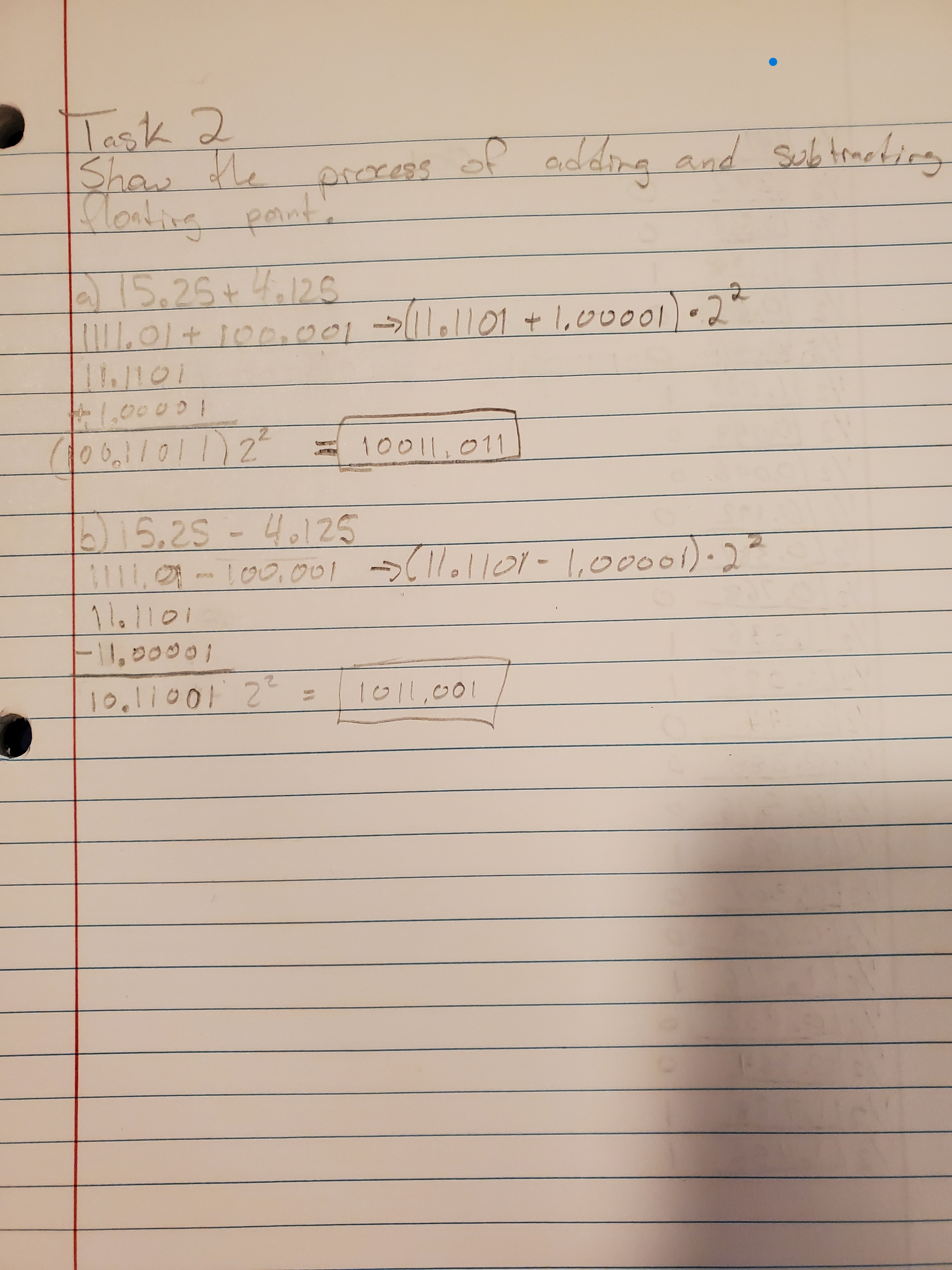

Figure 3: Shows the worked Problems of Task 2

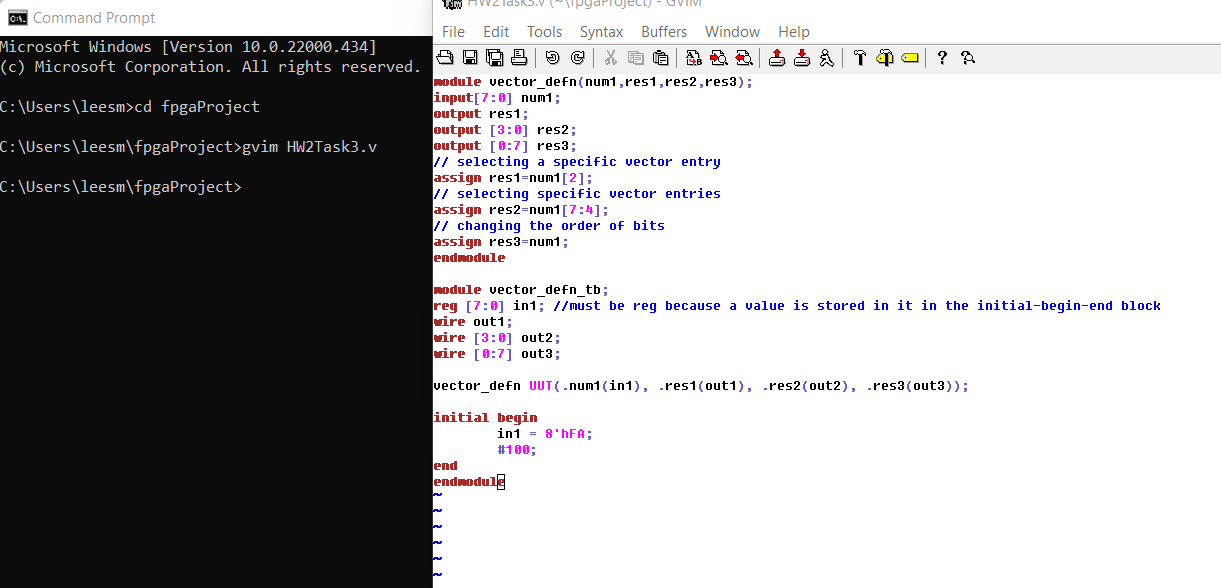

Task 3:

Repeat the simulation work in section 11

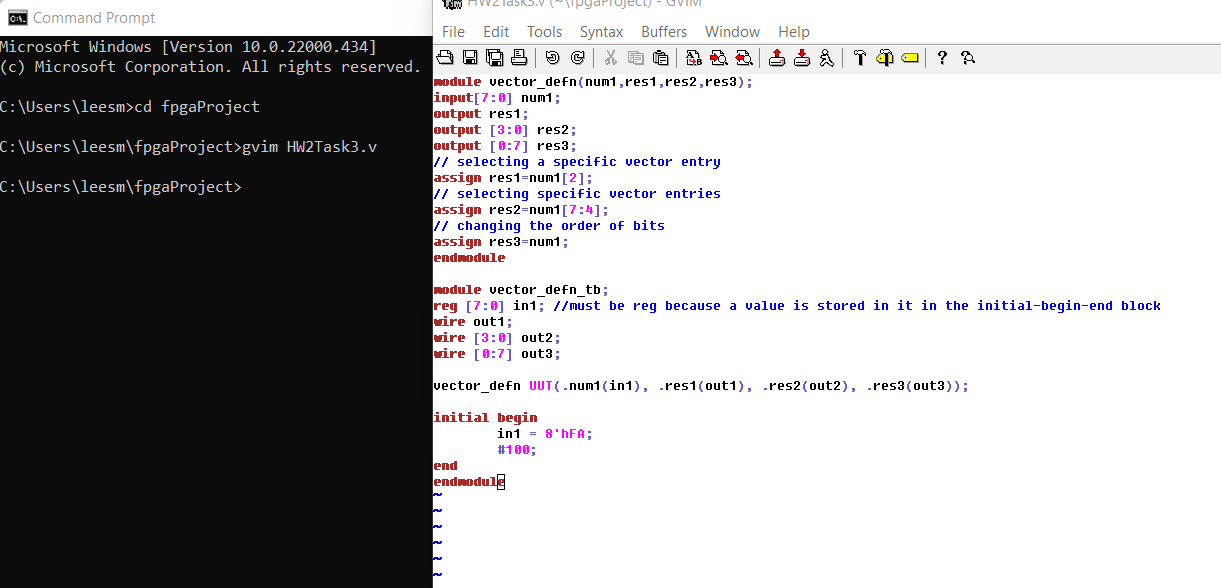

Figure 4: Shows the

Verilog code Used in the Task

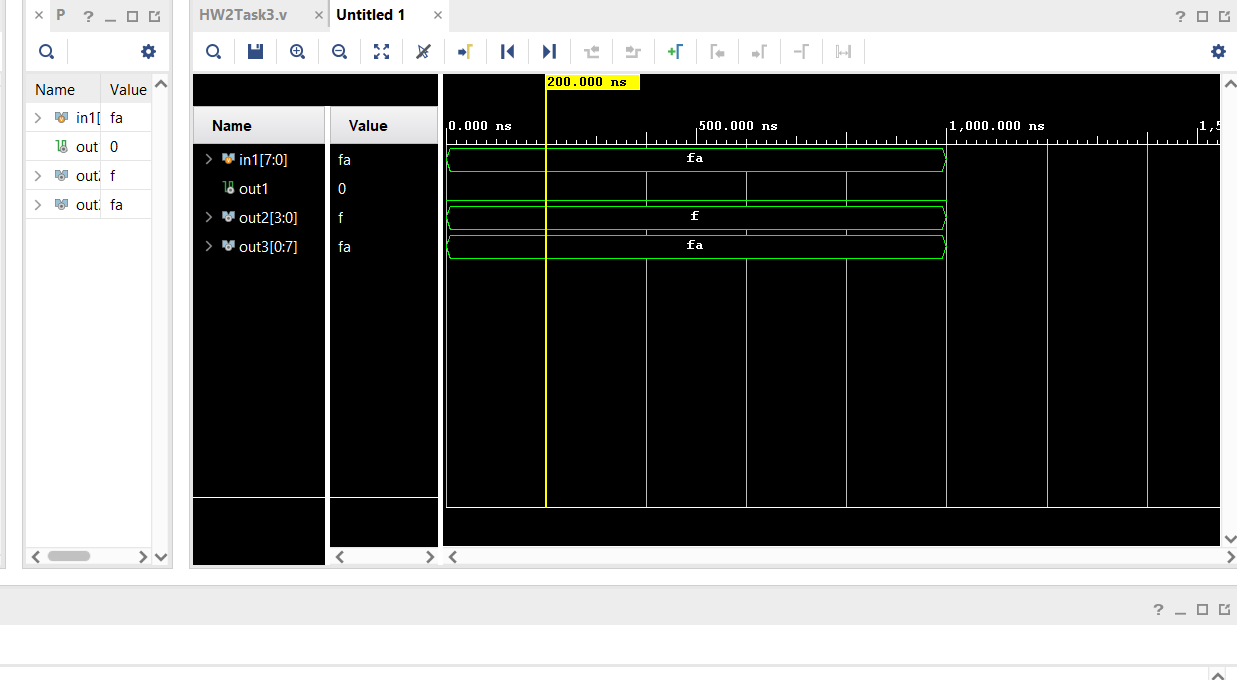

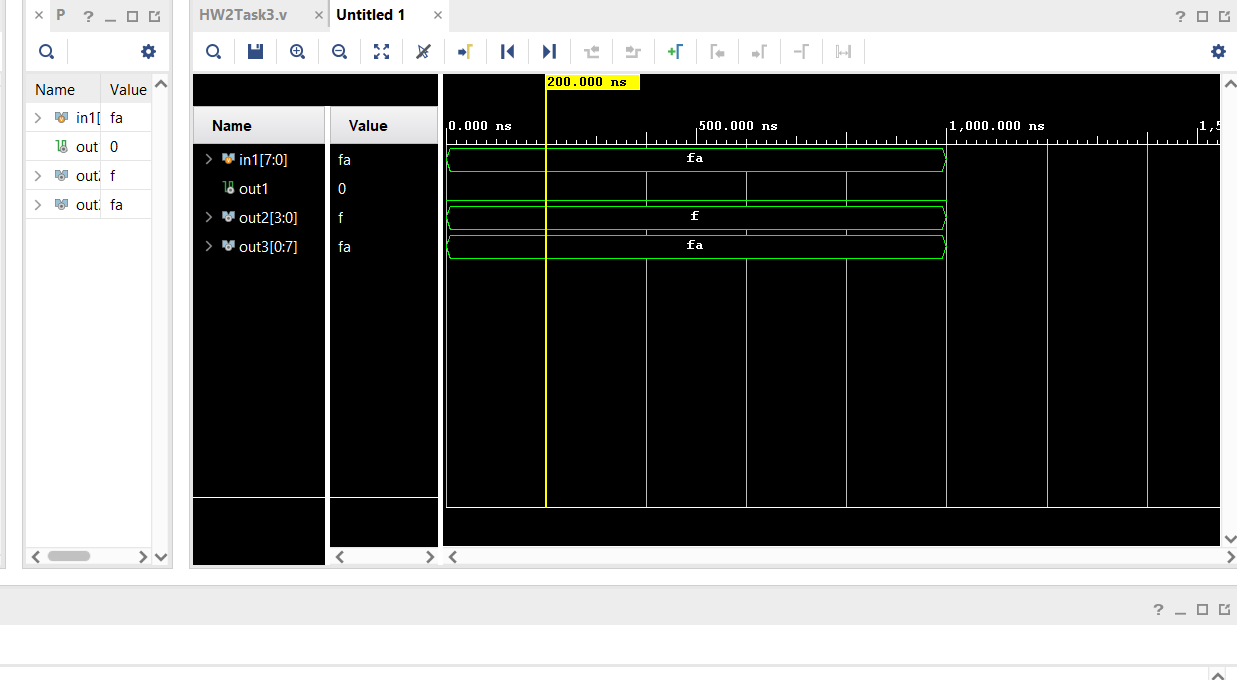

Figure

5: Shows the simulation results in vivado of section 11

Task 4: Repeat the work in section 14.1 14.2 and 14.3

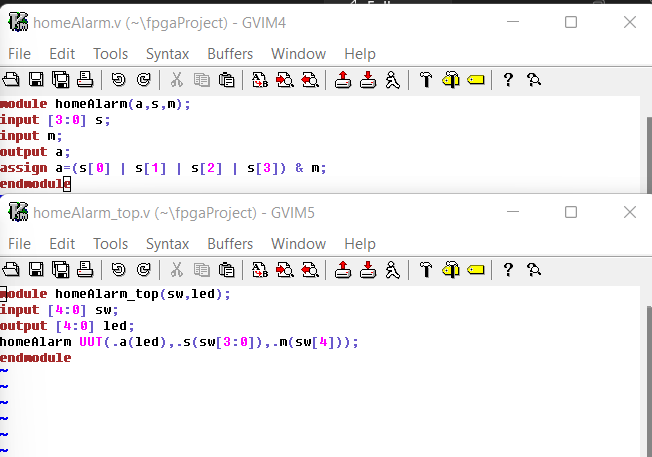

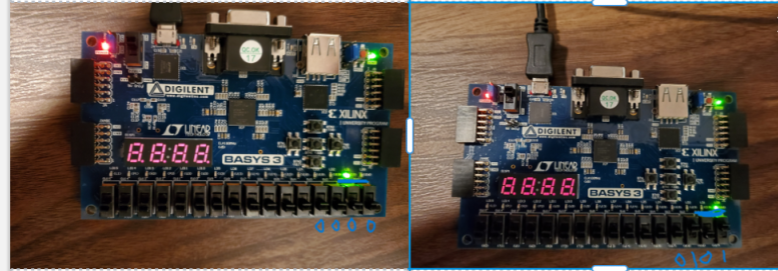

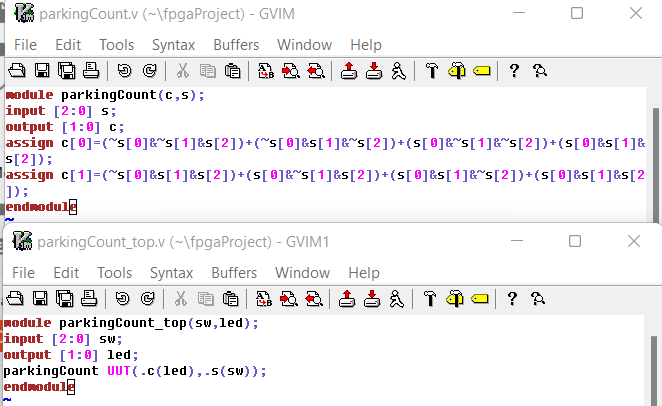

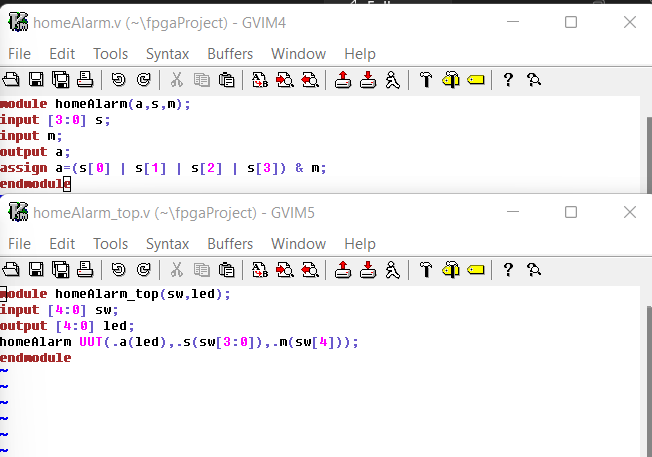

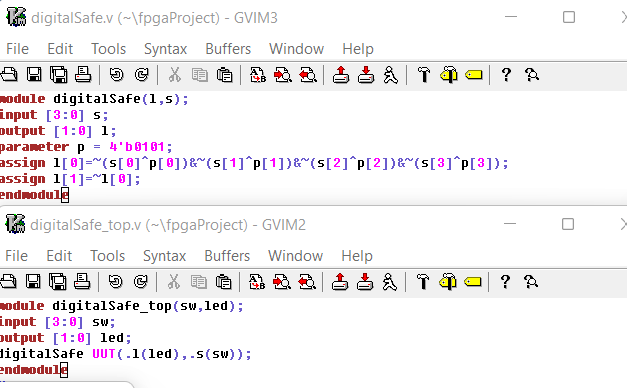

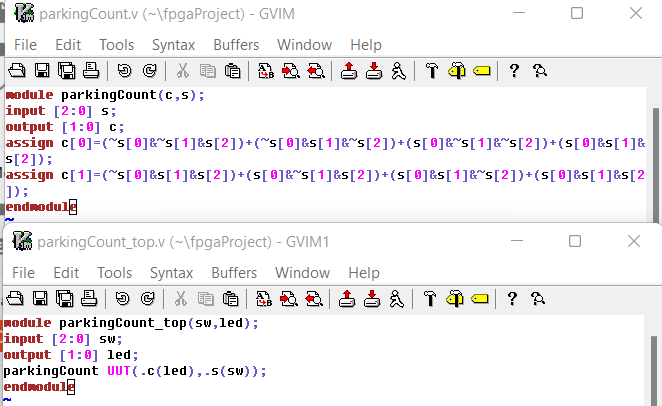

Figure 6: Shows the

gvim code for the example 14.1

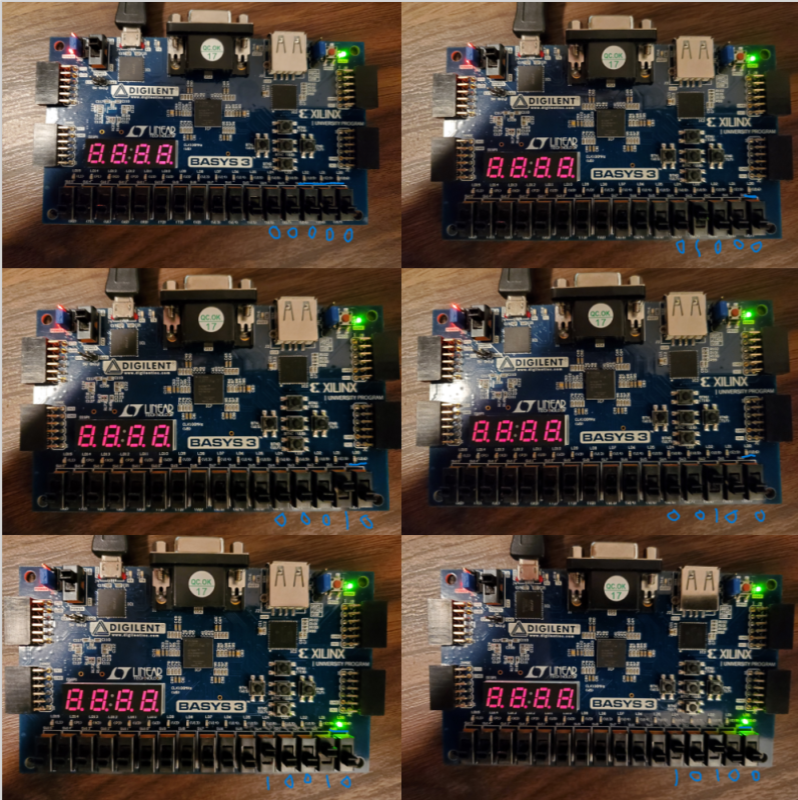

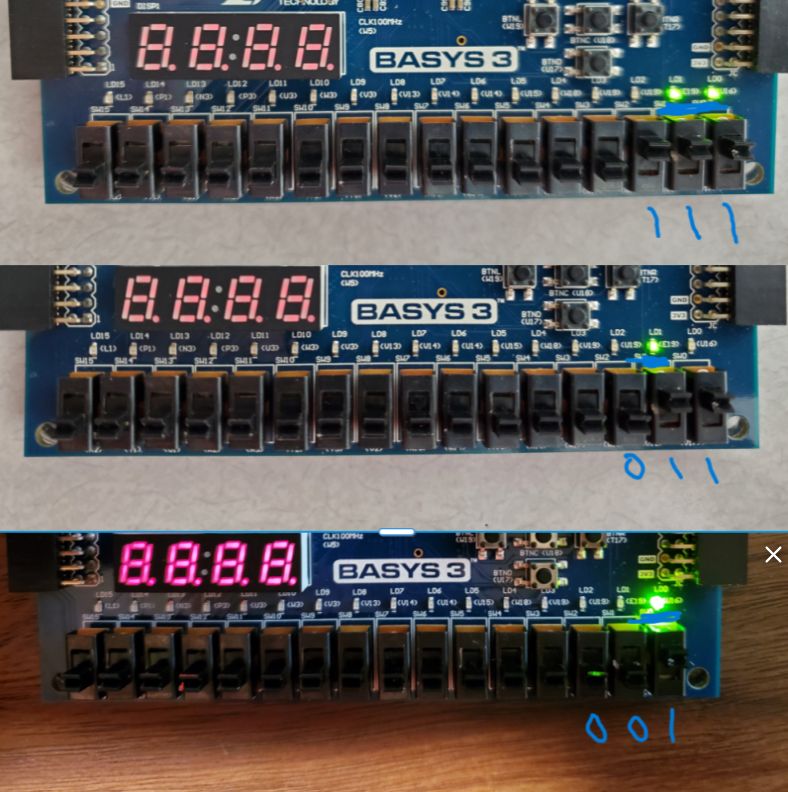

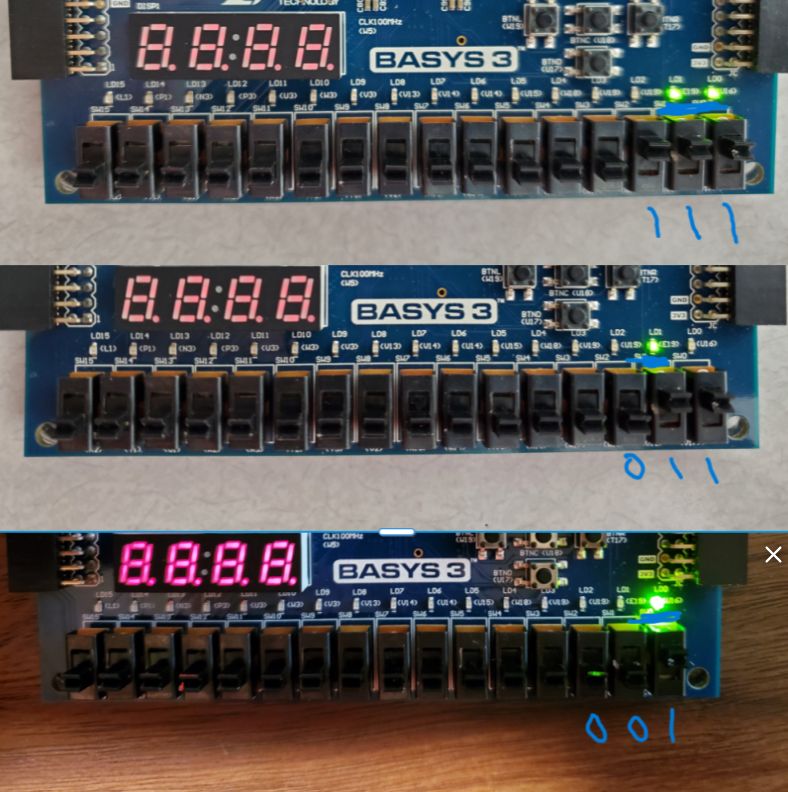

Figure 7: Shows the Results of the Vivado work on the board of example 14.1

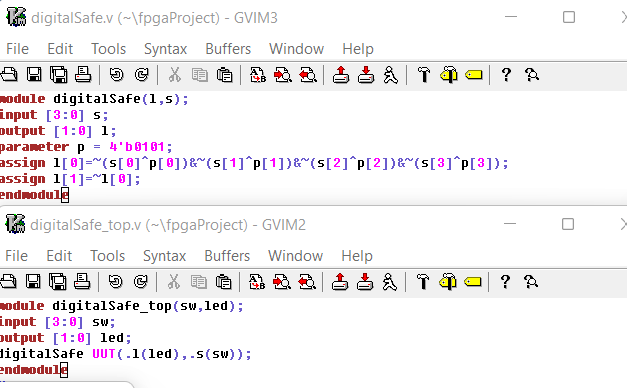

Figure 8: Shows the

gvim code for the example 14.2

Figure 9: Shows the Results of the Vivado work on the board of example 14.2

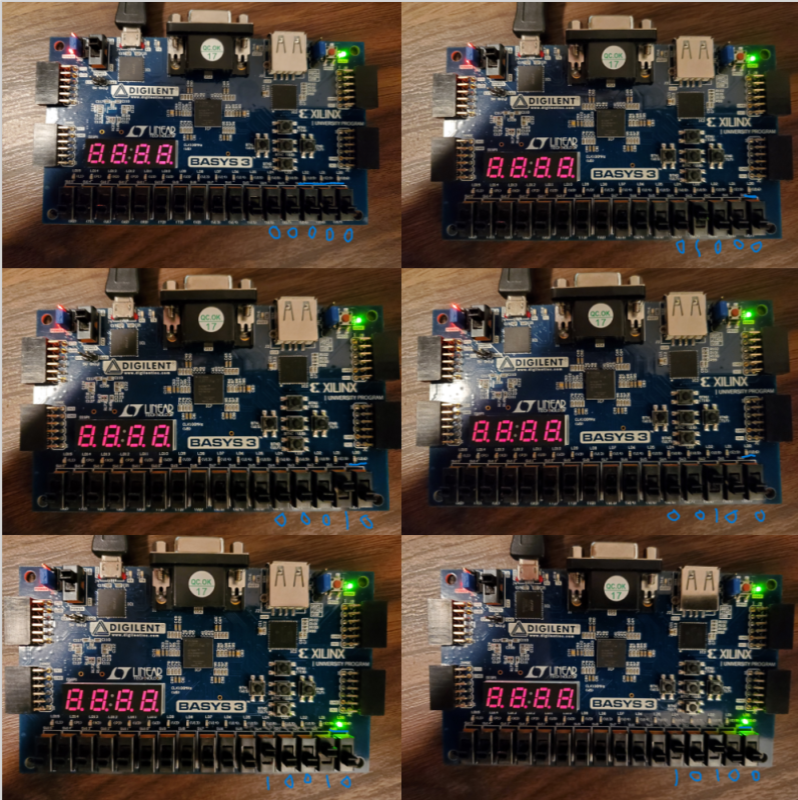

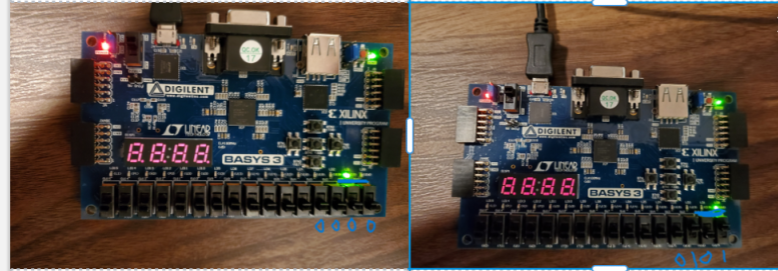

Figure 10: Shows the

gvim code for the example 14.3

Figure 11: Shows the Results of the Vivado work on the board of example 14.3

Discussion:

As

seen in the figures above I was

able to successfully complete the assignment of getting familar with

gvim and vivado. This Class assignment was reall good to do because it

helped introduce me into how to make fpgas function and how we are able

to easily use them.