CE 433 Lab Spring 2022

Lab 1

Name: David Lee

Email:

djlee1@fortlewis.edu

Verilog

and FPGA Basics

Introduction:

In this homework assignment we setup vim and get familar with the new

software Vivado.

Materials and Methods:

vim and Vivado

Results:

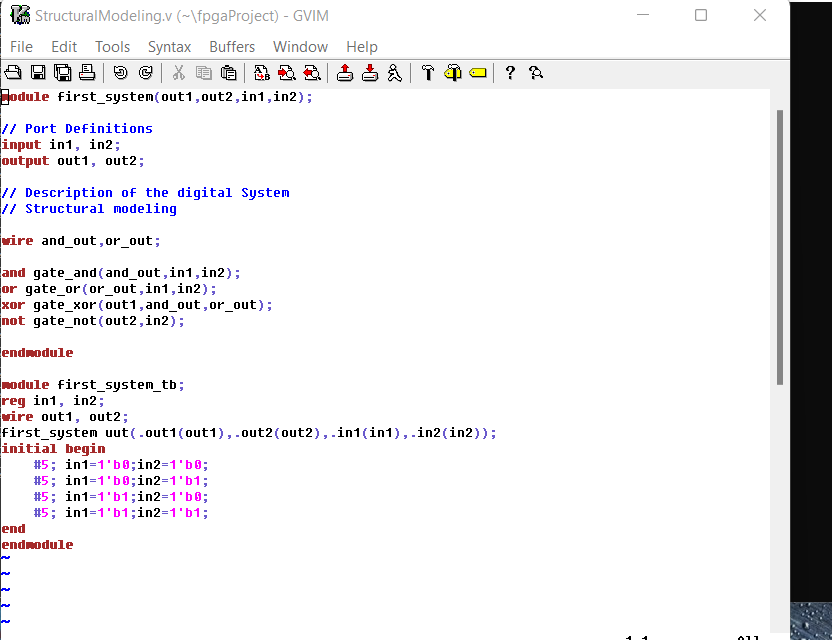

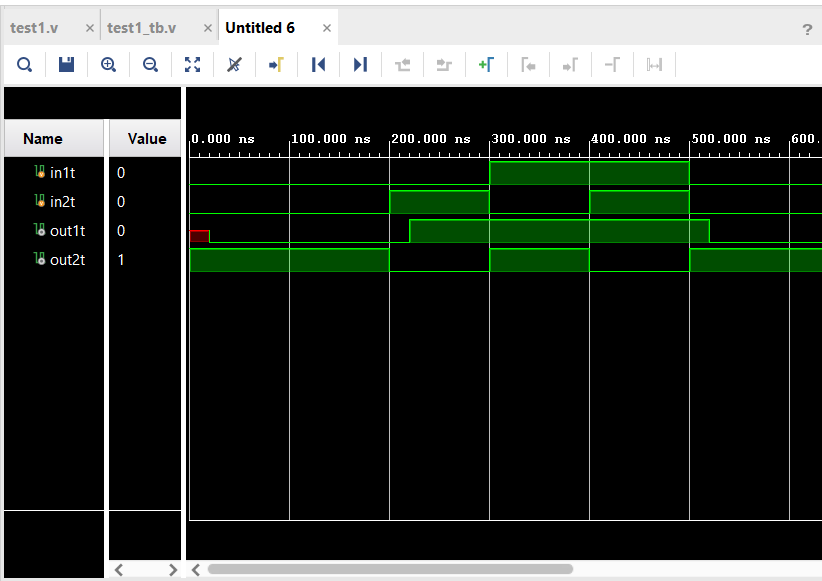

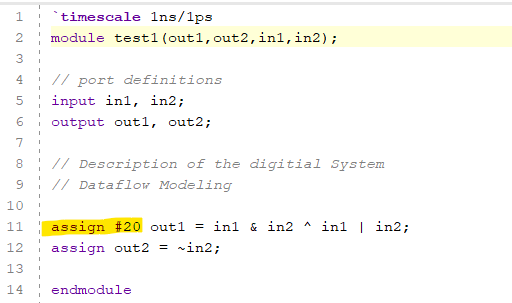

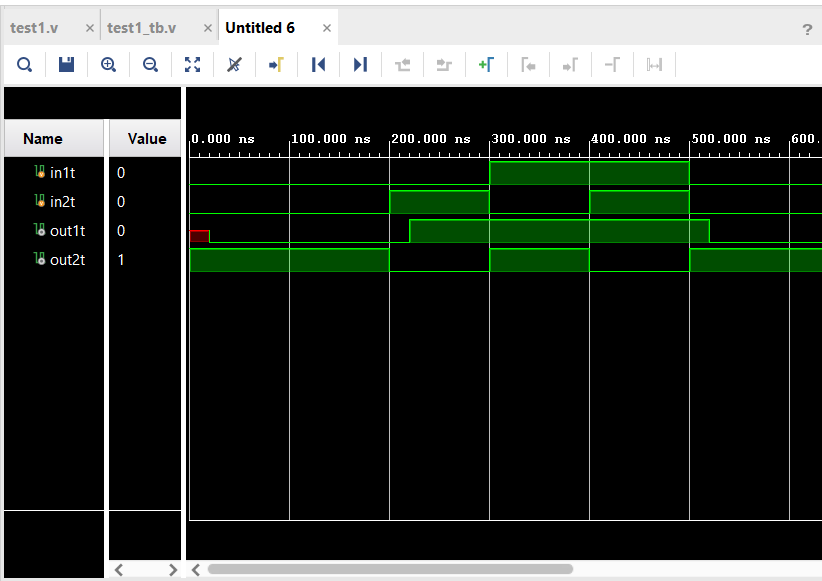

Task 1: Use gvim and Vivado to simulate the examples in sections

2.1,2.2,2.3. Post snapshots of gvim windoes and vivado simulations

results in your report. You must create testbenches for your simulations

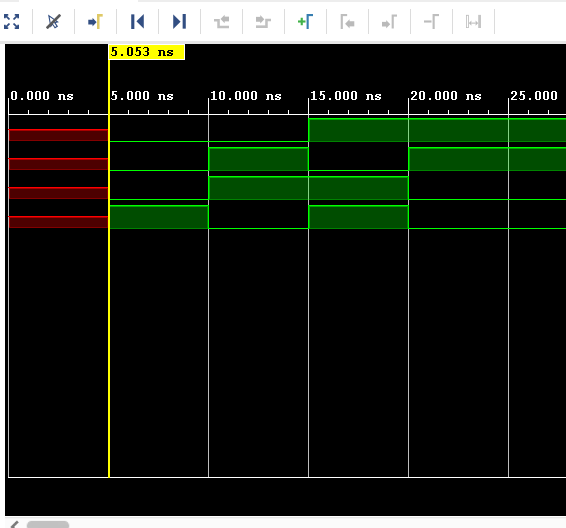

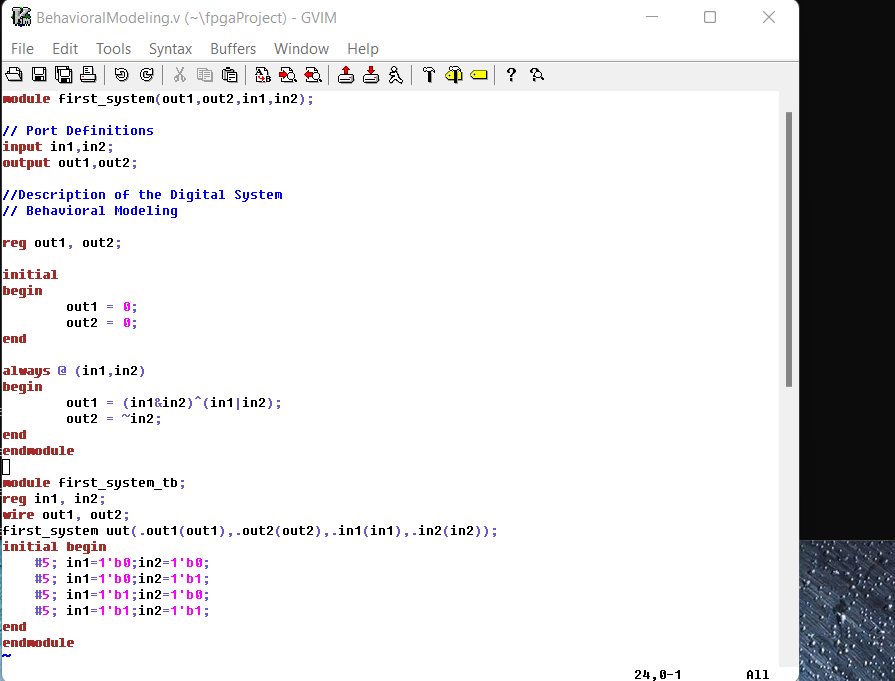

Figure 1: Shows the

gvim code for the example 2.1

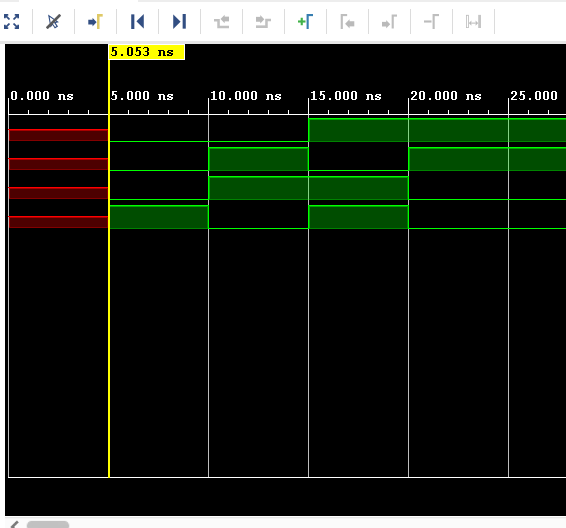

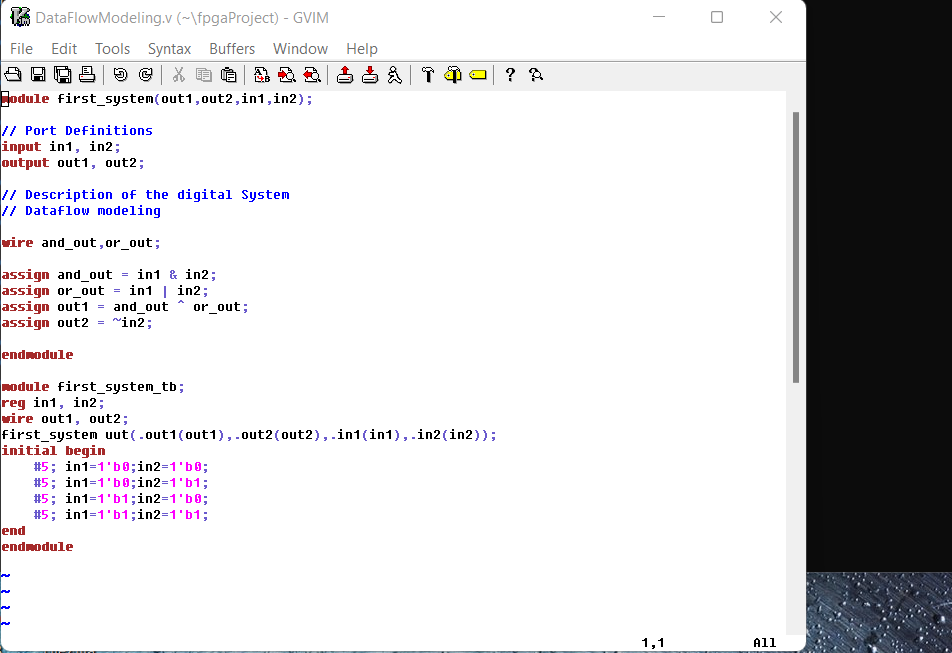

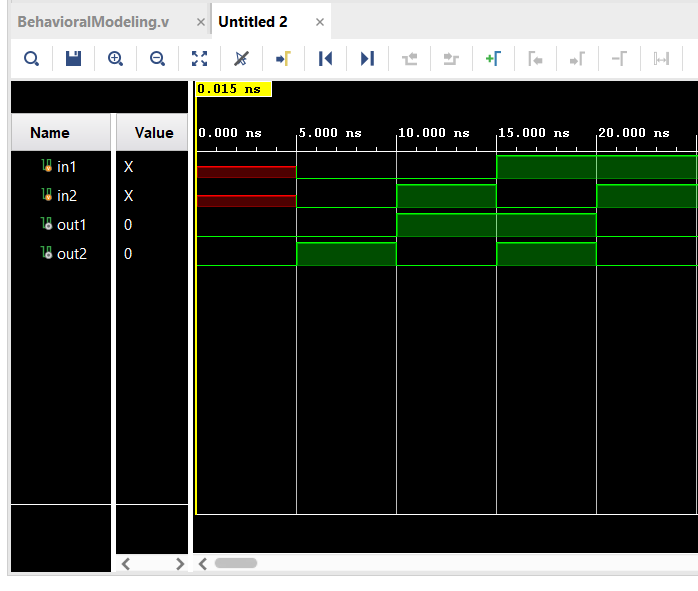

Figure 2: Shows the simulation results in vivado of example 2.1

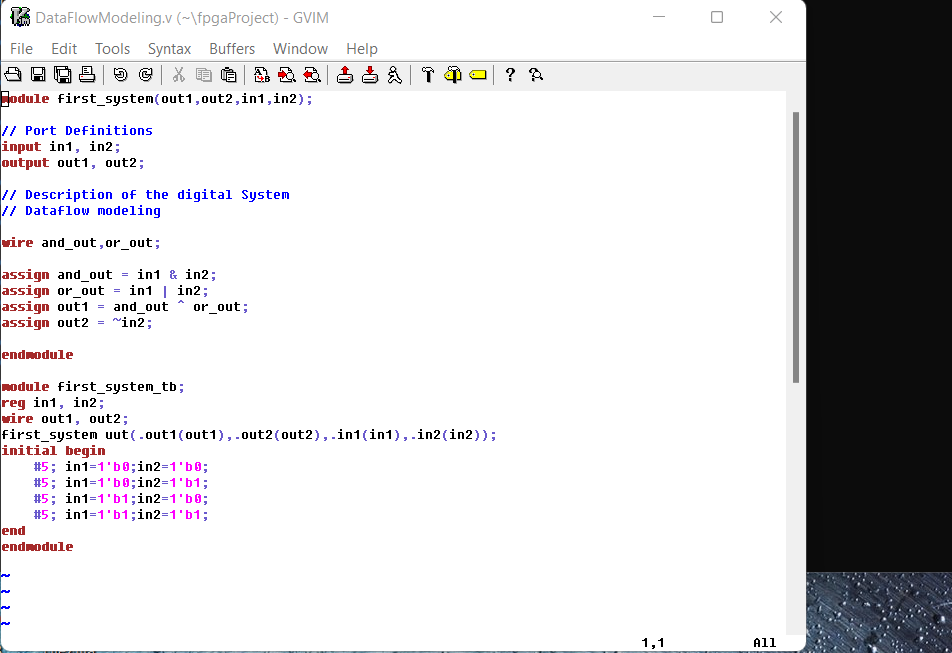

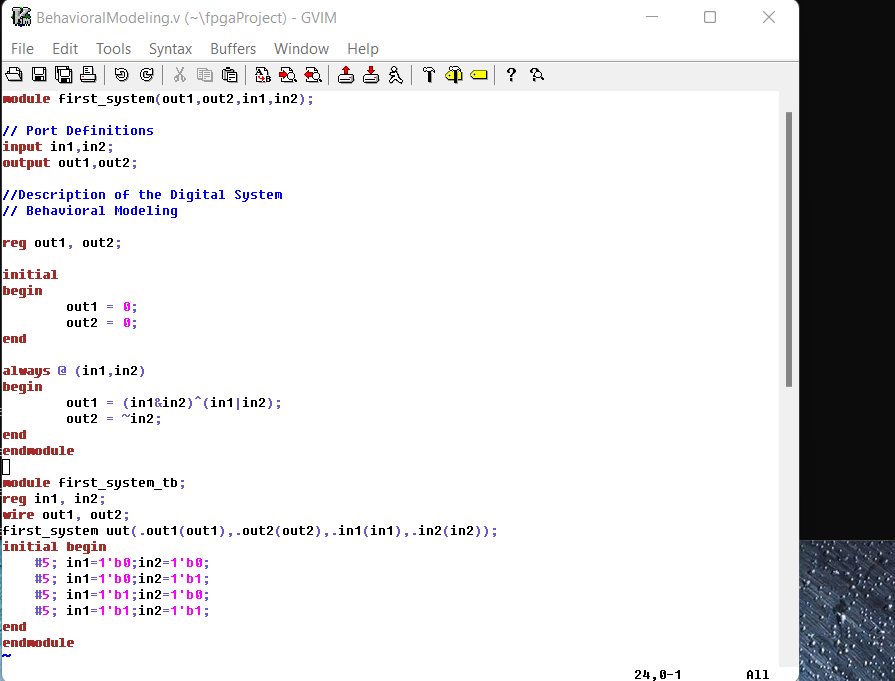

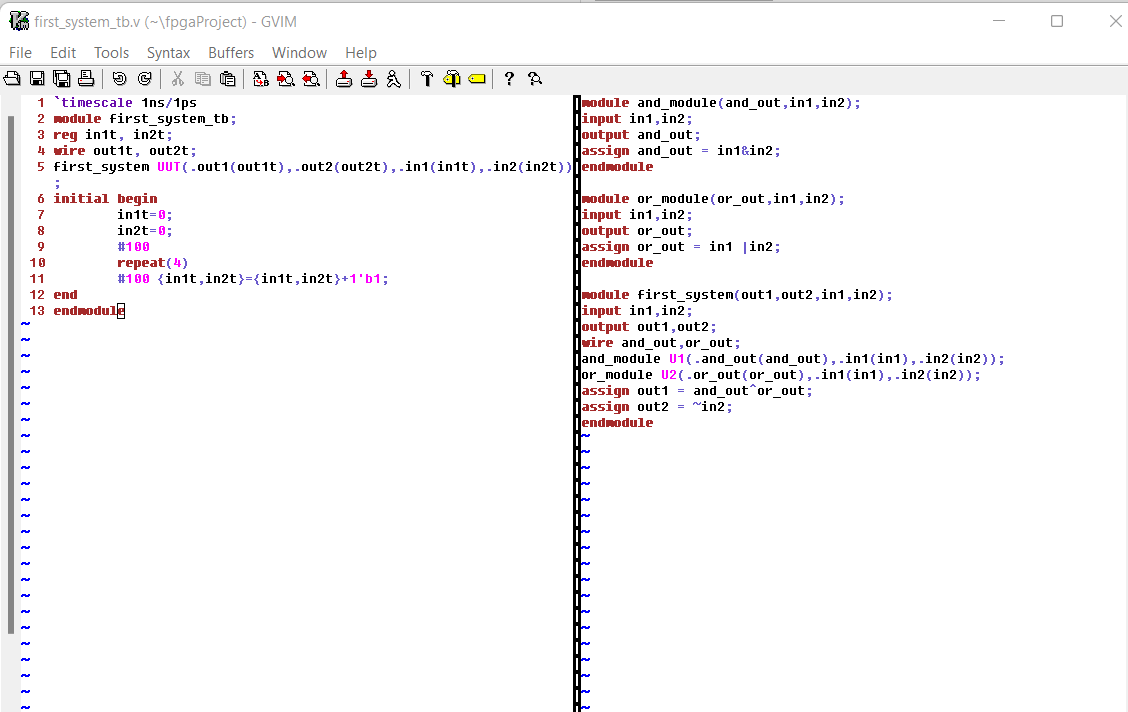

Figure 3: Shows the

gvim code for the example 2.2

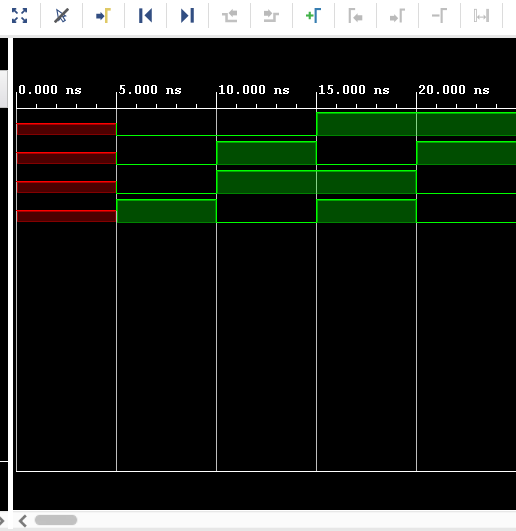

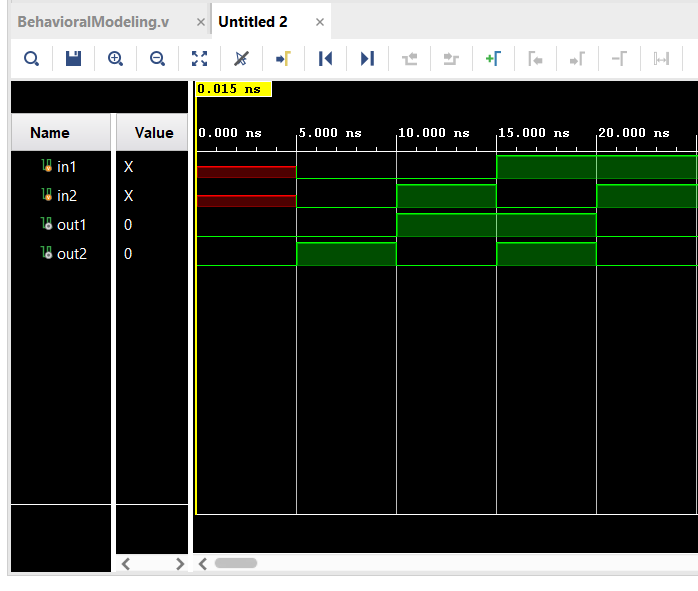

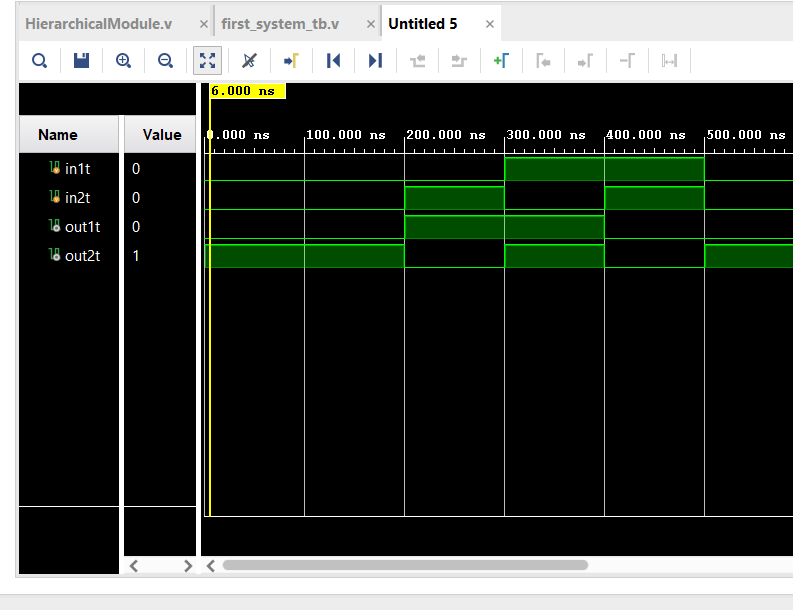

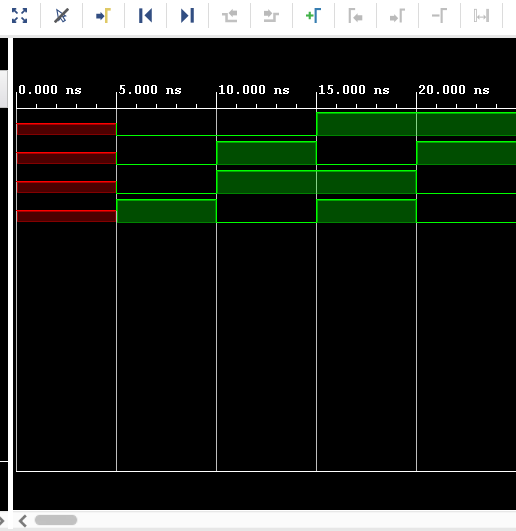

Figure 4: Shows the simulation results in vivado of example 2.2

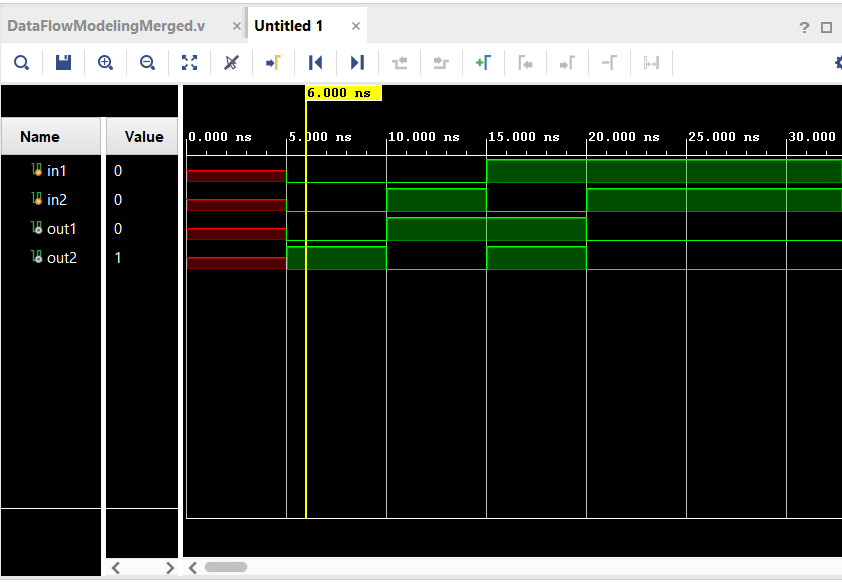

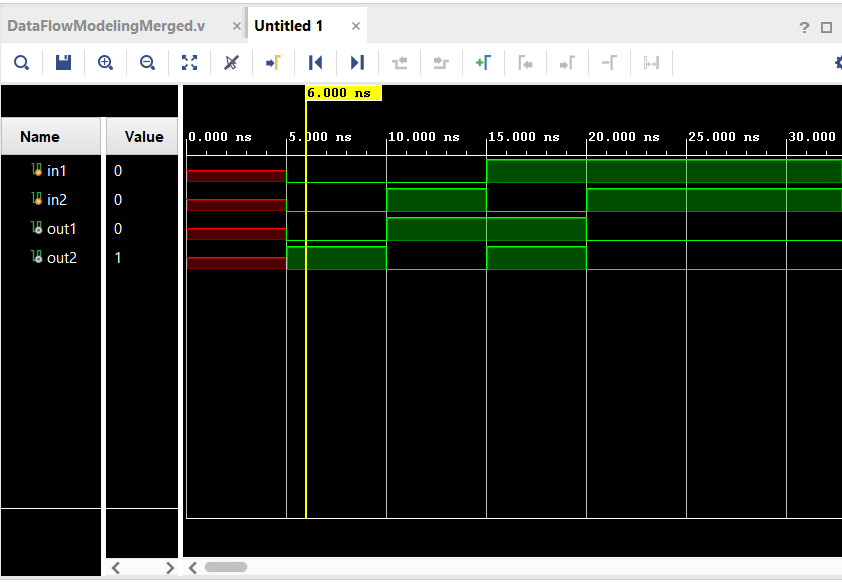

Figure 5: Shows the simulation results in vivado of example 2.2 with merged assignments.

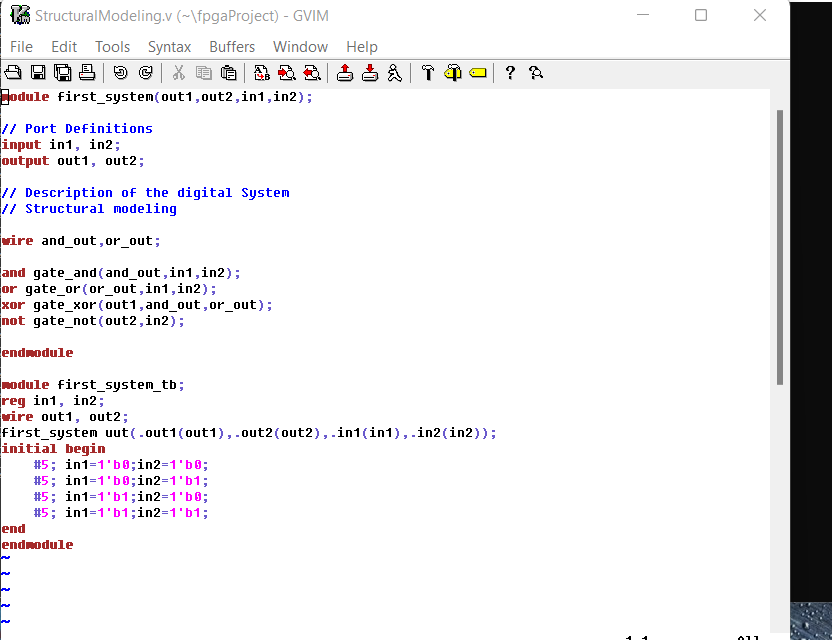

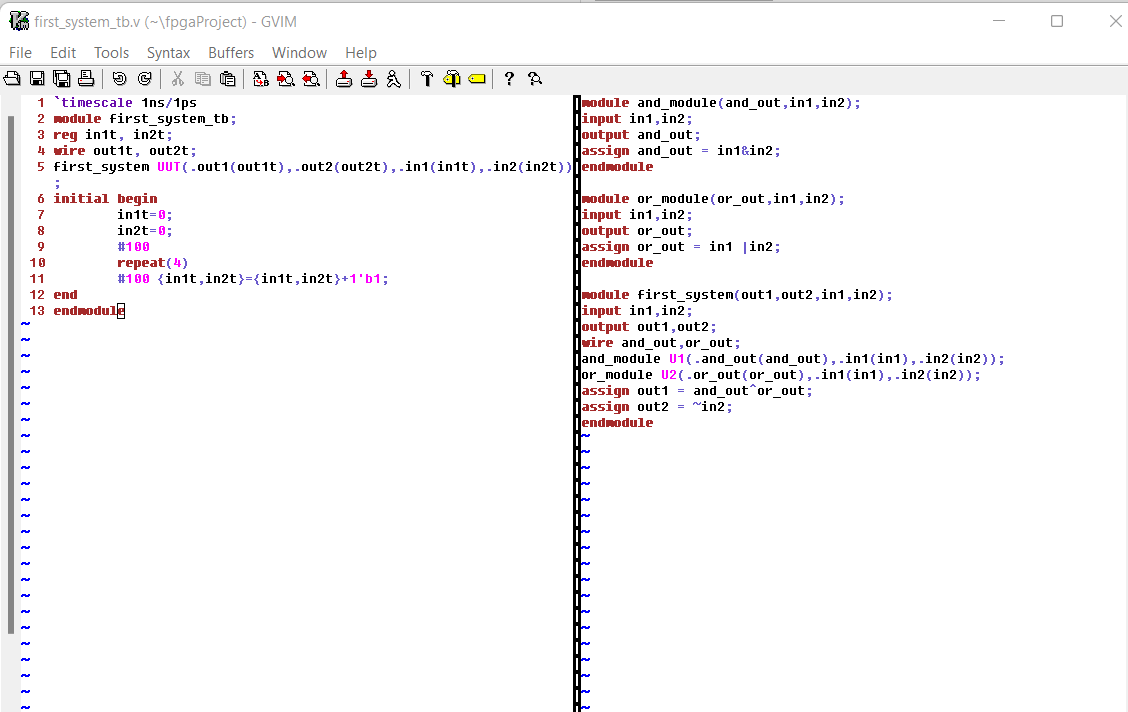

Figure 6: Shows the

gvim code for the example 2.3

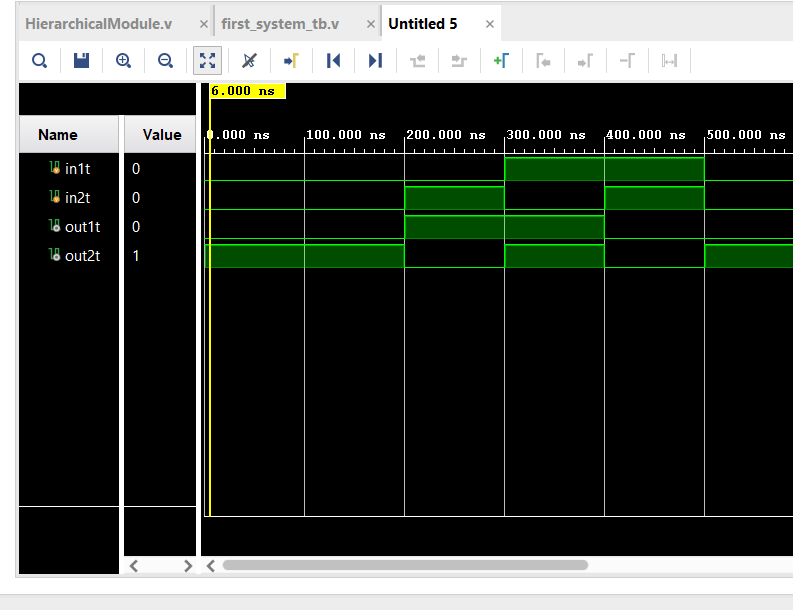

Figure 7: Shows the simulation results in vivado of example 2.3

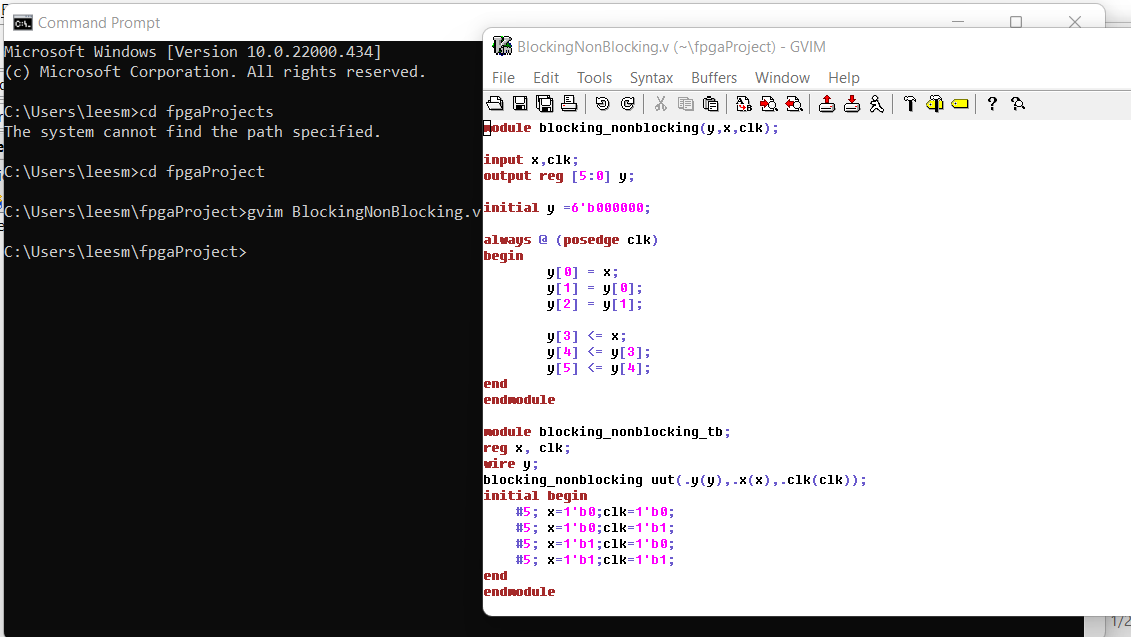

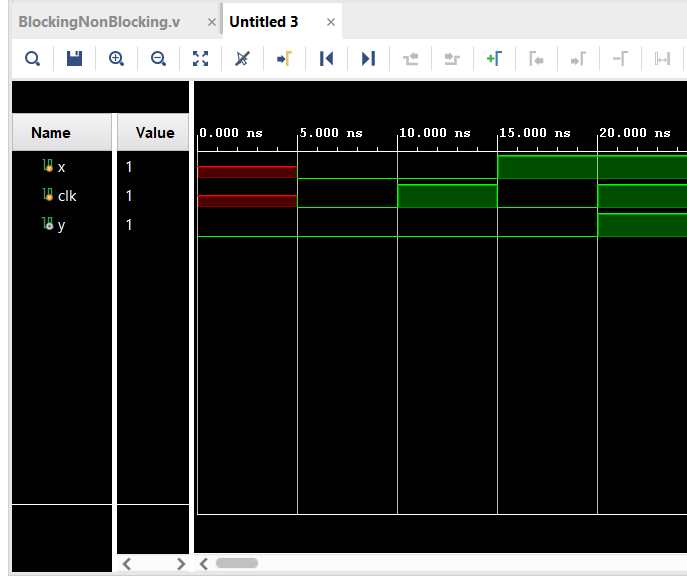

Task 2: Run a simulation to show the difference of blocking and non-blocking assignment in example 2.4

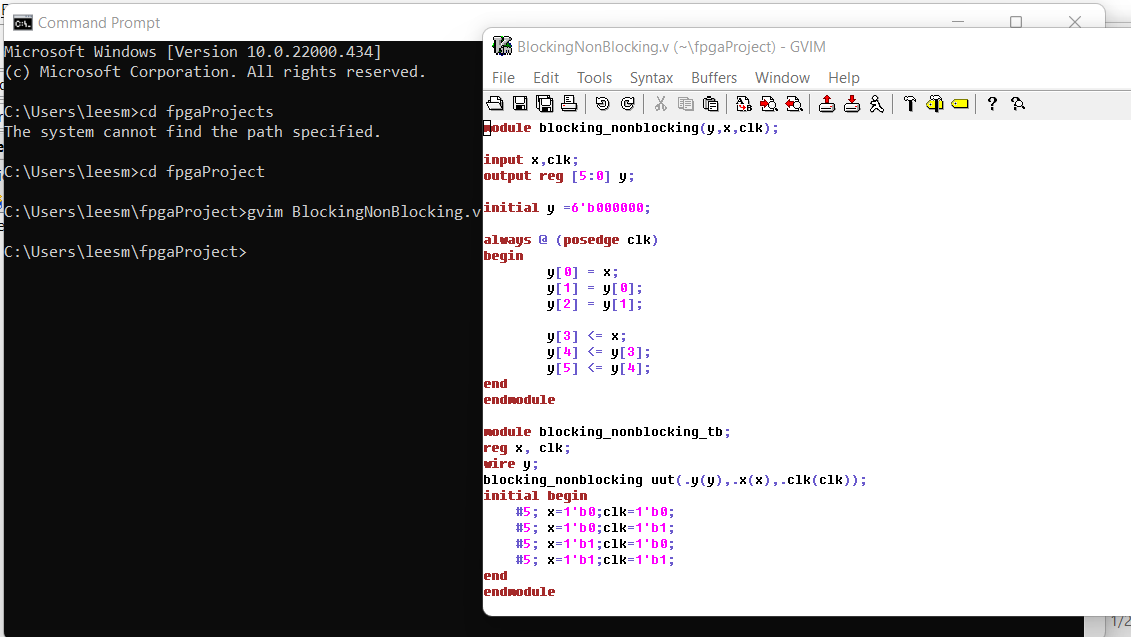

Figure 8: Shows the

gvim code for the example 2.4

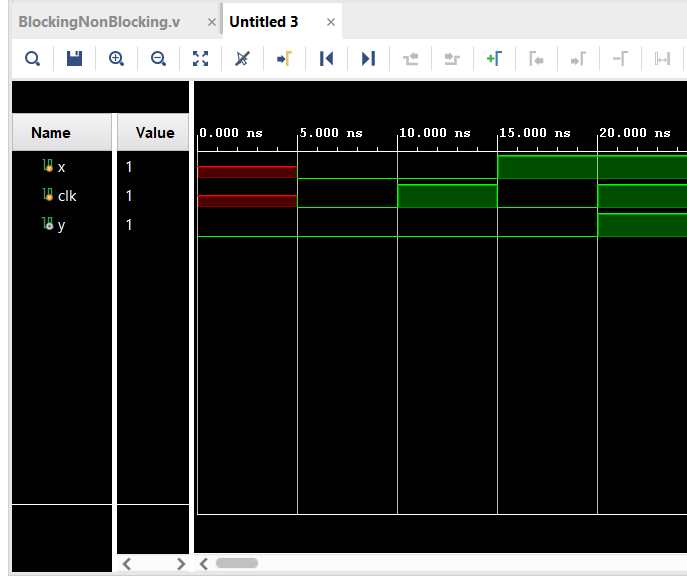

Figure 9: Shows the simulation results in vivado of example 2.4

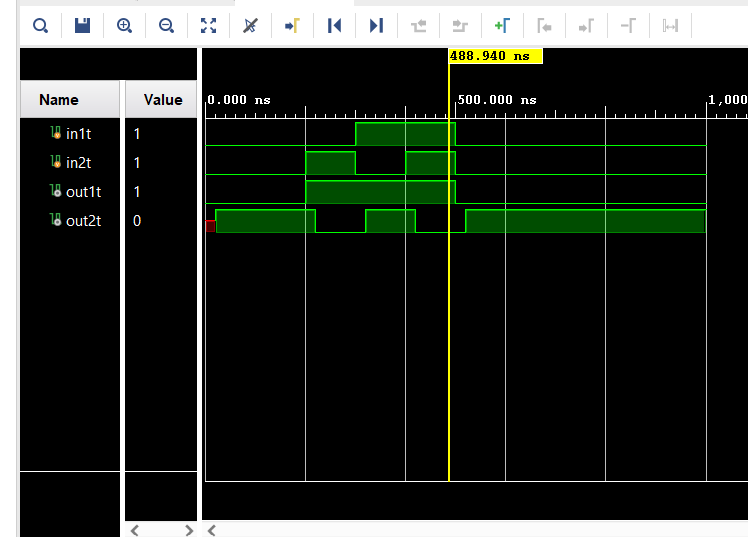

Task 3:

Repeat the simulation example in section 2.5

Figure 10: Shows the

gvim code for the example 2.5

Figure 11: Shows the simulation results in vivado of example 2.5

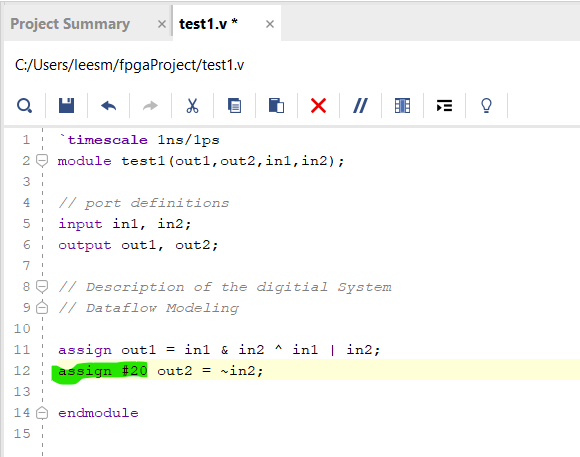

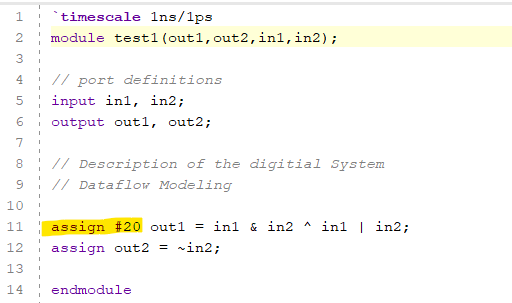

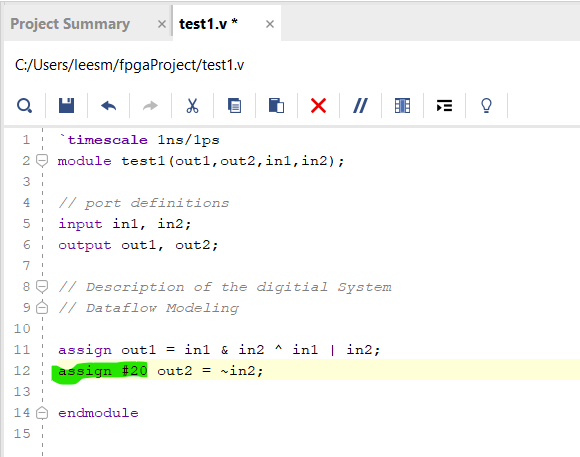

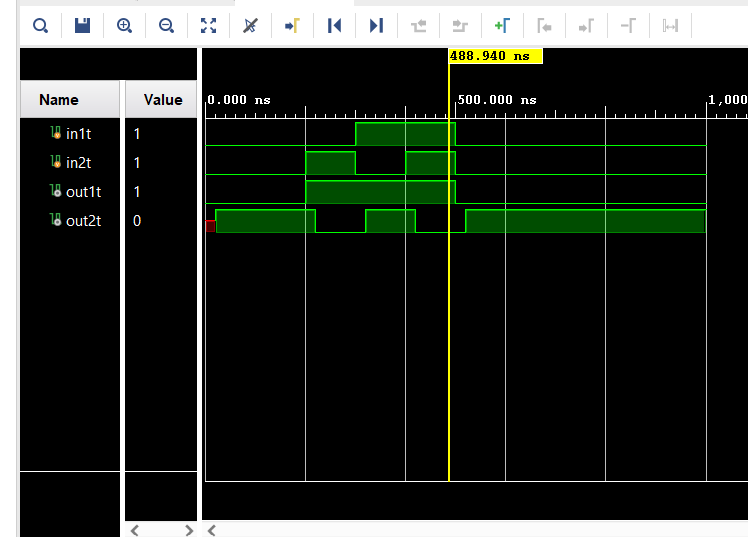

Task 4: For the example Task 3 move the 20ns delay from line 12 to line 11

Figure 12: Shows the

gvim code for the example 2.5

Figure 13: Shows the simulation results in vivado of example 2.5

Task 5: Use gvim and vivado, repeat the example in section 2.6.

Figure 14: Shows the

gvim code for the example 2.6

Figure 15: Shows the simulation results in vivado of example 2.6

Discussion:

As seen in the figures above I was able to successfully complete the assignment of getting familar with gvim and vivado.