# Lab 8 Design a MUX, and a High-Speed Full Adder

Calvin Reese cjreese@fortlewis.edu

11/8/2021

#### 1 Introduction

Full Adders and MUX are an integral part of any circuit that requires basic arithmetic. In this lab, we will be going over the creation of a High Speed Full Adder.

#### 2 Materials and Methods

The tutorial for making these exact example in Electric VLSI are found in /urlhttp://www.yilectronics.com/Courses/ENGR338 L $_CE/f2021/lab8_MUX_FAII/Lab8.html$

## 3 Results

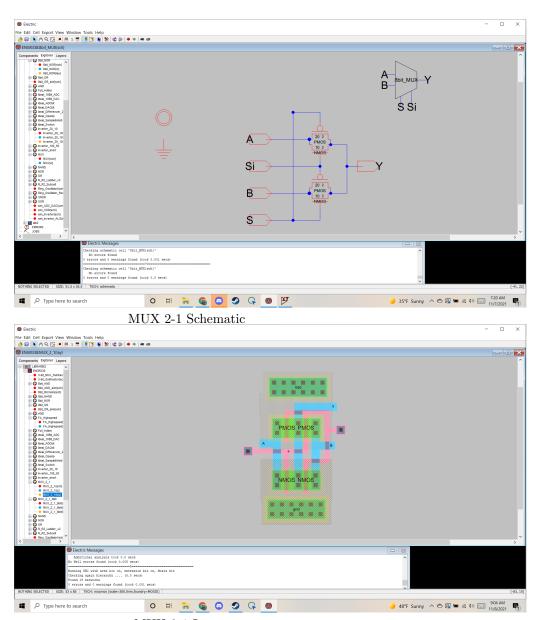

MUX 2-1 Layout

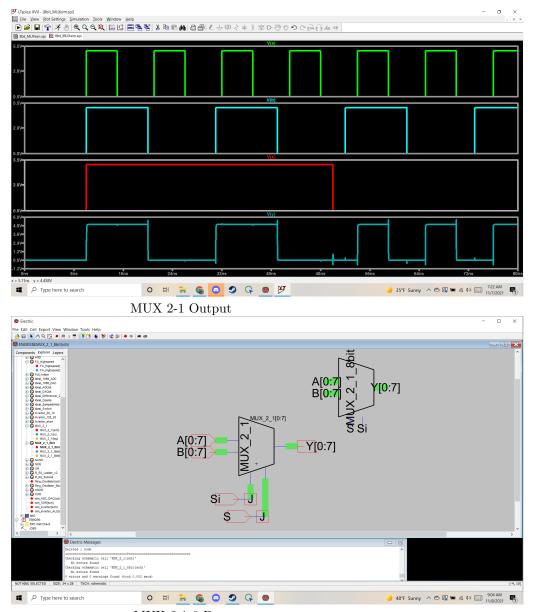

MUX 2-1 8 Bus

MUX 2-1 8 Bus Output

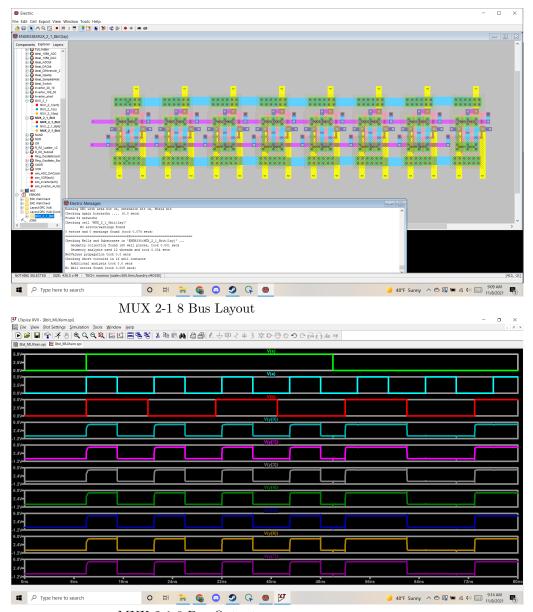

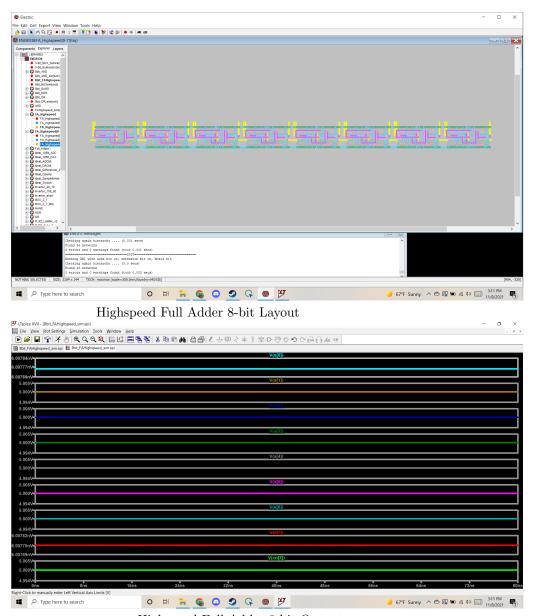

Highspeed Full Adder Layout

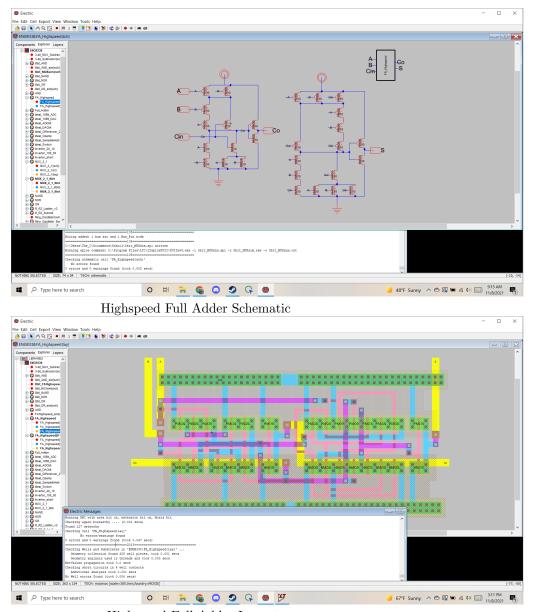

Highspeed Full Adder 8-bit Output

### 4 Discussion

As you can see, all the the outputs are correct and all the checks come clean, so these schematics and layouts work. I'm not sure if you actually read these, but I don't know where the NCC hierarchical checks is, so thats why they're

not there.