# Lab 2 Introduction to FPGA

Calvin Reese cjreese@fortlewis.edu

2/3/22

### 1 Introduction

This lab we loaded 3 sets of simple programs to learn how to design logic code and program the FPGA

### 2 Materials and Methods

The tutorial for making these examples are in http://www.yilectronics.com/ Courses/CE433\_Labs/s2022/Lab2\_FPGA\_Basics/Lab2.html

### 3 Results

TASK 3: Video explaining volitile vs non-volitial programs loaded on the FPGA:

### 3.1 Task 1

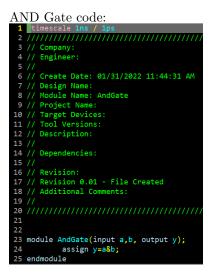

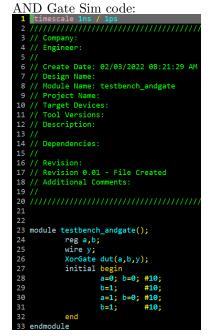

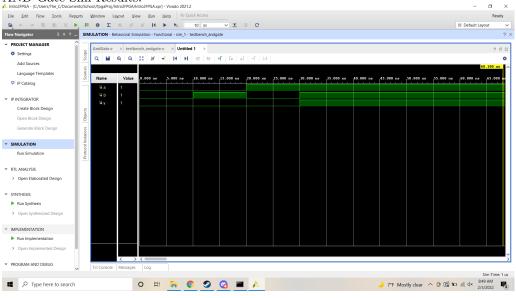

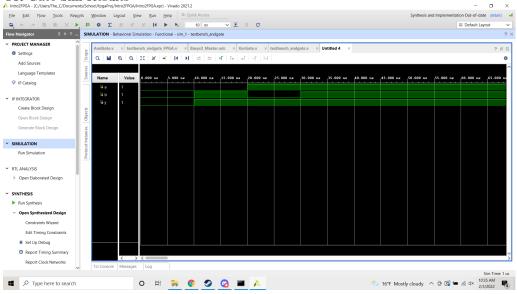

#### AND Gate Sim Results:

AND Gate Programming Code: `timescale 1ns / 1ps

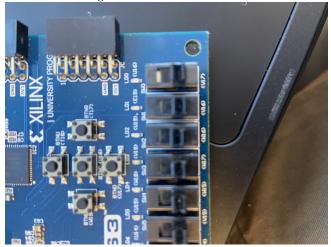

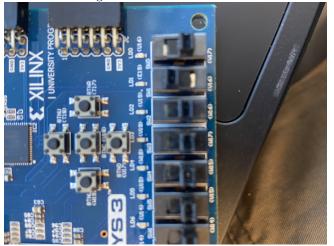

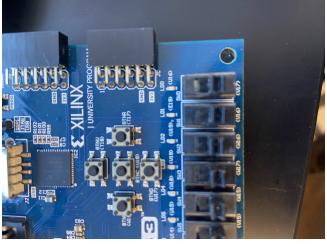

AND FPGA Logic 00

AND FPGA Logic 10

AND FPGA Logic 01

Common State

#### 3.2 Task 2

OR Gate Sim Code

OR Gate Sim Results

OR FPGA Logic 00

OR FPGA Logic 10

OR FPGA Logic 01

OR FPGA Logic 11

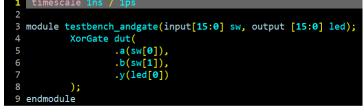

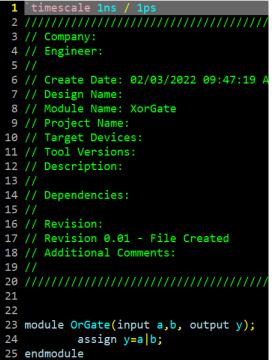

XOR Gate Sim Code

| 1 `timescale 1ns / 1ps                             |

|----------------------------------------------------|

| 2 /////////////////////////////////////            |

| 3 // Company:                                      |

| 4 // Engineer:                                     |

| 5 //                                               |

| 6 // Create Date: 02/03/2022 09:47:19 AM           |

| 7 // Design Name:                                  |

| 8 // Module Name: XorGate                          |

| 9 // Project Name:                                 |

| 10 // Target Devices:                              |

| 11 // Tool Versions:                               |

| 12 // Description:                                 |

| 13 //                                              |

| 14 // Dependencies:                                |

| 15 //                                              |

| 16 // Revision:                                    |

| 17 // Revision 0.01 - File Created                 |

| 18 // Additional Comments:                         |

| 19 //                                              |

| 20 ////////////////////////////////////            |

| 21                                                 |

| 22                                                 |

| <pre>23 module XorGate(input a,b, output y);</pre> |

| <pre>24 assign y=a^b;</pre>                        |

| 25 endmodule                                       |

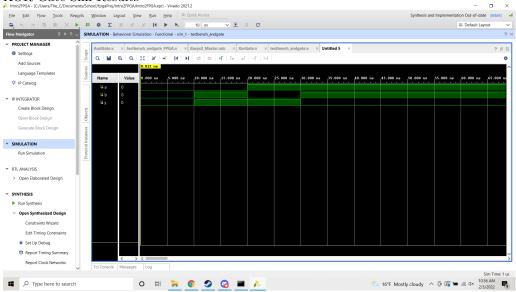

XOR Gate Sim Results

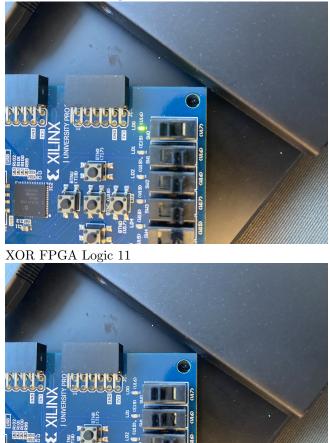

XOR FPGA Logic 00

XOR FPGA Logic 10

XOR FPGA Logic 01

## 4 Discussion

All of this was fairly simple just to follow your tutorial. I just reused the FPGA and Sim code for the OR and XOR for efficiency. I am excited to see where this takes us.