# Data Storage Units

Calvin Reese cjreese@fortlewis.edu

2/21/22

# 1 Introduction

This HW, we worked on integrating memory with our code.

# 2 Materials and Methods

The tutorial for making these examples are in http://www.yilectronics.com/Courses/CE433/s2022/lectures/week4\_dataStorage/week4\_DataStorage.html

# 3 Results

### 3.1 Task 1

```

SR Latch Code

3 module SRlatch(s,r,q,qn);

4 input s,r;

5 output reg q;

6 output reg qn;

7 always @(s or r)

if(s) \{q,qn\} <= 2'b10;

else if(r) {q,qn} <= 2'b01;

0 endmodule

.2 module SRlatch_tb;

3 reg s,r;

4 wire q,qn;

.5 SRlatch UUT(.q(q),.qn(qn),.s(s),.r(r));

.6 initial begin

{s,r} = 2'b10; #10;

{s,r} = 2'b01; #10;

.9 end

0 endmodule

```

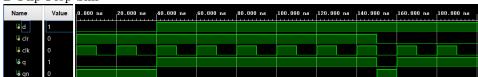

| SR Latch Sim |       |          |           |  |  |  |

|--------------|-------|----------|-----------|--|--|--|

| Name         | Value | 0.000 ns | 10.000 ns |  |  |  |

| ₩ s          | 0     |          |           |  |  |  |

| ₩r           | 1     |          |           |  |  |  |

| ™ q          | 0     |          |           |  |  |  |

| ¹⊌ qn        | 1     |          |           |  |  |  |

#### SR Flip Flop Code

```

23 module SRFF(s,r,q,qn,clk);

24 input s,r,clk;

25 output reg q;

26 output reg qn;

27 always @(s or r or clk)

28    if(clk & s) {q,qn} <= 2'b10;

29    else if(clk & r) {q,qn} <= 2'b01;

30 endmodule

31

32 module SRFF_tb;

33 reg s,r,clk;

34 wire q,qn;

35 SRFF UUT(.q(q),.qn(qn),.s(s),.r(r),.clk(clk));

36 initial begin

37 {s,r,clk} = 3'b101; #10;

38 {s,r,clk} = 3'b001; #10;

39 {s,r,clk} = 3'b011; #10;

{s,r,clk} = 3'b001; #10;

40

41 end

42 endmodule

```

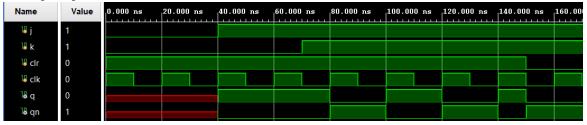

#### SR Flip Flop Sim

#### D Latch Code

```

45 module Dlatch(d,c,q,qn);

46 input d,c;

47 output reg q;

48 output reg qn;

49 always @(d or c)

if(c) {q,qn} <= {d,~d};

50

51 endmodule

52

53 module Dlatch_tb;

54 reg d,c;

55 wire q,qn;

56 Dlatch UUT(.q(q),.qn(qn),.d(d),.c(c));

57 initial begin

58 {d,c} = 2'b10; #10;

59 {d,c} = 2'b01; #10;

60 {d,c} = 2'b11; #10;

61 {d,c} = 2'b10; #10;

62 end

63 endmodule

```

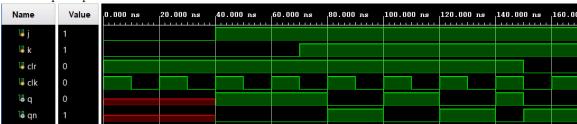

### D Latch Sim

| Name | Value | 0.000 ns | 20.000 ns |  |

|------|-------|----------|-----------|--|

| ₩ d  | 0     |          |           |  |

| ₩ c  | 0     |          |           |  |

| ₩ q  | 1     |          |           |  |

| ¼ qn | 0     |          |           |  |

#### D Flip Flop Code

```

66 module DFF(d,clr,q,qn,clk);

67 input d,clr,clk;

68 output reg q;

69 output reg qn;

70 always @(posedge clk or negedge clr)

71 if(clk == 0) {q,qn} <= 2'b01;

72

else \{q,qn\} \leftarrow \{d,\sim d\};

73 endmodule

74

75 module DFF_tb;

76 reg d=0;

77 reg clr=1;

78 reg clk=0;

79 wire q,qn;

80 integer i;

81 DFF UUT(.q(q),.qn(qn),.d(d),.clr(clr),.clk(clk));

82 initial begin

83 for(i=0;i<20;i=i+1)begin</pre>

clk=~clk;

84

85

if(i>3&i<10) d=1;

86

if(i==15) clr=0;

87

#10;

88

end

89 end

```

### D Flip Flop Sim

#### 3.2 Task 2

#### JK Flip Flop Sim

#### JK Flip Flop Code

```

94 module JKFF(j,k,clr,q,qn,clk);

95 input j,k,clr,clk;

96 output reg q;

97 utput reg qn;

98 always @(posedge clk, negedge clr)

99 if(clr == 0) {q,qn} <= 2'b01;</pre>

100

else

case({j,k})

101

2'b01: {q,qn} <= 2'b01;

2'b10: {q,qn} <= 2'b10;

102

103

2'b11: {q,qn} <= {qn,q};

104

105

endcase

106 endmodule

107

108 module JKFF_tb;

109 reg j=0;

110 reg k=0;

111 reg clr=1;

112 reg clk=0;

113 wire q,qn;

114 integer i;

115 JKFF UUT(.q(q),.qn(qn),.j(j),.k(k),.clr(clr),.clk(clk));

116 initial begin

for(i=0;i<20;i=i+1)begin

117

118

clk=~clk;

if(i>3&i<9) j=1;

if(i>6&i<9) k=1;

if(i==15) clr=0;</pre>

119

120

121

122

#10;

123

end

124 end

125 endmodule

```

T Flip Flop Sim

# T Flip Flop Code

```

129 module TFF(t,clr,q,qn,clk);

130 input t,clr,clk;

131 output reg q;

132 output reg qn;

133 always @(posedge clk, negedge clr)

134 if(clr == 0) {q,qn} <= 2'b01;

135

else

136

begin

137

q<= t^q;</pre>

138

qn<=\sim(t^q);

139

end

140 endmodule

141

142 module TFF_tb;

143 reg t=0;

144 reg clr=1;

145 reg clk=0;

146 wire q,qn;

147 integer i;

148 TFF UUT(.q(q),.qn(qn),.t(t),.clr(clr),.clk(clk));

149 initial begin

for(i=0;i<20;i=i+1)begin

150

clk=~clk;

if(i>3&i<10) t=1;

151

152

153

if(i==15) clr=0;

154

#10;

155

end

156 end

157 endmodule

```

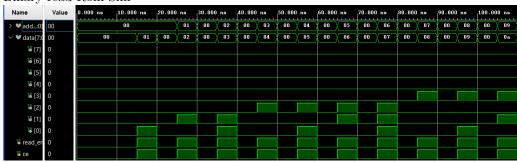

### 3.3 Task 3

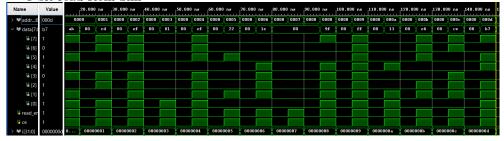

Binary read Rom Sim

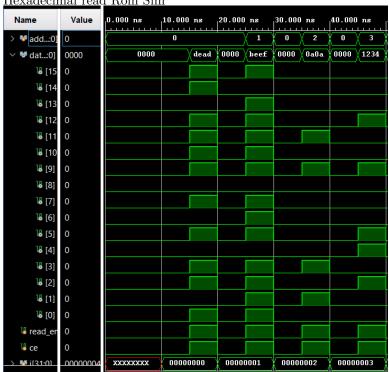

Hexadecimal read Rom Sim

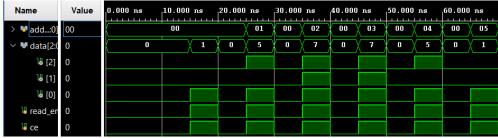

#### 3-bit read Rom Sim

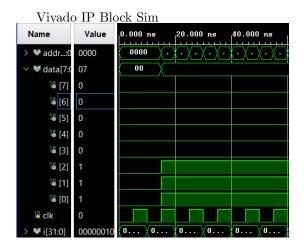

```

Vivado IP Block Code

194 module myRom_tb;

195 reg [15:0] address;

196 wire [7:0] data;

197 reg clk;

198 integer i;

199 initial begin

200

address=0;

clk =0;

for(i=0;i<16;i=i+1)begin</pre>

201

202

203

#5 address =i;

#5 address=0;

204

205

end

206 end

207 always #5 clk=~clk;

208 myRom U(.addra(address),.douta(data),.clka(clk));

209 endmodule

```

# 4 Discussion

All of this was fairly simple just to follow your tutorial. I had no trouble figuring out the problems.