# Data types, operators, combinational logic

Calvin Reese cjreese@fortlewis.edu

2/10/22

### 1 Introduction

This HW, we worked on refreshing our binary logic and uploading/testing some example codes to an FPGA.

### 2 Materials and Methods

The tutorial for making these examples are in http://www.yilectronics.com/Courses/CE433/s2022/lectures/week2\_dataTypes/week2\_dataTypes.html

### 3 Results

### 3.1 Task 3

Vector Example Code

Vector Example Sim

|          |         |          |            |            |            |            |            |            |            |            | 1,000.000 ns |

|----------|---------|----------|------------|------------|------------|------------|------------|------------|------------|------------|--------------|

| Name     | Value   | 0.000 ns | 100.000 ns | 200.000 ns | 300.000 ns | 400.000 ns | 500.000 ns | 600.000 ns | 700.000 ns | 800.000 ns | 900.000 ns   |

| > ₩ in1[ | 0:7] fa | fa       |            |            |            |            |            |            |            |            |              |

| ¹⊌ out   | Z       |          |            |            |            |            |            |            |            |            |              |

| > ₩ out2 | 2[3:0 Z |          |            |            |            |            | z          |            |            |            | '            |

| > ₩ out  | (0:7 fa | fa       |            |            |            |            |            |            |            |            |              |

|          |         |          |            |            |            |            |            |            |            |            |              |

|          |         |          |            |            |            |            |            |            |            |            |              |

|          |         |          |            |            |            |            |            |            |            |            |              |

### 3.2 Task 4

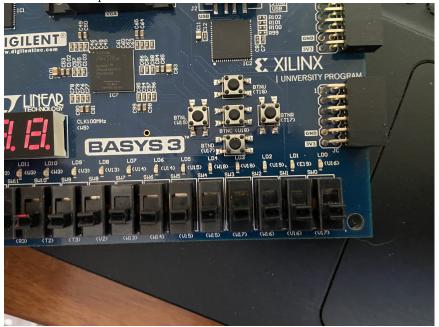

14.1 FPGA Output 00000

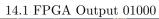

14.1 FPGA Output 00010

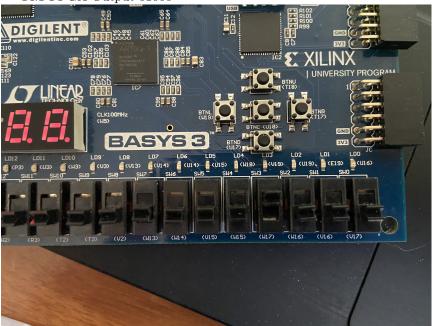

14.1 FPGA Output 00100

$14.1 \ \mathrm{FPGA} \ \mathrm{Output} \ 10010$

$14.1~{\rm FPGA~Output~10100}$

```

14.2 Code

1 timescale 1ns/1ps

2

3 module digitalSafe_top(sw,led);

4 input [3:0] sw;

5 output [1:0] led;

6 digitalSafe UUT(.1(led),.s(sw));

7 endmodule

7 assign 1[0] = ~(s[0]^p[0]) & ~(s[1]^p[1]) & ~(s[2]^p[2]) & ~(s[3]^p[3]);

8 assign 1[1] = ~l[0];

9 endmodule

```

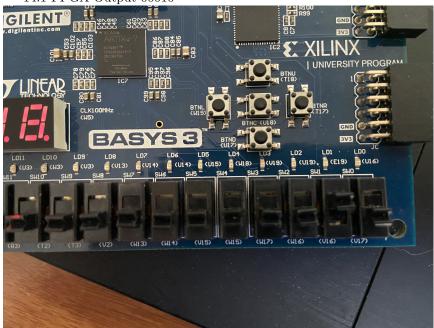

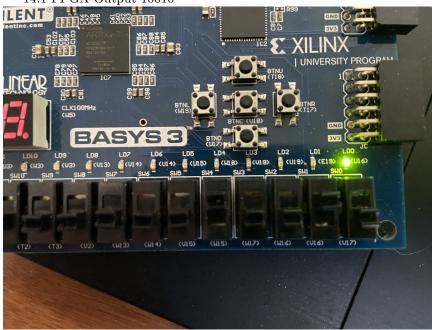

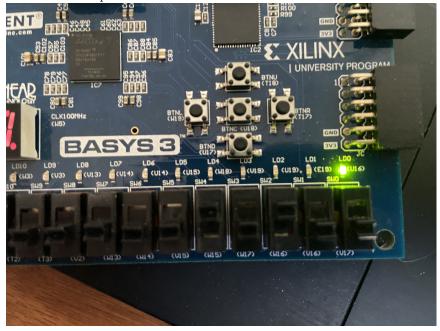

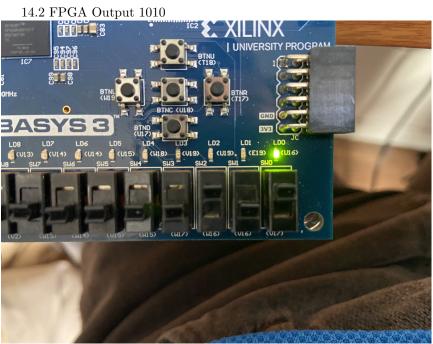

### $14.2 \ \mathrm{FPGA} \ \mathrm{Output} \ 0000$

# 14.3 Code 1 timescale 1ns/1ps 2 ///////////////////////// 3 module parkingCount\_top(sw,led); 4 input[2:0] sw; 5 output [1:0] led; 6 parkingCount UUT(.c(led),.s(sw)); 7 endmodule

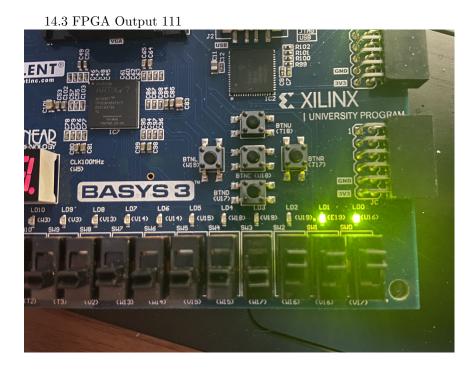

### 14.3 FPGA Output 000

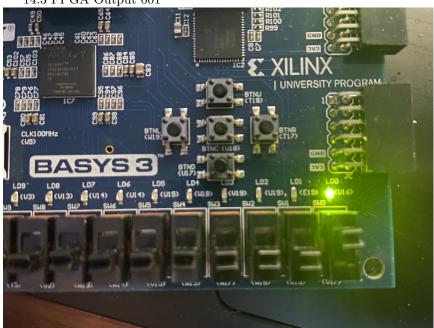

$14.3~{\rm FPGA~Output~001}$

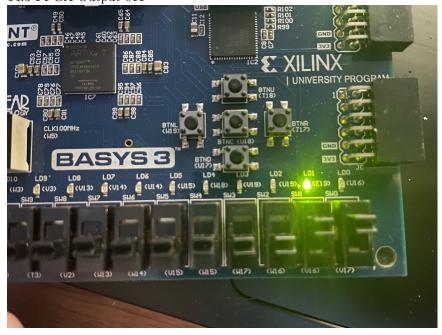

14.3 FPGA Output 011

## 4 Discussion

All of this was fairly simple just to follow your tutorial. I now understand the difference between [0:7] and [7:0] and I am feeling confident in my ability. 41.1 would light up if bit 5 and any other bit was high. 14.2 would have led 2 lit if it was anything besides 1010. 14.3 could give the bit sequence of how many of the 3 switches were high regardless of the sequence.

Task 1

0000 2000 0000 0000 0000 0000

1000 0000 0010 0110 0010 0000 0000

1000 0000 0011 0010 1010 0000 0000 0000

0 01100 001000011 0 10000 110 1000000

1 10010 (110)00000

Task 2

0000 1111,0100

+ 0000 0100 .00 lo

\_\_11.125

01001101 0000 10110010 19, 375

7 1111 1011.1110

0000 1111,0100