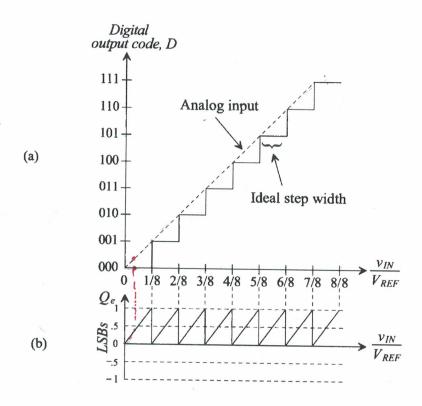

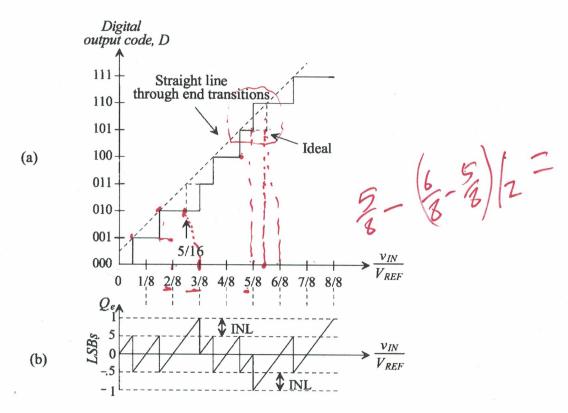

Examine Fig. 28.19a. The digital output, D, of an ideal, 3-bit ADC is plotted versus the analog input,  $v_{IN}$ . Note the difference in the transfer curve for the ADC versus the DAC (Fig. 28.10). The y-axis is now the digital output, and the x-axis has been normalized to  $V_{REF}$ . Since the input signal is a continuous signal and the output is discrete, the transfer curve of the ADC resembles that of a staircase. Another fact to observe is that the  $2^N$  quantization levels correspond to the digital output codes 0 to 7. Thus, the maximum output of the ADC will be  $111 (2^N - 1)$ , corresponding to the value for which  $\frac{v_{IN}}{v_{REF}} \ge \frac{7}{8}$ . Figure 28.19b corresponds to the error caused by the quantization.

Figure 28.19 (a) Transfer curve for an ideal ADC and (b) its corresponding quantization error.

The value of 1 LSB for this ADC can be calculated using Eq. (28.9) and is the ideal step width (1/8) in Fig. 28.19 (versus the height for the DAC) multiplied by  $V_{REF}$ . Therefore, assuming that  $V_{REF} = 5 \text{ V}$ ,

$$1 LSB = 0.625 V (28.17) .$$

## Quantization Error

Since the analog input is an infinite valued quantity and the output is a discrete value, an error will be produced as a result of the quantization. This error, known as quantization error,  $Q_e$ , is defined as the difference between the actual analog input and the value of the output (staircase) given in voltage. It is calculated as

$$Q_e = v_{IN} - V_{staircase}$$

(28.18)

where the value of the staircase output,  $V_{staircase}$ , can be calculated by

$$V_{staircase} = D \cdot \frac{V_{REF}}{2^N} = D \cdot V_{LSB}$$

(28.19)

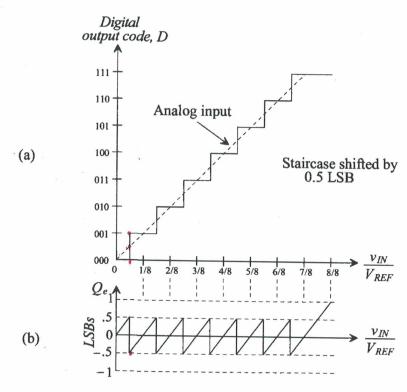

where D is the value of the digital output code and  $V_{LSB}$  is the value of 1 LSB in volts, in this case 0.625 V. We can also easily convert the value of  $Q_e$  in units of LSBs. In Fig. 28.19a,  $Q_e$  can be generated by subtracting the value of the staircase from the dashed line. The result can be seen in Fig. 28.19b. A sawtooth waveform is formed centered about ½ LSBs. Ideally, the magnitude of  $Q_e$  will be no greater than one LSB and no less than 0. It would be advantageous if the quantization error were centered about zero so that the error would be at most  $\pm \frac{1}{2}$  LSBs (as opposed to  $\pm \frac{1}{2}$  LSB). This is easily achieved as seen in Fig. 28.20a and b. Here, the entire transfer curve is shifted to the left by ½ LSB, thus making the codes centered around the LSB increments on the x-axis. This drawing illustrates that at best, an ideal ADC will have quantization error of  $\pm \frac{1}{2}$  LSB.

Figure 28.20 (a) Transfer curve for an ideal 3-bit ADC with (b) quantization error centered about zero.

In shifting this curve to the left, notice that the first code transition occurs when  $\frac{v_{IN}}{V_{REF}} \ge \frac{1}{16}$ . Therefore, the range of  $\frac{v_{IN}}{V_{REF}}$  for the digital output corresponding to 000 is half as wide as the ideal step width. The last code transition occurs when  $\frac{v_{IN}}{V_{REF}} \ge \frac{13}{16}$  (between 6/8 and 7/8). Note that the step width corresponding to this last code transition is 1.5 times larger than the ideal width and that the quantization error extends up to 1 LSB when  $\frac{v_{IN}}{V_{REF}} = 1$ . However, the converter would be considered to be out of range once  $\frac{v_{IN}}{V_{REF}} \ge \frac{15}{16}$  (halfway between 7/8 and 8/8), so the problem is moot.

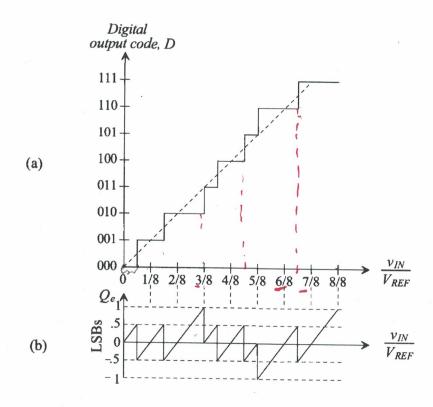

## Differential Nonlinearity

Differential nonlinearity for an ADC is similar to that defined for a DAC. However, for the ADC, DNL is the difference between the actual code width of a nonideal converter and the ideal case. Figure 28.21 illustrates the transfer curve for a nonideal 3-bit ADC. The values for the DNL can be solved as follows:

$$DNL = Actual step width - Ideal step width$$

(28.20)

Since the step widths can be converted to either volts for LSBs, DNL can be defined using either units. The value of the ideal step is 1/8. Converting to volts, this becomes

$$V_{idealstepwidth} = \frac{1}{8} \cdot V_{REF} = 0.625 \ V = 1 \ LSB$$

(28.21)

Figure 28.21 (a) Transfer curve for a nonideal 3-bit ADC used in Ex. 28.4 with (b) quantization error illustrating differential nonlinearity.

#### Example 28.6

Using Fig. 28.21a, calculate the differential nonlinearity of the 3-bit ADC. Assume that  $V_{REF} = 5$  V. Draw the quantization error,  $Q_e$ , in units of LSBs.

The DNL of the converter can be calculated by examining the step width of each digital output code. Since the ideal step width of the 000 transition is  $\frac{1}{2}$  LSB, then DNL<sub>0</sub> = 0. Also note that the step widths associated with 001 and 100 are equal to 1 LSB; therefore, both DNL<sub>1</sub> and DNL<sub>4</sub> are zero. However, the remaining values code widths are not equal to the ideal value but can be calculated as

The overall DNL for the converter used in this illustration is  $\pm 0.5$  LSB. Note that the quantization error illustrated in Fig. 28.21b is directly related to the DNL. As DNL increases in either direction, the quantization error worsens. Each "tooth" in the quantization error waveform should ideally be the same size.

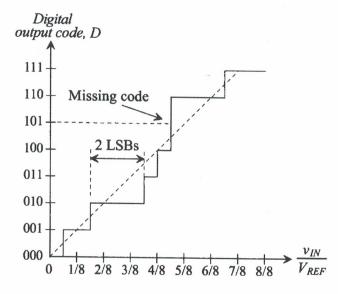

## Missing Codes

It is of interest to note the consequences of having a DNL that is equal to -1 LSB. Figure 28.22 illustrates an ADC for which this is true. The total width of the step corresponding to 101 is completely missing; thus, the value of DNL<sub>5</sub> is -1 LSB. Any ADC possessing a DNL that is equal to -1 LSB is guaranteed to have a missing code. Notice that the step width corresponding to 010 is 2 LSBs and that the value for DNL<sub>2</sub> is +1 LSB. However, there is not a missing code corresponding to 011, since the step width of code 011 depends on the 100 transition. Therefore, an ADC having a DNL greater than +1 LSB is not guaranteed to have a missing code, though in all probability a missing code will occur.

Figure 28.22 Transfer curve for a nonideal 3-bit ADC with a missing code.

#### Integral Nonlinearity

Integral nonlinearity (INL) is defined similarly to that for a DAC. Again, a "best-fit" straight line is drawn through the end points of the first and last code transition, with INL being defined as the difference between the data converter code transition points and the straight line with all other errors set to zero.

### Example 28.7

Determine the INL for the ADC whose transfer curve is illustrated in Fig. 28.23a. Assume that  $V_{REF} = 5$  V. Draw the quantization error,  $Q_e$ , in units of LSBs.

Figure 28.23 (a) Transfer curve of a nonideal 3-bit ADC and (b) its quantization error illustrating INL.

By inspection, it can be seen that all of the transition points occur on the best-fit line except for the transitions associated with code 011 and 110. Therefore,

$$INL_0 = INL_1 = INL_2 = INL_4 = INL_5 = INL_7 = 0$$

The INL corresponding to the remaining codes can be calculated as

$$INL_3 = 3/8 - 5/16 = 1/16$$

or 0.5 LSB

Similarly,  $INL_6$  can be calculated in the same manner and is found to be -0.5 LSB. Thus, the overall INL for the converter is the maximum value of INL corresponding to  $\pm 0.5$  LSB.

The INL can also be determined by inspecting the quantization error in Fig. 28.23b. Here, the INL will be the magnitude of the quantization error which lies outside the  $\pm \frac{1}{2}$  LSB band of  $Q_e$ . It can be seen that  $Q_e = 1$  LSB, corresponding to the point at which INL = 0.5 LSB for digital output code 011, and that  $Q_e = -1$  LSB at the output code corresponding to INL = -0.5 LSB for digital output code 110.

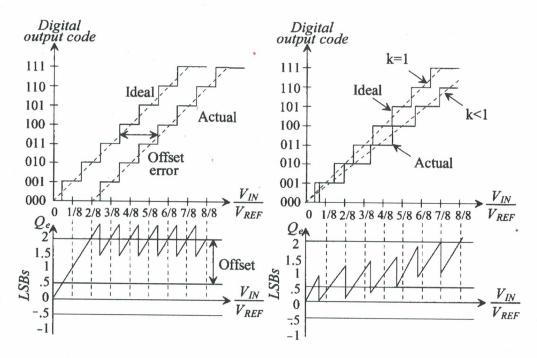

# Offset and Gain Error

Offset and gain error are identical to the DAC case. Offset error occurs when there is a difference between the value of the first code transition and the ideal value of ½ LSBs. As seen in Fig. 28.24a, the offset error is a constant value. Note that the quantization error becomes ideal after the initial offset voltage is overcome. Gain error or scale factor error, seen in Fig. 28.24b, is the difference in the slope of a straight line drawn through the transfer characteristic and the slope of 1 of an ideal ADC. Causes of offset and gain error are discussed in Ch. 29, but it is important here to understand their overall effects on ADC transfer curves.

Figure 28.24 Transfer curve illustrating (a) offset error and (b) gain error.

So far, we have examined only the DC characteristics of an ADC. However, examining the dynamic aspects of the converter will lead to a whole new set of errors. Sampling is inherently a dynamic process since the accuracy of the sample is dependent on the speed of the analog signal. Many effects that occur during sampling limit the overall performance of the converter.

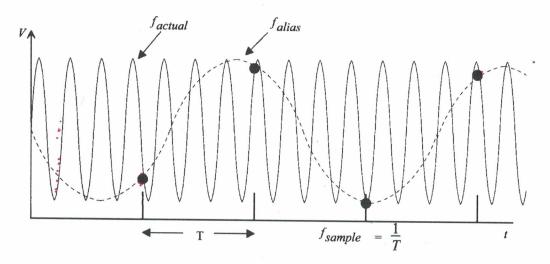

### Aliasing

As mentioned earlier in the chapter, the Nyquist Criterion requires that a signal be sampled at least two times the highest frequency contained in the signal. What would happen if this criterion were ignored and the sampling rate was actually less than that amount? A phenomenon known as aliasing would occur.

Examine Fig. 28.25. Here, an analog signal is being sampled at a rate slower than the Nyquist Criterion requires. As a result, it appears that a totally different signal (see

Figure 28.25 Aliasing caused by undersampling.

example dashed line) is being sampled. The different frequency signal is an "alias" of the original signal, and its frequency can be calculated using

$$f_{alias} = f_{actual} + k f_{sample} \quad (k = ... -2, -1, 0, 1, 2, 3...)$$

(28.22)

$f_{alias} = f_{actual} + k f_{sample} \quad (k = ... - 2, -1, 0, 1, 2, 3...)$  (28.22) where  $f_{actual}$  is the frequency of the analog signal,  $f_{sample}$  is the sampling frequency, and  $f_{alias}$ is the frequency of the alias signal.

Aliasing can be eliminated by both sampling at higher frequencies and by filtering the analog signal before sampling and removing any frequencies that are greater than one-half the sampling frequency. It is good practice to filter the analog signal before sampling to eliminate any unknown higher order frequency components or noise that could result in aliasing.

A frequency domain analysis may further illustrate the concepts of aliasing. Figure 28.26 shows the analog signal, the sampling function (represented by a unit impulse train) and the resulting sampled signal in both the time and frequency domains. The analog signal in Fig. 28.26a is represented as a simple band-limited signal with center frequency, f<sub>o</sub>. This simply means that the signal is contained within the frequency range shown. In Fig. 28.26b, the sampling function is shown in both the time and frequency domain. The sampling function simply represents the action of sampling at discrete points in time. The frequency domain version of the sampling function is similar to its time domain counterpart, except that the x-axis is now represented as f = 1/T. Since each of the impulses has a value of 1, the resulting sampled signal shown in Fig. 28.26c is the impulse function multiplied by the amplitude of the analog signal at each discrete point in time. Remembering that multiplication in the time domain is equivalent to convolution in the frequency domain, we note that the frequency domain representation of the sampled signal reveals that the overall signal consists of multiple versions of the band-limited signal at multiples of the sampling frequency.

Note in Fig. 28.26b that as the sampling time increases, the sampling frequency decreases and the impulses in the frequency domain become more closely spaced. This results in 28.26d, which illustrates the aliasing as the multiple versions of the