## On the Design of Low Power CMOS (SA-ADCs) for Biomedical Applications

# On The Design of Low Power CMOS (SA-ADCs) for Biomedical Applications

# Ву

# TASNIM BASSAM SAMI NAZZAL

## **University of Sharjah**

College of Engineering

Department of Electrical and Computer Engineering

## Supervisor

## Prof. Dr. Soliman Mahmoud

Program: Master of Science in Electrical and Electronics Engineering

March 2016

# On The Design of Low Power CMOS (SA-ADCs) for Biomedical Applications

## By

## TASNIM BASSAM SAMI NAZZAL

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in the Department of Electrical and Computer Engineering,

University of Sharjah

## Approved by:

| Dr. Soliman Mahmoud (Thesis Supervisor)                                      | Chairman |

|------------------------------------------------------------------------------|----------|

| Associate Professor of Electrical and Electronics Engineering, University of | Sharjah  |

|                                                                              |          |

|                                                                              |          |

| Dr. Lutfi Al Basha (External Examiner)                                       | Member   |

| Associate Professor of Electrical Engineering, American University of Sh     | narjah   |

|                                                                              |          |

|                                                                              |          |

| Dr. Sohaib Majzoub (Internal Examiner)                                       | Member   |

| Assistant Professor of Electrical and Electronics Engineering, University of | Sharjah  |

## UNIVERSITY OF SHARJAH

| Author:               | Tasnim Bassam Sami Nazzal                                                  |

|-----------------------|----------------------------------------------------------------------------|

| Thesis Title:         | On The Design of Low Power CMOS (SA-ADCs) for                              |

|                       | Biomedical Applications                                                    |

| Department:           | Electrical and Computer Engineering                                        |

| Degree:               | M.Sc.                                                                      |

| Defense Date:         | 24 March 2016                                                              |

|                       |                                                                            |

|                       |                                                                            |

| Permission            | is herewith granted to the University of Sharjah to circulate and to have  |

| copies for non-com    | imercial purposes, and its discretion, the above title upon the request of |

| individuals or instit | utions.                                                                    |

|                       |                                                                            |

|                       |                                                                            |

|                       | Signature of Author                                                        |

## **Abstract**

SUCCESSIVE APPROXIMATATION analog-to-digital converter (SA-ADC) is one of the most popular approaches for realizing A/D converters, due to its reasonably quick conversion time, moderate circuit complexity, high accuracy, and it's a proper choice for low power applications. Thus, one of the main challenges in designing SA-ADC is to succeed in proposing a low power, simple and accurate design.

This thesis presents three different CMOS realizations of an 8-bit successive approximation analog to digital converter (SA-ADC) for biomedical applications. The architecture of the proposed SA-ADCs consists of a sample and hold (S/H), a comparator, a successive approximation register (SAR) controller, and an 8-bit digital-to-analog converter (DAC). The proposed realizations are implemented using the same S/H circuit which is based on a sampling transistor with dummy switch, the choice of static or dynamic comparator, the choice of conventional or clock gated SAR, and the same binary weighted capacitor array single ended DAC based SAR architecture. In addition to that, the SAR controller is implemented using D-flip flop (D-FF) or hybrid latch-flip flop (HL-FF). The proposed SA-ADCs are presented, compared and simulated using 90nm CMOS technology file on LT-spice-IV.

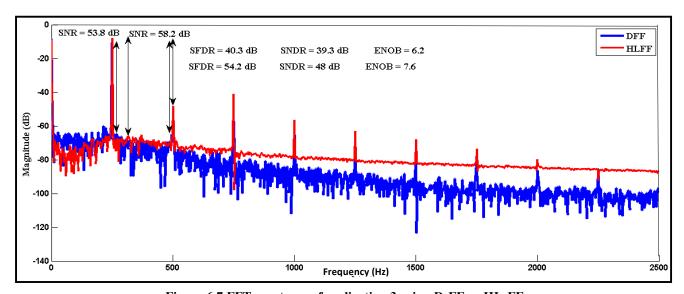

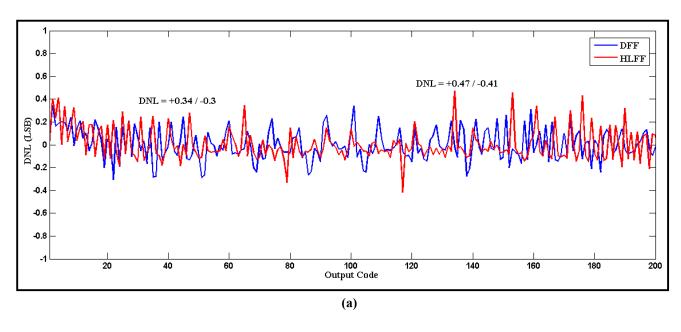

The simulation results show that the SA-ADC realization which implemented by using the double-tail dynamic latched comparator and the clock-gated D-FF based SAR is superior from point of view of the power consumption. According to the simulation results, the low-power clock gated SA-ADC using D-FF realization consumes 200nW from 1V power supply without additional calibration or analog circuits. It has signal-to-noise ratio (SNR) of 53.8 dB, peak spurious-free dynamic range (SFDR) of 54.2 dB, and a signal-to-noise-and distortion ratio (SNDR) of 48 dB for a 250Hz full scale input sine wave. It has also an effective number of bits (ENOB) of 7.6-bits, and a figure of merit (FOM<sub>2</sub>) of 0.1 pJ/Conversion-step. It achieves +0.34/-0.3 LSB and +0.79/-0.58 LSB of Differential non-linearity (DNL) and Integral non-linearity (INL) errors respectively.

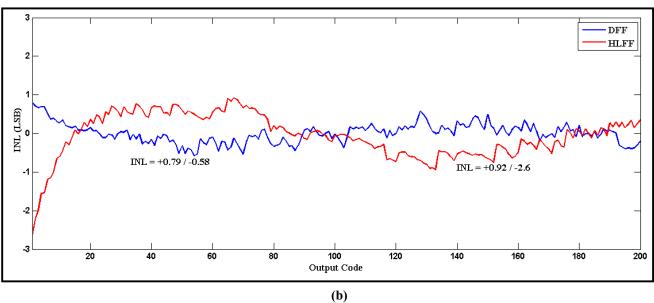

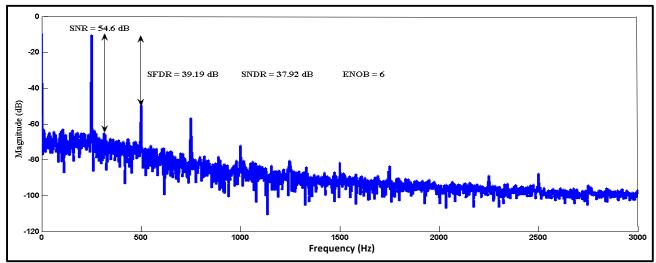

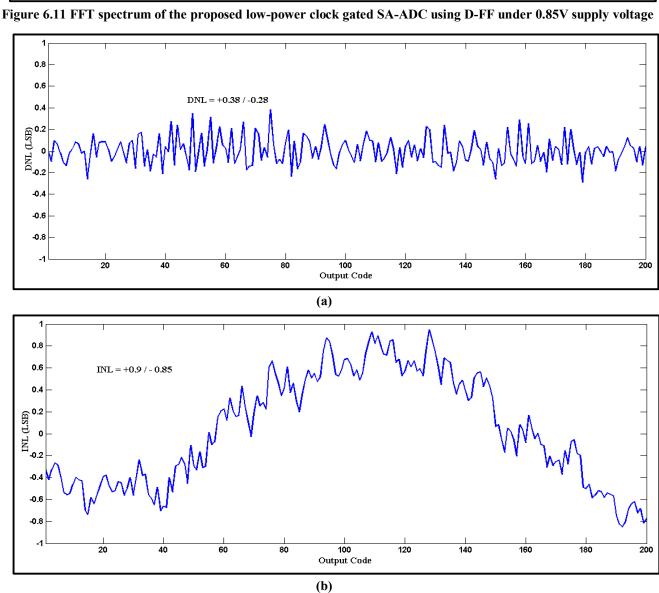

Furthermore, the low-power clock gated SA-ADC using D-FF realization consumes 88.76 nW from 0.85V power supply without additional calibration or analog circuits. It has SNR, SFDR and SNDR of 54.6 dB, 39.19 dB and 37.92 dB respectively for the same input sinewave. It achieves ENOB of 6-bits with (FOM<sub>2</sub>) of 0.13 pJ/Conversion-step. It has DNL and INL of +0.38/-0.28 LSB and +0.9/-0.85 LSB respectively.

## Acknowledgment

First of all, I would like to express my deepest gratitude to our benevolent god, for bestowing upon me his grace and granting me the ability, the strength and the patience to complete my thesis after all the challenges and difficulties.

I take this opportunity to thank my supervisor Prof. Soliman Mahmoud, whose guidance has been instrumental in me having successfully presented this thesis and for his support through whole master study. I do sincerely thank Dr. Mohamed Shaker for the continuous support extended to me for solving some of the problems I faced in my thesis. I am also truly grateful to my committee members, Dr. Sohaib Majzoub and Dr. Lutfi Al Basha for their insightful suggestions and comments on my thesis.

I am indebted to my parents, Bassam and Hind, for their belief in my convictions, their patience, and for having provided me with all the necessary resources enabling me to achieve my goals. It was impossible for me to reach this level without their continued prayers. I sincerely thank my lovely sisters Saja, Hala and Aya with her husband Wasim and their daughter Sana who have been my mentor and source of inspiration in this project and for their continuous support. I would like to give my special thanks to my grandmother for her prayers which enabled me to complete my thesis. My sincere appreciation also goes to my uncle Basel for his care and continuous supports.

I would like to express my sincere gratitude to all my friends for the nice days I spent with them during my study and work period. Special thanks to Eng. Mohamed Buhatier for helping me in the MATLAB part of my thesis.

# **Table of Contents**

| Chapte | er 1 Introduction                                                        | 1                   |

|--------|--------------------------------------------------------------------------|---------------------|

| 1.1    | Thesis Motivation                                                        | 1                   |

| 1.2    | Thesis Objectives                                                        | 2                   |

| 1.3    | Thesis Contribution                                                      | 3                   |

| 1.4    | Thesis Organization                                                      | 5                   |

| Chapte | er 2 Sample and Hold Circuits                                            | 6                   |

| 2.1 I  | Introduction                                                             | 6                   |

| 2.2 E  | Basic Sample and Hold Circuit                                            | 7                   |

| 2      | 2.1 Differential Basic Sample and Hold Circuit                           | 10                  |

| 2      | 2.2 Basic Sample and Hold Circuit with Dummy Switch                      | 13                  |

| 2      | 2.3 Basic Sample and Hold Circuit using Transmission Gate                | 14                  |

| 2.3 S  | Sample and Hold Circuits with Bootstrapped Technique                     | 15                  |

| 2      | 3.1 Sample and Hold Circuit with Boosted Driver Technique                | 15                  |

| 2      | 3.2 Sample and Hold Circuit with Bootstrapped Technique                  | 18                  |

| 2.4 F  | Proposed Modified Low-Power Bootstrapped Sample and Hold Circuit using T | ransmission Gate 23 |

| 2.5 \$ | Simulation Results                                                       | 25                  |

| Chapte | er 3 Comparator Circuits                                                 | 28                  |

| 3.1 I  | Introduction                                                             | 28                  |

| 3.2 S  | Static Comparators                                                       | 30                  |

| 3.3 I  | Dynamic Comparators                                                      | 35                  |

| 3      | 3.1 Dynamic Comparator with a Cross-Coupled Transistors                  | 35                  |

| 3      | 3.2 Dynamic Latched Comparator using Back-to-Back inverters              | 39                  |

| Chapte | er 4 Digital-to-Analog Converter                                         | 46                  |

| 4.1 I  | Introduction                                                             | 46                  |

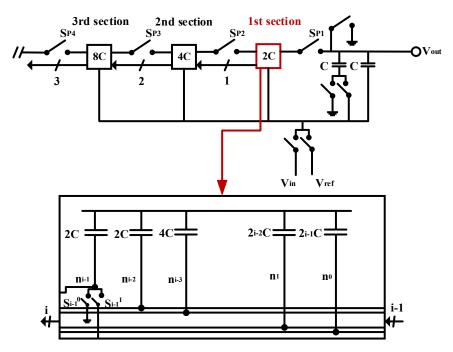

| 4.2 E  | Binary Weighted Switched Capacitor Array DAC                             | 47                  |

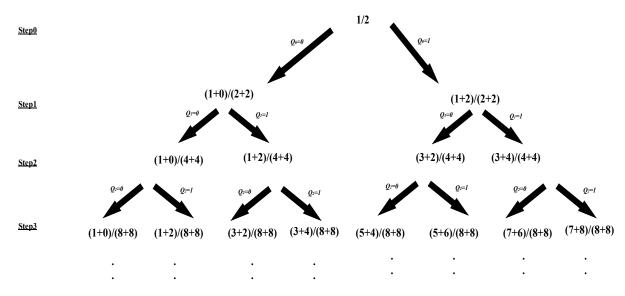

| 4.2 S  | Serial Charge Redistribution D/A Converter                               | 49                  |

| 4.3 J  | Junction-Splitting Capacitor Array                                       | 52                  |

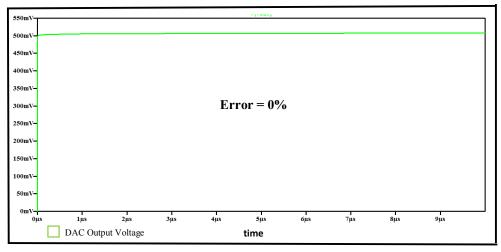

| 445    | Simulation Results                                                       | 54                  |

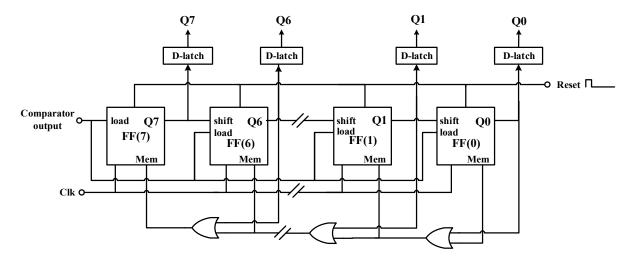

| Chapter 5 Successive Approximation Register                                         | 56    |

|-------------------------------------------------------------------------------------|-------|

| 5.1 Introduction                                                                    | 56    |

| 5.2 Conventional SAR                                                                | 57    |

| 5.3 Clock Gated SAR                                                                 | 61    |

| 5.4 Simulation Results                                                              | 64    |

| Chapter 6 SA-ADC Realizations                                                       | 69    |

| 6.1 Introduction                                                                    | 69    |

| 6.2 8-Bit CMOS SA-ADC Realizations                                                  | 70    |

| 6.3 Simulation Results                                                              | 74    |

| Chapter 7 Conclusion                                                                | 87    |

| 7.1 Conclusion of the Chapters                                                      | 88    |

| 7.2 Future Work                                                                     | 89    |

| References                                                                          | 90    |

| List of Published and Under Review Papers from the Master Thesis                    | 93    |

| Appendix A Derivations of the Dynamic Performance Metrics (SNR and ENOB) for Ideal  | ADC94 |

| Appendix B Matlab Code for Static Performance Metrics (DNL and INL) Calculations    | 95    |

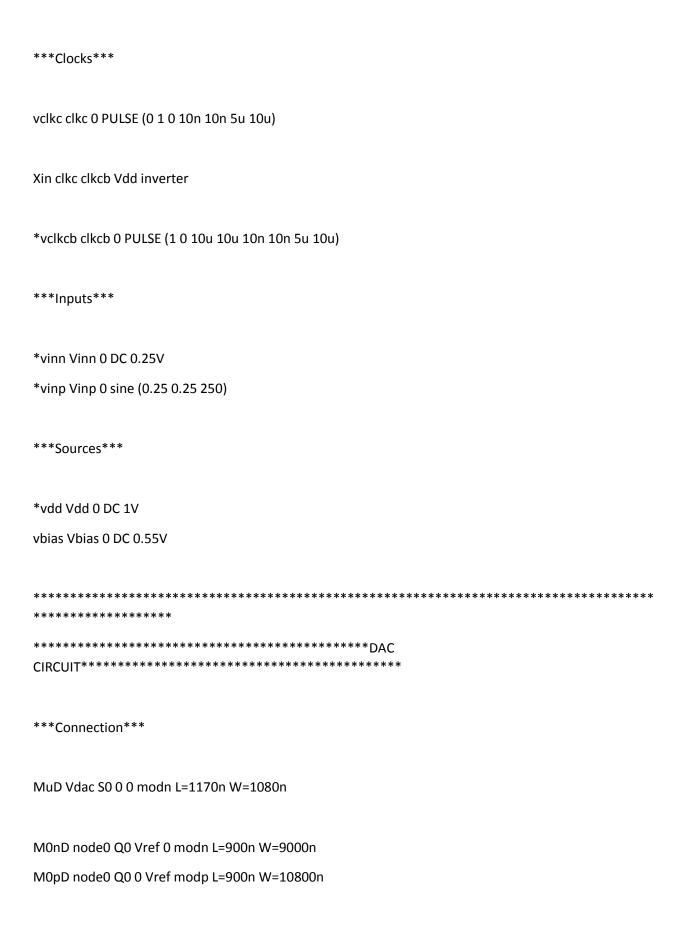

| Appendix C Netlist Code for Low-Power Clock Gated SA-ADC (Realization 3 using D-FF) | 97    |

# **List of Figures**

| Figure 1.1 Block diagram of a single ended DAC based SAR ADC architecture          | 3  |

|------------------------------------------------------------------------------------|----|

| Figure 2.1 Basic sample and hold circuit                                           | 8  |

| Figure 2.2 Sampled output Voltage (Vout,sampled) with sampling frequency of 10 KHz | 8  |

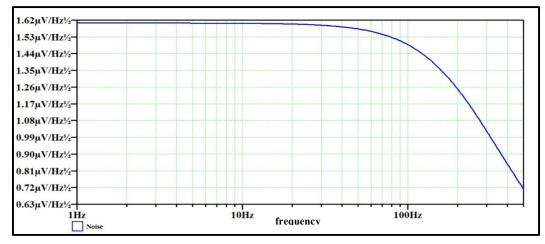

| Figure 2.3 Noise spectrum of (V <sub>out,sampled</sub> ) over bandwidth of 500 Hz. | 8  |

| Figure 2.4 Differential basic sample and hold circuit.                             | 10 |

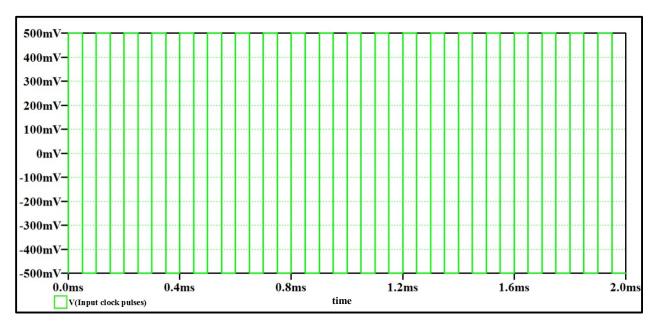

| Figure 2.5 Input clock pulses (Ø).                                                 | 11 |

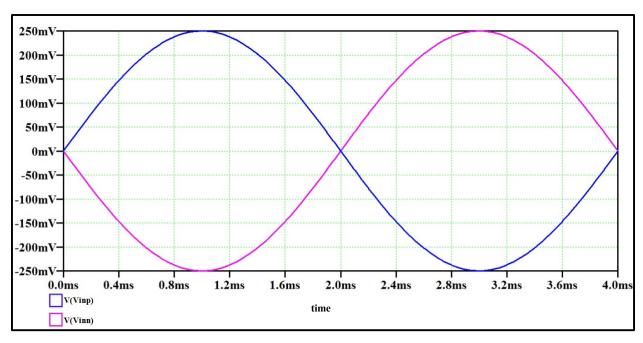

| Figure 2.6 Differential balanced input.                                            | 11 |

| Figure 2.7 Differential output.                                                    | 12 |

| Figure 2.8 Noise spectrum of differential output over bandwidth of 500 Hz.         | 12 |

| Figure 2.9 Basic sample and hold circuit with dummy switch.                        | 13 |

| Figure 2.10 Basic sample and hold circuit using transmission gate.                 | 14 |

| Figure 2.11 Sample and hold circuit using transmission gate with boosted driver    | 16 |

| Figure 2.12 Input clock pulses (Ø)                                                 | 17 |

| Figure 2.13 Zoomed (V <sub>out,sampled</sub> ) with inverted boosted clock         | 17 |

| Figure 2.14 Bootstrapped MOS switch.                                               | 20 |

| Figure 2.15 Sample and hold with bootstrapped circuit technique.                   | 20 |

| Figure 2.16 Cross coupled capacitors.                                              | 20 |

| Figure 2.17 Input clock pulses (Ø).                                                | 21 |

| Figure 2.18 Input signal with the clock pulses formed on G.                        | 21 |

| Figure 2.19 Zoomed (V <sub>out,sampled</sub> ) with the clock pulses formed on G   | 21 |

| Figure 2.20 Sample and hold circuit with power scalable ON/OFF technique           | 22 |

| Figure 2.21 Proposed modified low-power bootstrapped S/H circuit using transmission gate        | 24 |

|-------------------------------------------------------------------------------------------------|----|

| Figure 2.22 FFT spectrum of (V <sub>out,sampled</sub> ) for the basic S/H circuit.              | 26 |

| Figure 3.1a Differential comparator symbol.                                                     | 29 |

| Figure 3.1b Transfer curve of ideal comparator.                                                 | 29 |

| Figure 3.1c Transfer curve of real comparator with finite gain.                                 | 29 |

| Figure 3.2 Static comparator with cross-coupled transistors.                                    | 31 |

| Figure 3.3 Static comparator output when vin- = 0.25 V at speed of 80 KHz                       | 31 |

| Figure 3.4 Zoomed static comparator output.                                                     | 32 |

| Figure 3.5 Static comparator with rail-to-rail input swing.                                     | 34 |

| Figure 3.6 Dynamic comparator with a cross-coupled transistors                                  | 36 |

| Figure 3.7 Modified dynamic comparator with a current source and a cross-coupled N transistors. |    |

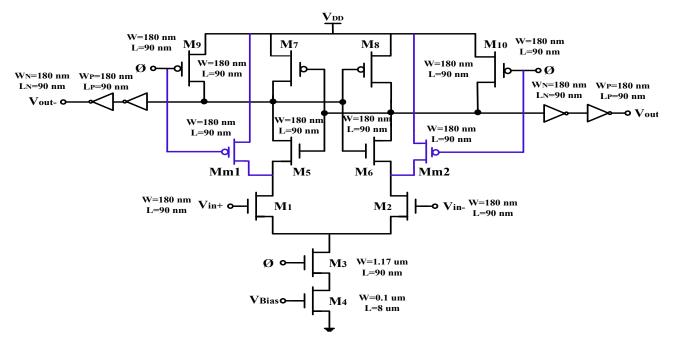

| Figure 3.8 Dynamic latched comparator using back-to-back inverters.                             | 40 |

| Figure 3.9 Modified dynamic latched comparator.                                                 | 42 |

| Figure 3.10 Double-tail dynamic latched comparator.                                             | 44 |

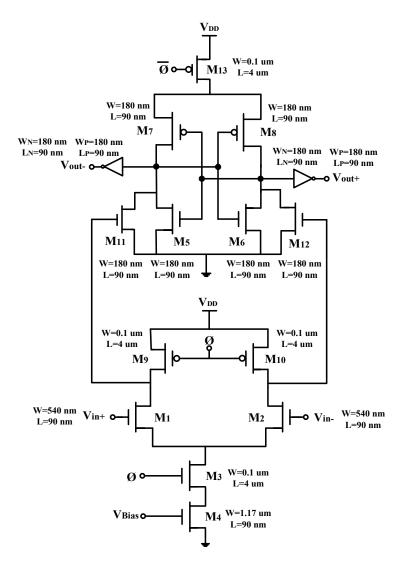

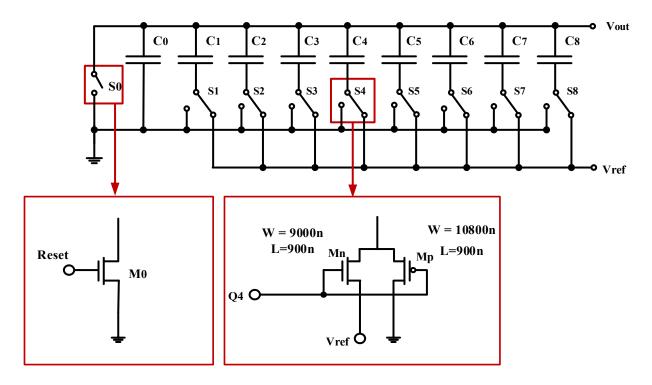

| Figure 4.1 Schematic diagram of binary weighted switched capacitor array DAC                    | 49 |

| Figure 4.2 Schematic diagram of serial charge redistribution DAC.                               | 51 |

| Figure 4.3 Junction splitting capacitor array DAC                                               | 53 |

| Figure 4.4 Method of achieving the desired capacitor ratio for the J-S capacitor array          | 54 |

| Figure 4.5 DAC output voltage for (1000 0000) digital input                                     | 55 |

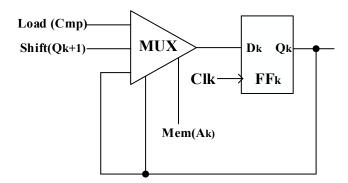

| Figure 5.1 Conventional SAR logic block diagram.                                                | 58 |

| Figure 5.2 Control unit (FF).                                                                   | 58 |

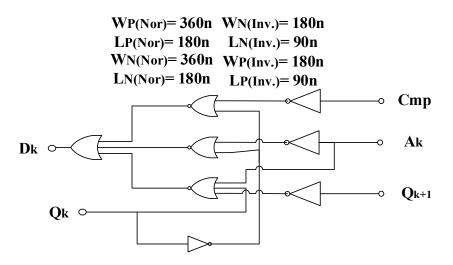

| Figure 5.3 Multiplexer circuit                                                                  | 59 |

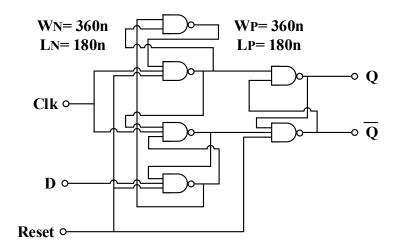

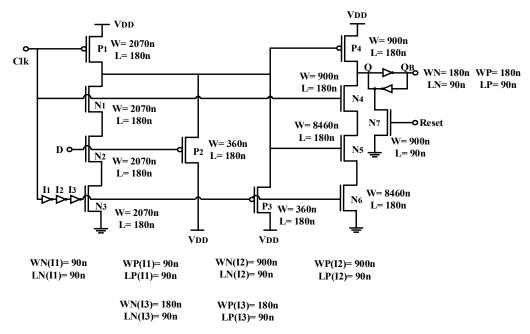

| Figure 5.4 D-FF unit.                                                                              | 59         |

|----------------------------------------------------------------------------------------------------|------------|

| Figure 5.5 HL-FF unit.                                                                             | 60         |

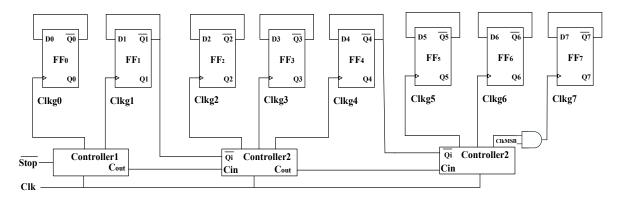

| Figure 5.6 Modified clock gated SAR logic block diagram.                                           | 62         |

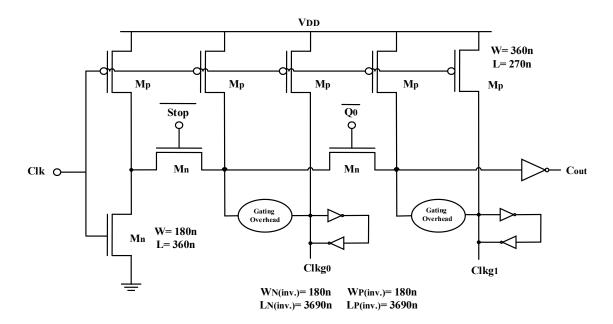

| Figure 5.7 Schematic diagram of controller1                                                        | 62         |

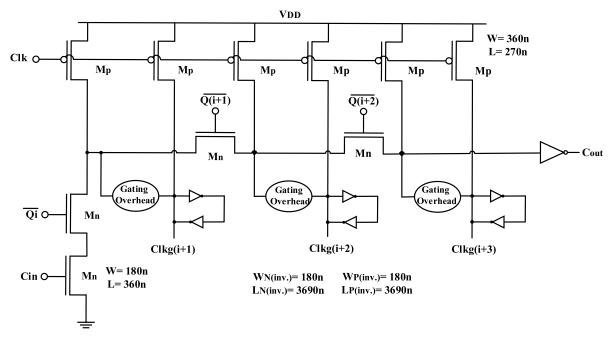

| Figure 5.8 Schematic diagram of controller2                                                        | 63         |

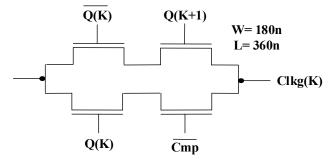

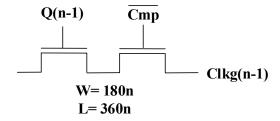

| Figure 5.9 Gating overhead circuit for Clkg(k).                                                    | 63         |

| Figure 5.10 Gating overhead circuit for Clkg(n-1)                                                  | .63        |

| Figure 5.11 Conventional SAR logic outputs when comparator output is 0                             | 65         |

| Figure 5.12 Conventional SAR logic outputs when comparator output is 1                             | 66         |

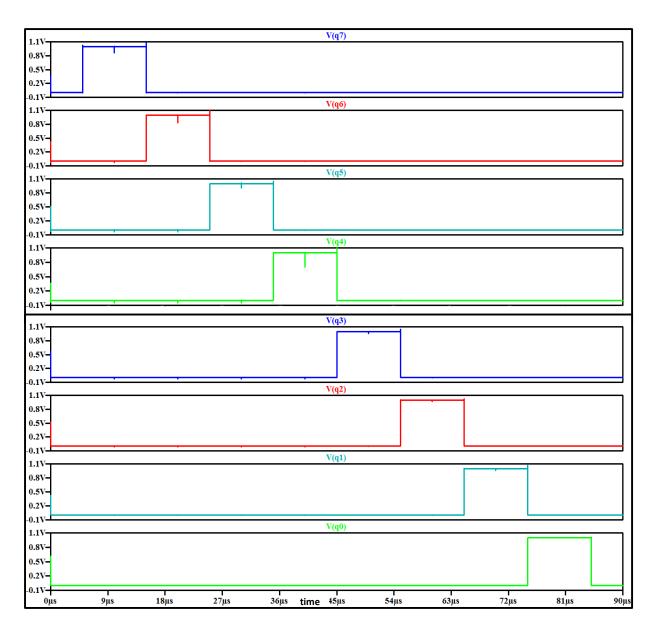

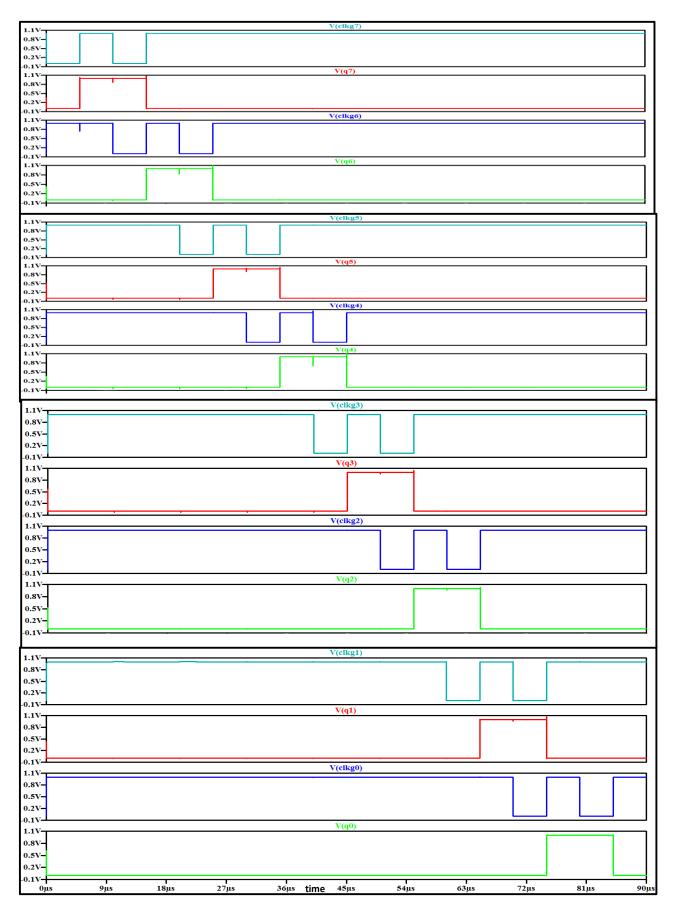

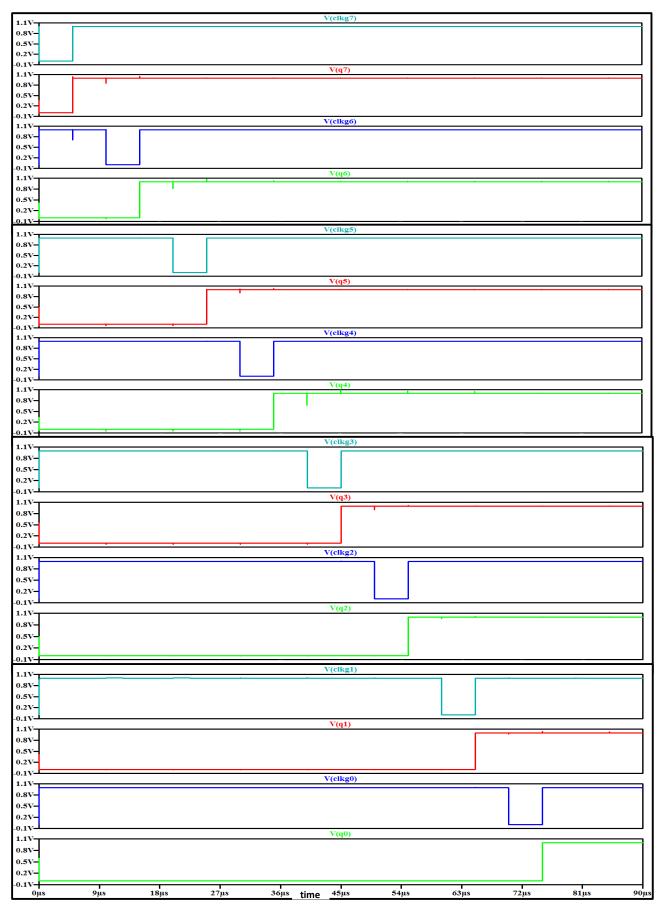

| Figure 5.13 Clock gated SAR logic outputs when comparator output is 0 (worst case)                 | .67        |

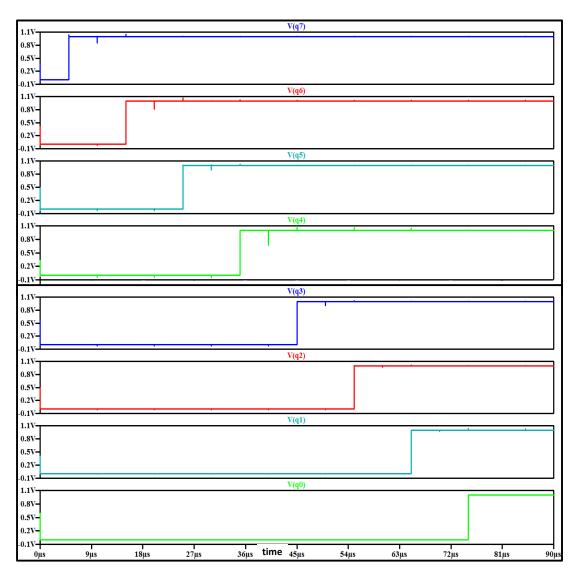

| Figure 5.14 Clock gated SAR logic outputs when comparator output is 1 (best case)                  | .68        |

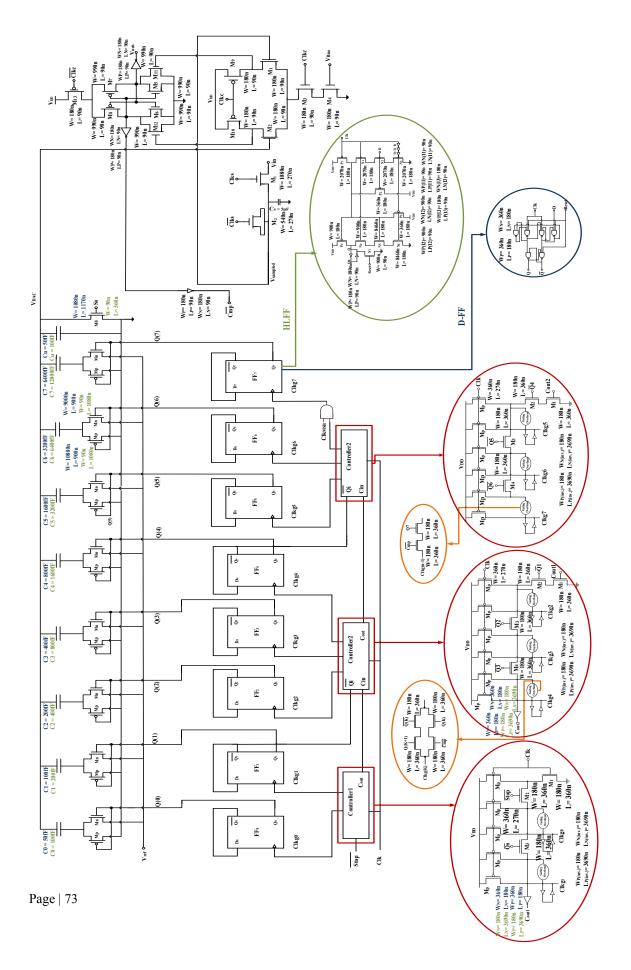

| Figure 6.1 Conventional SA-ADC (realization 1)                                                     | 71         |

| Figure 6.2 Clock gated SA-ADC (realization 2).                                                     | 72         |

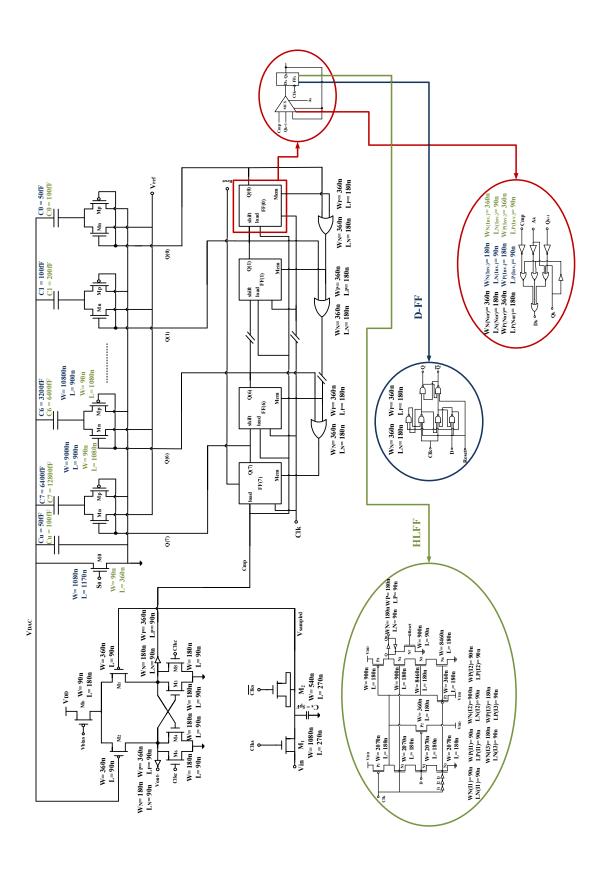

| Figure 6.3 Low-power clock gated SA-ADC (realization3)                                             | 73         |

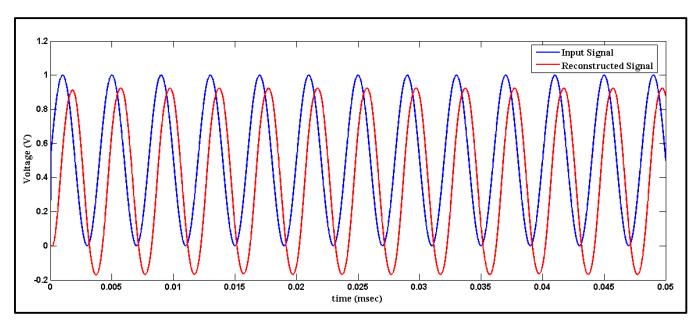

| Figure 6.4 The input sinusoidal signal and the reconstructed signal of realization 1 using D-FF    | F.75       |

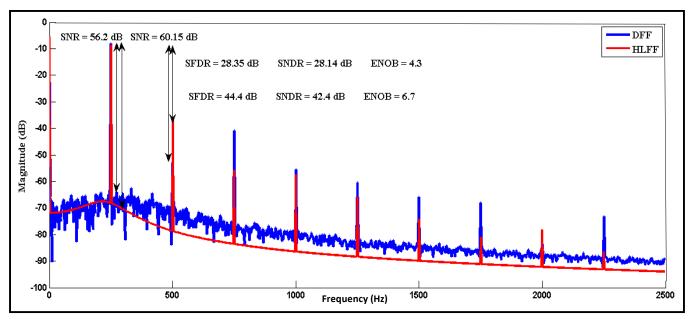

| Figure 6.5 FFT spectrum of realization 1 using D-FF or HL-FF.                                      | 75         |

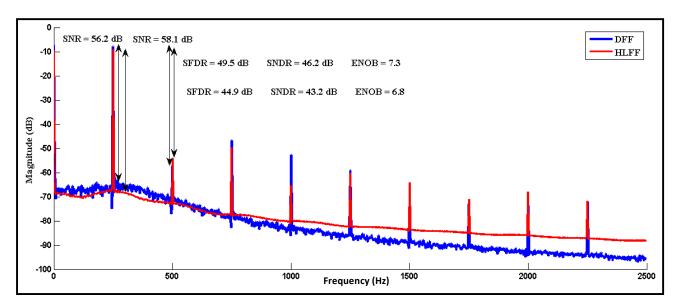

| Figure 6.6 FFT spectrum of realization 2 using D-FF or HL-FF.                                      | 76         |

| Figure 6.7 FFT spectrum of realization 3 using D-FF or HL-FF.                                      | 76         |

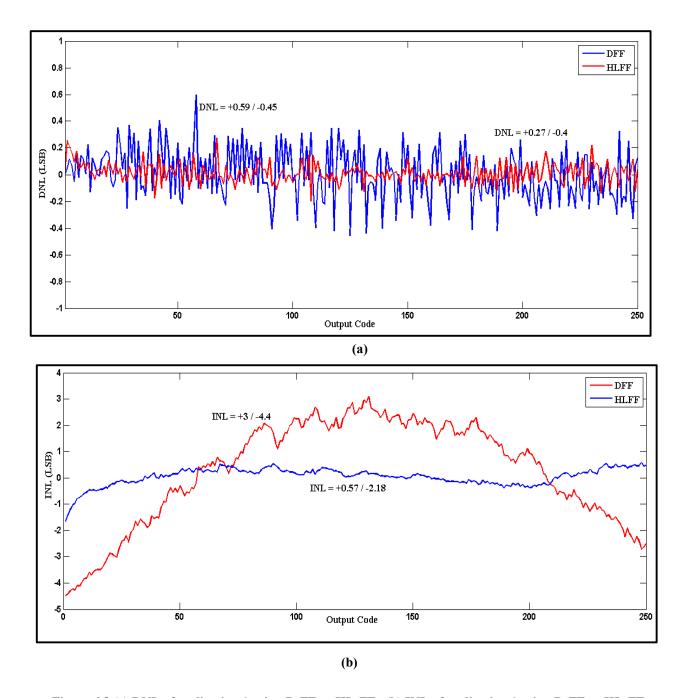

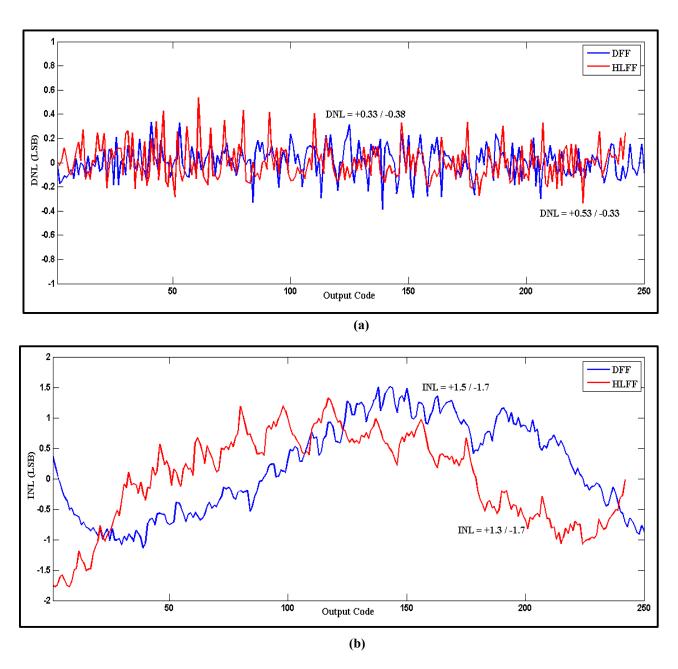

| Figure 6.8 (a) DNL of realization 1 using D-FF or HL-FF (b) INL of realization 1 using D-FF HL-FF. |            |

| Figure 6.9 (a) DNL of realization 2 using D-FF or HL-FF (b) INL of realization 2 using D-FI HL-FF  | F or<br>80 |

| Figure 6.10 (a) DNL of realization 3 using D-FF or HL-FF (b) INL of realization 3 using D-FF HL-                                          | 0  |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| F                                                                                                                                         | 81 |

| Figure 6.11 FFT spectrum of the proposed low-power clock gated SA-ADC using D-FF unco. 85V supply voltage.                                |    |

| Figure 6.12 (a) DNL of realization 3 using D-FF under 0.85V supply voltage (b) INL of realization 3 using D-FF under 0.85V supply voltage |    |

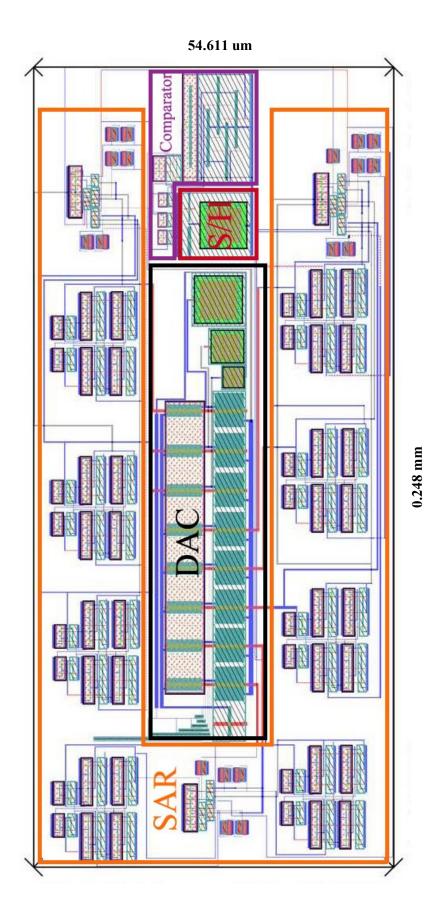

| Figure 6.13 The layout of the proposed 8-bit low-power clock gated SA-ADC using Dealization under 1V supply voltage.                      |    |

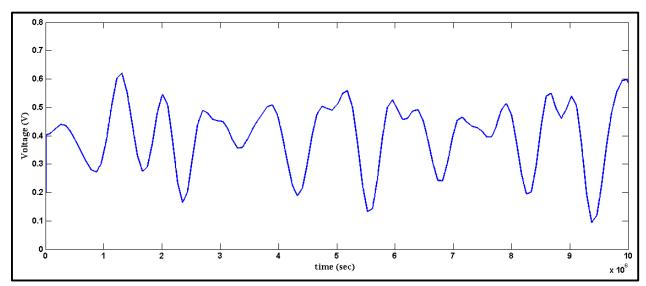

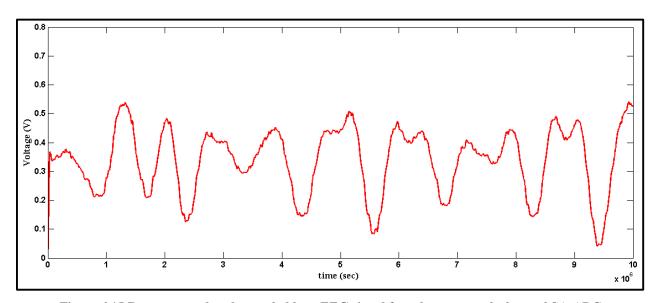

| Figure 6.14 Real recorded input beta EEG signal.                                                                                          | 84 |

| Figure 6.15 Reconstructed real recorded beta EEG signal from low-power clock gated SA-AI using D-FF realization under 1V supply voltage   |    |

# **List of Tables**

| Table 2.1 Simulation results of the presented S/H circuits for different applications                                                                              | 27 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.1 Transistors aspect ratios for static comparator with a cross-coupled transistors for (1 MHz) input frequency signal.                                     | _  |

| Table 3.2 Static comparator simulation results for different applications                                                                                          | 32 |

| Table 3.3 Simulation results of rail-to-rail input swing static comparator for different applications.                                                             |    |

| Table 3.4 Transistors aspect ratios for dynamic comparator with a cross-coupled transist high (1 MHz) input frequency signal                                       |    |

| Table 3.5 Dynamic comparator with a cross-coupled transistors simulation results                                                                                   | 37 |

| Table 3.6 Transistors aspect ratios for a modified dynamic comparator with a current source cross-coupled NMOS transistors for high (1 MHz) input frequency signal |    |

| Table 3.7 Modified dynamic comparator with a current source and a cross-coupled transistors simulation results.                                                    |    |

| Table 3.8 Transistors aspect ratios for dynamic latched comparator using back-to-back in for medium (20 KHz), and high (1 MHz) frequency input signals             |    |

| Table 3.9 Dynamic latched comparator using back-to-back inverters simulation results                                                                               | 41 |

| Table 3.10 Modified dynamic latched comparator simulation results                                                                                                  | 42 |

| Table 3.11 Double-tail dynamic latched comparator simulation results                                                                                               | 45 |

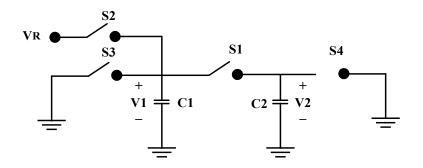

| Table 4.1 Serial charge redistribution DAC operation                                                                                                               | 51 |

| Table 4.2 Binary weighted switched capacitor array DAC simulation results                                                                                          | 55 |

| Table 5.1 SAR controller algorithms.                                                                                                                               | 60 |

| Table 6.1 Power consumption percentage for each building block in realization 1, 2 and 3                                                                           | 85 |

| Table 6.2 Simulation results and comparison of three proposed 8-bit SA-ADC realizations                                                                            | 85 |

| Table 6.3 Comparison with other previous works                                                                                                                     | 86 |

## Chapter 1

## Introduction

With the continuous growth in technology, electronic devices are being improved to serve people's life in all aspects. As the number of people conducting sedentary life increases, chronic diseases are continuing to spread among people of all ages. One of the most important technology is developing biomedical systems for diagnosing, monitoring, and treating various diseases. Another important technology is the wireless applications. Handheld devices such as: cell phones, palmtop, and laptop computer are rapidly becoming an integral part of people daily lives. In most cases, these devices have compatible data communication interfaces by a cable connections and configuration procedures. An obvious solution is to get rid of these cables and use short range wireless links to facilitate on demand connectivity among devices.

This chapter introduces the thesis and it is organized as follows: Section 1.1 illustrates the thesis motivation. The thesis objectives are presented in section 1.2. Section 1.3 states the thesis contribution. Finally the thesis organization is included in section 1.4.

#### 1.1 Thesis Motivation

The biomedical electronics world is rapidly changing with high future potential. With new technology, new designs with more features are placed into the biomedical devices. Nowadays, integrated circuit technology was developed in which the medical diagnostic systems can be miniaturized to portable devices. This kind of technology allow people to monitor their medical condition regardless of their age or location. For example, a recent study found nearly 90% of respondents are using mobile devices within their organizations to engage patients in their healthcare [1]. Furthermore, in large senior living facilities, the requirements of the care providers are fast and efficient ways to collect the residents' health data and update patient records in real time [1]. A small mobile device such as a smartphone or tablet are preloaded with healthcare applications and it consists of mobile healthcare sensor, device, server and medical service which make it possible to perform these tasks easily from any location. Various biomedical signals will be sensed by the sensor such as: sleep monitoring, heart rate, skin temperature, stress,

electrocardiogram and blood pressure. After that, these biomedical signals will be transferred to the server by the device which will stored and analyzed it. An additional benefit of this approach is such devices can be secured and controlled remotely via medical service [1].

Analog-to-digital converter (ADC) is considered as one of the main electronic blocks in the biomedical systems and healthcare integrated circuit. It becomes a bottleneck in data processing applications and it limits the performance of the overall system. Low power design and high resolution ADC are the main requirements in the biomedical applications. Sigma-delta ADC is a proper choice for high resolution ADC where the successive approximation analog to digital converter (SA-ADC) is a proper choice for low power ADC [2].

### 1.2 Thesis Objectives

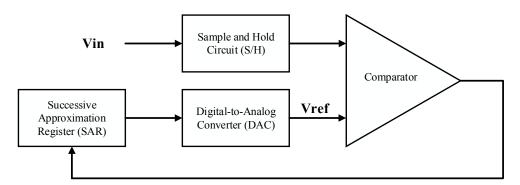

The objective of this thesis is to search and find out low power 8-bit SA-ADC for portable biomedical applications. The architecture of the SA-ADC used in this work is single ended DAC based and it consists of a sample and hold (S/H) circuit, a comparator, a successive approximation register (SAR) controller in addition to digital to analog converter (DAC) as shown in Figure (1.1) [3]. The analog to digital conversion is based on the binary search algorithm. At the sampling phase, the sample and hold (S/H) circuit stores the analog signal. The comparator determines the polarity of the difference between the reference voltage and the sampled analog signal. After that, the comparator output triggers the successive approximation register (SAR) controller which feeds the digital to analog converter (DAC) to prepare the reference voltage for the next comparison. In this algorithm, each bit needs one clock cycle to be determined. Therefore, the SA-ADC needs n clock cycles to complete an n-bit conversion [3].

The most power efficient SA-ADC is derived from three different possible realizations. These realization are implemented using the same S/H circuit which is based on a sampling transistor with dummy switch, the choice of static or dynamic comparator, the choice of conventional or clock gated SAR, and the same binary weighted capacitor array DAC. In addition to that, the SAR controller is implemented using D-flip flop (D-FF) or hybrid latch-flip flop (HL-FF). The low power dissipation is behind the use of the simplest S/H and DAC circuits without additional calibration or analog circuits. The first realization is implemented using static comparator and conventional SAR, the second realization is implemented using static comparator and clock gated

SAR and the third realization is based on the double-tail dynamic latched comparator and clock gated SAR. These realizations are characterized by moderate speed, moderate accuracy, and low power dissipation which meets the requirements of biomedical applications [2]. The proposed SA-ADCs are simulated and compared using 90nm CMOS technology file on LT-spice-IV.

Figure (1.1) Block diagram of a single ended DAC based SAR ADC architecture [3]

#### 1.3 Thesis Contribution

The fundamental building blocks of the SA-ADC are S/H circuit, comparator circuit, DAC circuit and SAR control logic. The comparator circuit is one of the main sources of power consumption in the SA-ADC for low frequency applications. The choice of the static or dynamic comparator structure has a great effect on the power consumption [2,4]. Furthermore, the SAR control logic is considered a source of dynamic power consumption as a digital circuit due to its high frequency clock signal [2,5].

In this thesis, a survey of different structures and design considerations of each building block in the SA-ADC has been studied, analyzed, simulated and compared in order to select the best candidate for biomedical (low-frequency) applications in term of low power consumption. As a result, three different CMOS realizations of an 8-bit single ended DAC based SAR ADC are proposed. Moreover, they are implemented using alternative building blocks of the SA-ADC in order to illustrate the effect of each building block structure on the SA-ADC performance especially on the power consumption. The aim is to reduce the power consumption. Therefore, in each realization the power consumption has been minimized using alternative building blocks.

The second main contribution in this thesis is that, the SAR controller for each realization is implemented twice, the first one using D-flip flop (D-FF) and the second one using the hybrid latch-flip flop (HL-FF) in order to illustrate the effect of the flip flop (FF) type on the power consumption of the SA-ADC. It was worth to note that the structure's choice of each building blocks in the SA-ADC is not the only way to achieve minimum power consumption, but the suitable type of the FF should be selected in order to save a great amount of power consumption regarding the FF complexity.

The proposed realizations are simulated using 90nm CMOS technology file on LT Spice IV under supply voltage of 1V. The simulation results show that the SA-ADC realization which implemented by using the double-tail dynamic latched comparator and the clock-gated D-FF based SAR without additional calibration or analog circuits is superior from point of view of the power consumption compared with the first two realizations given in this thesis and also compared with previous work given in [2,6,7,8,9]. A layout and extraction of the best realization in term of power consumption is done using L-edit. In addition to that, it was tested under supply voltage of 0.85 V to achieve further reduction in power consumption. A reconstruction of the real recorded electroencephalogram (EEG) signal was realized for the best realization under 1V supply voltage and it was consistent with the input of the real recorded EEG signal waveform.

### 1.4 Thesis Organization

This thesis is organized into six chapters with references and appendix listed at the end. Each chapter has a brief introduction of the work undertaken and it is followed by the detailed analysis.

Chapter 2 illustrates a survey of sample and hold (S/H) circuits, which is the first block in the SA-ADC. It introduces different structures of S/H circuits which meet the requirements of low and high frequency applications. A simulation was done for the introduced S/H circuits in low, medium and high frequency and the best S/H circuit has been chosen for the biomedical signals.

Chapter 3 reviews the comparator circuits which is the second block in the SA-ADC. It was simulated and tested in low, medium and high frequency. As a result of this chapter, a low power dynamic comparator has been chosen for the biomedical signals.

In Chapter 4, different topologies of digital-to-analog converters (DACs) have been discussed. The advantages and disadvantages of each DAC have been illustrated. A suitable DAC has been chosen and simulated for the biomedical signals.

Chapter 5, illustrates two different successive approximation register (SAR) controllers which are the conventional SAR and clock gated SAR. After these two controllers have been studied, a simulation and a comparison were performed on the two SAR controllers. Furthermore, they were tested on D-FF and HL-FF. The best SAR controller in term of power consumption has been selected.

The complete CMOS realizations of an 8-bit SA-ADC and simulation results are illustrated in Chapter 6. It shows the SA-ADC architecture using different ways to realize its key building blocks result in three proposed possible realizations of an 8-bit SA-ADC. These realizations are discussed, simulated and compared to figure out the best candidate from power consumption point of view and achieving reasonable performance metrics. In addition to that, these proposed realizations have been compared with previous works in this chapter. Furthermore, this chapter presents a layout and reconstructed of a real recorded EEG signal as an example of one of the biomedical signals for the best proposed realization in term of power consumption. Also, it includes the best low power realization simulation results under supply voltage of 0.85 V.

Finally, Chapter 7 offers conclusions and recommends some possible future work that may be undertaken in the same direction.

## Chapter 2

# Sample and Hold Circuits

#### 2.1 Introduction

Sample-and-hold (S/H) circuit is one of the main significant analog building blocks, especially in analog-to-digital converters (ADCs) [3]. It is also often referred to as "track-and-hold" circuit. Normally, these two terms are synonymous except for a few individual switched capacitor sample and hold circuits that do not have a phase where the output signal is tracking the input signal. It is the first block of the ADC components in which the input signal is seen by the input of the S/H circuit. Therefore, it has a significant effect on the whole ADC performance which in turns will affect the overall system. In many cases, using the S/H circuit at the front of the data converters have a significant effect. This effect appears in minimizing the errors due to slightly different delay times in the internal operation of the converter [3].

There are many types of S/H circuits; the first type is S/H circuits with an active block (like the operational amplifier) and/or supply voltage which includes S/H circuit with clock feedthrough cancellation, inverting S/H circuit and S/H circuit with bootstrapped technique. The second type is S/H circuits without an active block and does not need a supply voltage [3].

The objective of this chapter is to select the best S/H circuit candidate for each application among the introduced types under low voltage operation. The introduced S/H circuits are using either one single sample transistor or transmission gate, bootstrapped switch or not and single ended structure or differential. The reliability and accuracy of the S/H circuit depend mainly on the on-resistance of the sampling switch which will affect the switch linearity. It's worth noting that different sampling rates are used for different applications. This will affect the signal to noise and distortion ratio (SNDR), speed and power consumption of the S/H circuit and the overall ADC. Depending on the application, the emphasis will be on different metrics. In addition to that, a simulation was done for the presented S/H circuit types using 90nm CMOS technology on LT Spice IV. Furthermore, they were tested in low (250 Hz), medium (20 KHz), and high (1 MHz, 7 MHz and 13.6 MHz) frequency input signals in order to select the best S/H circuit candidate for each application. This chapter is organized as follows: Section 2.2 illustrates basic S/H circuit and

its modified versions without bootstrapped techniques. S/H circuits with bootstrapped techniques are presented in section 2.3. Section 2.4 introduces proposed modified low-power bootstrapped S/H circuit using transmission gate and section 2.5 includes simulation results for different applications.

## 2.2 Basic Sample and Hold Circuit

Basic S/H circuit is considered one of the simplest S/H circuits that can be realized using a CMOS technology [3]. This section introduces basic S/H circuit architecture, its problems, and a modified versions of it which compensate the induced problems. All the presented S/H circuits in this section are from the second type of S/H circuits.

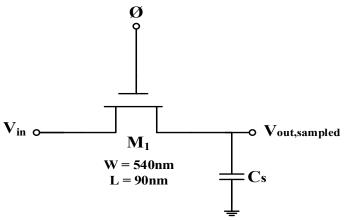

Basic S/H circuit is a single-ended architecture. It consists of single NMOS switch  $M_1$  and a sampling capacitor  $C_s$  as shown in Figure (2.1). It operates in a single phase  $\emptyset$ . When  $\emptyset$  goes high the transistor turns ON, and the voltage across the capacitor ( $V_{out,sampled}$ ) follows the input voltage ( $V_{in}$ ). When  $\emptyset$  goes low, the transistor turns OFF, and ( $V_{out,sampled}$ ) will stay constant having a value equal to ( $V_{in}$ ) at the instance of  $\emptyset$  went low [3].

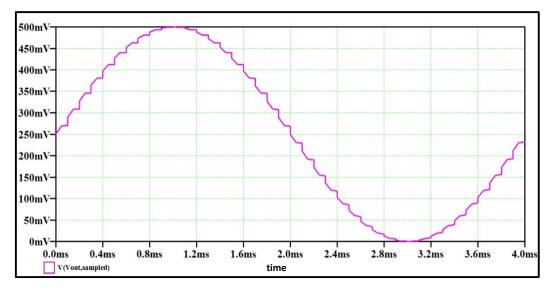

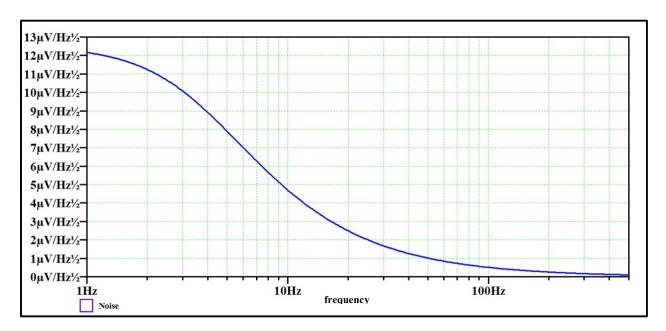

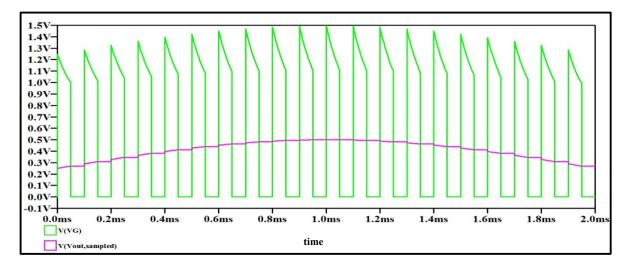

A simulation was done for this circuit for an electrocardiogram (ECG) signal properties [2]. The input signal is a sinusoidal input with amplitude and frequency of 500 mV<sub>p-p</sub> and 250 Hz respectively. This signal is sampled at clock frequency of 10 KHz. The sampling capacitor  $C_s$  is chosen to be 5pF. It is worth noting that the value of the sampling capacitor is a function of two main factors: the ADC input range and resolution, which translates into an equivalent thermal noise specification ( $\frac{KT}{C_s}$ ) [2]. The aspect ratio of the transistor  $M_1$  is (W=540nm / L=90nm). Figure (2.2) shows the sampled output voltage ( $V_{out,sampled}$ ) of this circuit. All the introduced types have the same ( $V_{out,sampled}$ ) shape and the main difference between them will be illustrated in the simulation results section. The noise spectrum of this circuit was calculated over the interest bandwidth of 500 Hz as shown in Figure (2.3) with total RMS output noise of 26.58  $\mu$ V.

Figure 2.1 Basic sample and hold circuit [3]

Figure 2.2 Sampled output Voltage ( $V_{out,sampled}$ ) with sampling frequency of 10 KHz

Figure 2.3 Noise spectrum of  $(V_{out,sampled})$  over bandwidth of 500 Hz

Charge injection and clock feedthrough are considered two major problems occur in basic S/H circuit. It is happening when a transistor is used as a switch in a switched capacitor circuit [2,3]. A modified versions of basic S/H circuit will be introduced in the following subsections in order to reduce the effect of these problems and compensate the induced errors.

Charge injection occurs when the clock  $\emptyset$  goes high. The NMOS transistor turns ON, and the input voltage is sampled by the capacitor  $C_s$ . Due to the inverted channel, a charge under the gate oxide is produced, and it is given as follows [2]:

$$Q_{ch} = W L C_{ox} (V_{DD} - V_{in} - V_{tn})$$

(2.1)

Then, when the clock  $\emptyset$  goes low, The NMOS transistor turns OFF. The created channel charge will flow out from the NMOS gate into its source and drain creating an error in the sampled voltage. If all the charges are injected on the sampling capacitor  $C_s$ , the sampled output voltage is given by the following equation [2]:

$$V_{\text{out}} = V_{\text{in}} (1 + \frac{W L C_{\text{ox}}}{C_{\text{s}}}) - (\frac{W L C_{\text{ox}}}{C_{\text{s}}}) (V_{\text{DD}} - V_{\text{tn}})$$

(2.2)

Therefore, the sampled output voltage is affected by two parameters. These parameters are a non-unity gain  $(1 + \frac{W \, L \, C_{ox}}{C_s})$  and a constant offset voltage  $(-\left(\frac{W \, L \, C_{ox}}{C_s}\right)(V_{DD} - V_{tn}))$  [2].

Clock feedthrough is defined as the coupling between the clock transitions and the sampling capacitor by the MOS transistor through its gate-drain or gate-source overlap capacitances. When the clock Ø goes high, an overlap capacitance is fed through the gate-source, the gate-drain, or both. While in the OFF state of the transistor, a capacitive divider is created. This operation result in an offset voltage which is given as follows:

$$\Delta V_{\text{offset}} = \frac{c_{\text{ov}}}{c_{\text{ov}} + c_{\text{s}}} V_{\text{DD}}$$

(2.3)

Where  $C_{ov}$  is the overlap capacitance [2].

### 2.2.1 Differential Basic Sample and Hold Circuit

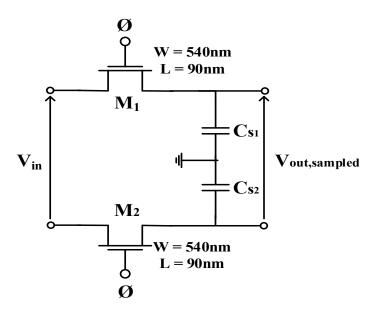

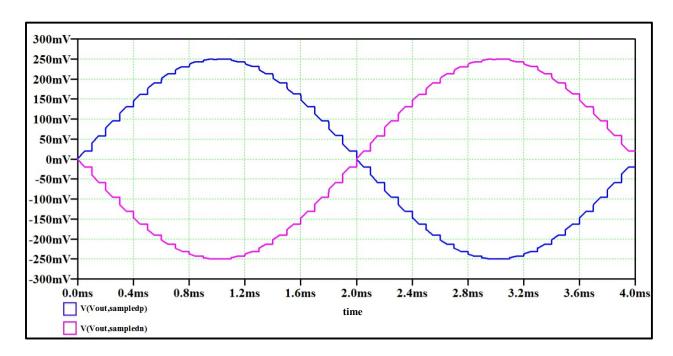

The principle of this circuit is to cancel the charge injection problem by applying a differential balanced input on the basic S/H circuit as shown in Figure (2.4). This is done if the differential sampling capacitors  $C_{s1}$  and  $C_{s2}$  are matched [10]. A simulation was done for this circuit using the aspect ratios which are illustrated in Figure (2.4) with  $C_{s1}$  and  $C_{s2}$  of 5pF and the same previous input characteristics. Figure (2.5) shows the input clock pulses. The differential input and differential output are shown in Figure (2.6) and Figure (2.7) respectively. Figure (2.8) shows the noise spectrum of the differential output with total RMS noise of 29  $\mu$ V.

Figure 2.4 Differential basic sample and hold circuit [10]

Figure 2.5 Input clock pulses (Ø)

Figure 2.6 Differential balanced input

Figure 2.7 Differential output

Figure 2.8 Noise spectrum of differential output over bandwidth of 500 Hz

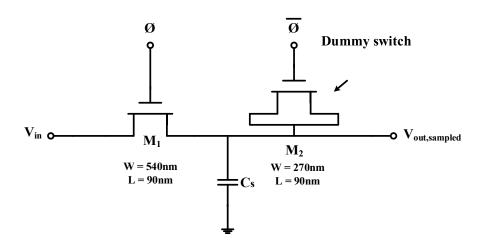

#### 2.2.2 Basic Sample and Hold Circuit with Dummy Switch

This method is considered one of the most common methods that is used to overcome the charge injection and clock feedthrough effect. Figure (2.9) shows basic S/H circuit with dummy switch.  $M_2$  is a dummy switch with its source and drain shorted. It is placed in series with  $M_1$  having a complement clock of  $\emptyset$ . When  $M_1$  turns OFF, and  $M_2$  turns ON,  $M_2$  will absorb the channel charge deposited on  $C_s$ . The following equations express the injected charge  $\Delta q_1$  and the absorbed charge  $\Delta q_2$  respectively as follows [2]:

$$\Delta q_1 = \frac{W_1 L_1 C_{ox} (V_{DD} - V_{in} - V_{tn1})}{2}$$

(2.4)

$$\Delta q_2 = W_2 L_2 C_{ox} (V_{DD} - V_{in} - V_{tn2})$$

(2.5)

In order to achieve ( $\Delta q_1 = \Delta q_2$ ), the channel width of  $M_2$  should be half that of  $M_1$  assuming the channel length of both transistors is equal. Thus, the charge injection and clock feedthrough will be suppressed [2]. A simulation was done for this circuit using the aspect ratios which are illustrated in Figure (2.9) with  $C_s$  of 5pF and the same previous input characteristics. It has the same noise spectrum as the basic S/H circuit with total RMS output noise of 26.57  $\mu$ V.

Figure 2.9 Basic sample and hold circuit with dummy switch [2]

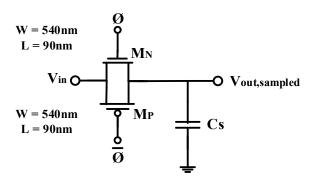

#### 2.2.3 Basic Sample and Hold Circuit using Transmission Gate

This technique is based on replacing the single transistor in Figure (2.1) with a CMOS transmission gate as shown in Figure (2.10). If the size of PMOS transistor  $M_P$  is taken to be the same as NMOS transistor  $M_N$ . Then, the charge injection due to each transistor will be canceled when the transmission gate turns OFF. PMOS transistor  $M_P$  have the advantage in enhancing the on-conductance between the input and output when the input is close to the supply voltage [3,11]. A simulation was done for this circuit using the aspect ratios which are illustrated in Figure (2.10) with  $C_s$  of 5pF and the same previous input characteristics. It has the same noise spectrum as the basic S/H circuit with total RMS output noise of 26.59  $\mu$ V.

However, at the circuit level, in low voltage and high frequency condition; the MOSFETs switches may not be fully turned on as they are under a higher voltage operation. It is happening when the sum of the absolute value of the PMOS threshold voltage and that of the NMOS is greater than the supply voltage. The MOSFETs switches may now have extremely poor conductance and would limit the bandwidth of the circuits. Therefore, a bootstrapped technique is required [11].

Figure 2.10 Basic sample and hold circuit using transmission gate [3]

### 2.3 Sample and Hold Circuits with Bootstrapped Technique

Two types of bootstrapped techniques have been introduced in this section [11,12]. The first type keeps the on-resistance of the sampling switch small and varying due to the gate-source voltage variation of the sampling switch which is S/H circuit with boosted driver technique [11,13]. The second type keeps the on-resistance of the sampling switch small and constant because the gate-source voltage of the sampling switch is constant and independent of the input signal which is S/H circuit with bootstrapped technique [12]. These techniques are convenient in low voltage operation. They aims to provide a small on-resistance of the sampling transistor which results in improving the switch linearity, reliability and bandwidth with high signal-to-noise and distortions ratio (SNDR) [11].

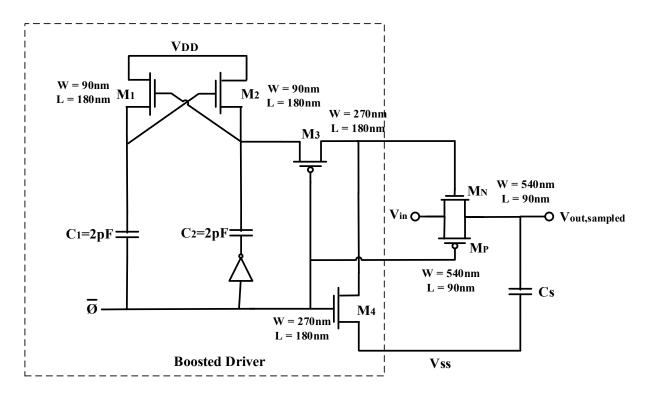

#### 2.3.1 Sample and Hold Circuit with Boosted Driver Technique

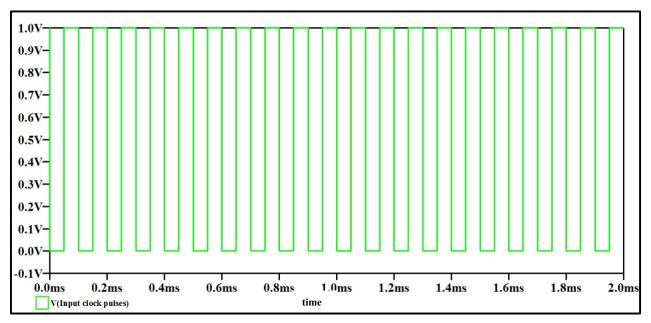

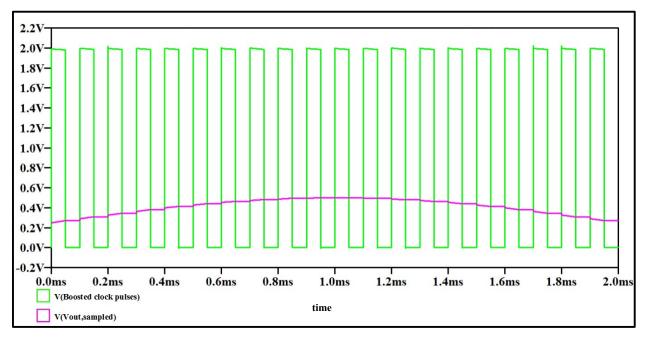

Figure (2.11) shows S/H circuit with boosted driver using transmission gate. The goal of this circuit is to achieve both low power and a wide bandwidth. The gate of the transistor  $M_N$  is connected to the boosted driver output. It operates by applying a square wave input signal of  $(V_{DD})$ . When Ø is high, the bottom plate of  $C_2$  and the top plate of  $C_1$  are charged to  $(V_{DD})$ . When Ø goes low, the supply voltage is applied to each second capacitor plates. Then, the charge stored in  $C_2$  is transferred to the gate of  $M_N$  by  $M_3$  with an inverted square wave output which is generated according to:

$$V_{\text{gateM}_{N}} = 2V_{\text{DD}} \cdot \frac{C_{2}}{C_{\text{gateM}_{N}+C_{2}+C_{\text{parasitic}}}}$$

(2.6)

In other words, the boosted driver output has a periodical signal switching between  $(2V_{DD}-\Delta V)$  and the ground.  $(\Delta V)$  result from the charge sharing between the capacitor  $C_2$  and the parasitic capacitance at the gate of  $M_N$ . The bandwidth of this circuit is  $({}^1/_{2\pi R_{on}C_s})$ , where  $R_{on}$  the onresistance of the sampling switch  $M_N$ . In this technique, the on-resistance of the sampling switch is small and varying due to  $(V_{GS})$  variation [11,13]. For the same input signal that is mentioned previously with supply voltage  $(V_{DD})$  of 1V. Figure (2.12) illustrates the simulation results of the input clock pulses.  $C_1$ ,  $C_2$  and  $C_s$  are chosen to be 2pF, 2pF and 5pF respectively. The transistors

aspect ratios' are illustrated in Figure (2.11). Figure (2.13) shows zoomed ( $V_{out,sampled}$ ) of this circuit with the inverted square wave signal switching between 2V and the ground is formed on the gate of  $M_N$  (boosted clock). It has the same noise spectrum as the basic S/H circuit with total RMS output noise of 26.59  $\mu$ V.

Figure 2.11 Sample and hold circuit using transmission gate with boosted driver [11]

Figure 2.12 Input clock pulses (Ø)

Figure 2.13 Zoomed ( $V_{out,sampled}$ ) with inverted boosted clock

#### 2.3.2 Sample and Hold Circuit with Bootstrapped Technique

In low voltage operation, the reliability constraints of the technology must not be crashed. For example, using MOS transistor as a switch in low voltage operation has several disadvantages. As a result of decreasing the supply voltage, the threshold voltage of high-threshold transistors must be reduced. This will increase the sub-threshold leakage current exponentially which distort the analog sample, and hence increase the static power dissipation. In another technique, MOS transistors with high-threshold voltage are used. This technique has disadvantages in which the transistors have high series resistance which reduce the speed [12].

However, the consumer trends goes for high performance portable electronics. Magnify the importance of the power dissipation reduction to guarantee longer battery life for enhanced portability and noise reduction for high signal integrity. Therefore, long circuit lifetime can be assured with great confidence by keeping the device voltages within the rated supply voltage. This can be observed by implementing the MOS switches without low-threshold devices by using a bootstrapped technique which does not subject the devices to large terminal voltages [12].

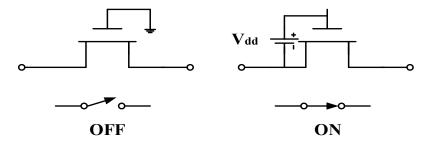

Figure (2.14) shows a bootstrapped switch which is conceptually a single NMOS transistor. In the OFF state, the gate is grounded and the switch will be in the cutoff mode. In the ON state, a constant voltage of  $(V_{DD})$  is applied across the gate-to-source terminals, and a low on resistance is formed from drain-to-source terminals independent of the input signal. If the gate voltage exceeds  $(V_{DD})$  for a positive input signal, none of the terminal-to-terminal device voltages exceed  $(V_{DD})$  [12].

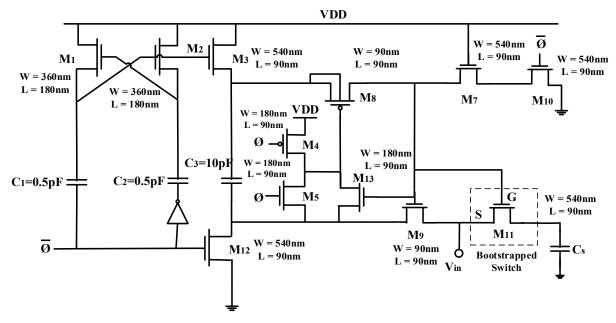

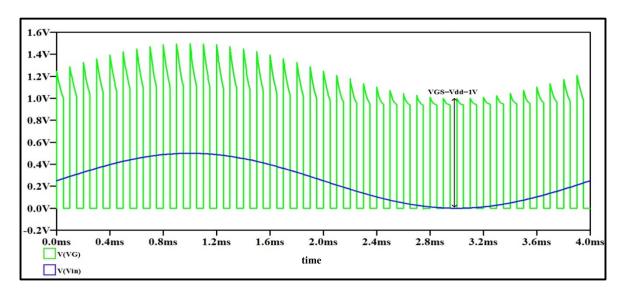

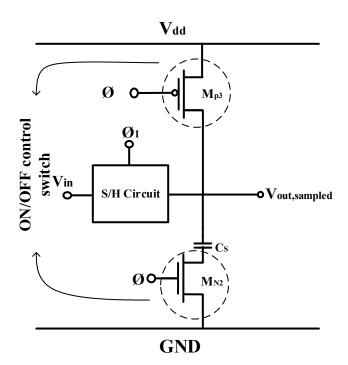

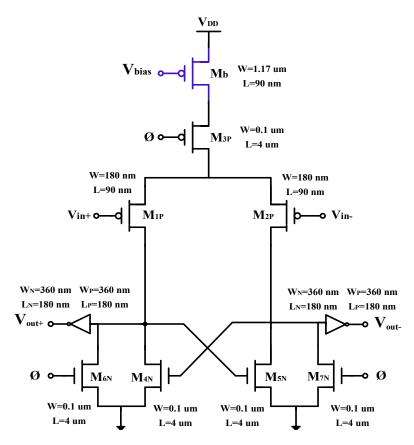

Figure (2.15) shows the actual bootstrapped circuit. It operates on a single phase clock  $\emptyset$  that turns the bootstrapped switch  $M_{11}$ ON and OFF. When  $\emptyset$  is low,  $M_7$  and  $M_{10}$  discharge the gate of  $M_{11}$  to ground and thus the bootstrapped circuit in the OFF phase. In this phase,  $(V_{DD})$  is applied across capacitor  $C_3$  by  $M_3$  and  $M_{12}$ . This capacitor will act as a battery across the gate-to-source terminals of  $M_{11}$ during the ON phase. The job of  $M_8$  and  $M_9$  is to isolate the switch  $M_{11}$  from  $C_3$  while it is charging. When  $\emptyset$  is high, the gate of  $M_8$  will be pulled down by  $M_5$ , allowing charge from the battery capacitor  $C_3$  to flow onto gate G. This turns on both  $M_9$  and  $M_{11}$ .  $M_9$  enables gate G to track the input voltage S shifted by  $(V_{DD})$ , keeping the gate-to-source voltage of  $M_{11}$  constant

regardless the input signal. For example, if the source S is at  $(V_{DD})$ , then gate G is at  $(2V_{DD})$ ; however,  $(V_{GS} = V_{DD})$ . The body (n-well) of  $M_8$  is connected to its source in order to repress latch up.  $M_7$  and  $M_{13}$  are not functionally necessary but to improve the circuit reliability.  $M_7$  reduces the  $(V_{DS})$  and  $(V_{GD})$  experienced by  $M_{10}$  when  $\emptyset$  is low.  $M_{13}$  ensures that  $(V_{GS8})$  does not exceed  $(V_{DD})$ .  $M_1$ ,  $M_2$ ,  $C_1$ , and  $C_2$  form a clock multiplier that enables  $M_3$  to charge  $C_3$  during the OFF phase [12].

$C_3$  must be sufficiently large to supply the stored charges to the gate-to-source terminals of  $M_{11}$  in addition to all parasitic capacitances in the charging path. Otherwise, charge sharing will significantly reduce the boosted voltage according to equation (2.7), where  $C_p$  is the total parasitic capacitance connected to the top plate of  $C_3$  while it is across  $M_{11}$  [12]

$$V_{G} = V_{S} + \frac{C3}{C3 + C_{p}} V_{DD}$$

(2.7)

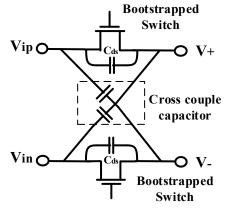

When the bootstrapped switch is OFF, a  $C_{ds}$  capacitor is formed between the drain-to-source terminals of the sampling transistor. It couples the input signal to the sampling capacitor by  $C_{ds}$  and the routing parasitic capacitance. The coupling effect degrades the high frequency performance because  $C_{ds}$  induces unequal charges in the comparison cycles, which result in a dynamic offset. Therefore, two cross-coupled metal oxide metal (MOM) capacitors are used to neutralize the effect as shown in Figure (2.16). A dummy switch is an alternative solution to reduce the coupling effect [12,14].

As a result of using bootstrapped technique, the gate-to-source voltage of the sampling transistor will have a constant voltage and it is relatively independent of the input signal. This will improve the switch linearity and the input bandwidth [12].

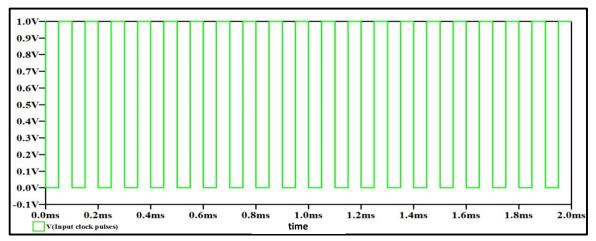

A simulation was done for this circuit with the same input signal that is mentioned previously. Figure (2.17) shows the input clock pulses. The supply voltage ( $V_{DD}$ ) is 1V and a clock pulses are formed on G that is shifted from the input signal by ( $V_{DD} = 1V$ ) as shown in Figure (2.18).  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_s$  are chosen to be 0.5pF, 0.5pF, 10pF and 5pF respectively. Figure (2.19) shows zoomed ( $V_{out,sampled}$ ) of this circuit with the clock formed on G. It has the same noise spectrum as the basic S/H circuit with total RMS output noise of 26.58  $\mu$ V. The aspect ratios of the transistors are shown in Figure (2.15).

Figure 2.14 Bootstrapped MOS switch [12]

Figure 2.15 Sample and hold with bootstrapped circuit technique [12]

Figure 2.16 Cross-coupled capacitors [14]

Figure 2.17 Input clock pulses (Ø)

Figure 2.18 Input signal with the clock pulses formed on G

Figure 2.19 Zoomed ( $V_{out,sampled}$ ) with the clock pulses formed on G

Finally, a power scalable technique of S/H circuit is introduced. Since the S/H circuit's working time frame is much smaller than the whole conversion period. It aims to save a large amount of static power when S/H circuit is idle during the conversion phase. So it becomes an essential circuit in high speed applications [15,16].

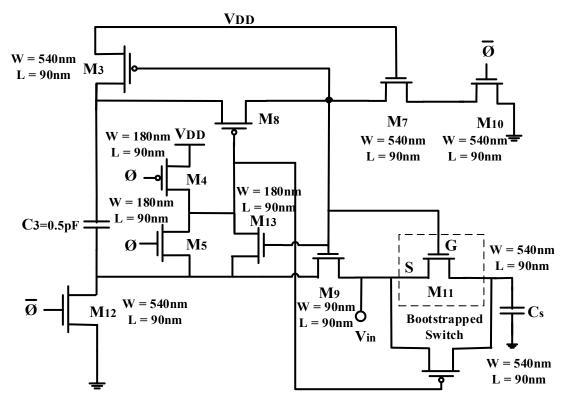

Figure (2.20) shows S/H circuit with power scalable ON/OFF technique. This technique can be added to any of the S/H circuits which were mentioned in this chapter. It is based on the addition of PMOS switch  $M_{p3}$  between the supply voltage and the output of the S/H circuit. When Ø is low (reset mode), the S/H circuit will be OFF. When Ø is high,  $M_{p3}$  is disconnected and the S/H circuit is in the ON mode. During the power down phase,  $M_{p3}$  will pull up the top plate of the sampling capacitor  $C_s$  which will degrade the speed during this phase. NMOS switch  $M_{N2}$  is consequently added between  $C_s$  and the ground in order to overcome this problem. So when Ø is low,  $C_s$  will be floating and the speed of the power down transient can be improved [16].

Figure 2.20 Sample and hold circuit with power scalable ON/OFF technique [16]

# 2.4 Proposed Modified Low-Power Bootstrapped Sample and Hold Circuit using Transmission Gate

A proposed modified low-power bootstrapped S/H circuit using transmission gate is illustrated in Figure (2.21). Simply, it is the same as the S/H circuit with bootstrapped technique which is shown in Figure (2.15) but without the multiplier circuit. The multiplier circuit consists of M<sub>1</sub>, M<sub>2</sub>, C1 and C2. In Figure (2.15), the gate of the NMOS transistor M3, which is responsible for charging the capacitor C3, is biased by the multiplier circuit. On the other hand, in Figure (2.21), the NMOS transistor M3 is replaced by a PMOS transistor M3 and its gate is biased by the gate of the bootstrapped switch M<sub>11</sub>. M<sub>3</sub> will charge C<sub>3</sub> to (VDD) in the OFF state of the bootstrapped switch M<sub>11</sub>; while in the ON state, the stored charge in C<sub>3</sub> will be applied to the gate-to-source terminal of M<sub>11</sub>. Both circuits make the gate-to-source voltage of M<sub>11</sub> constant and equal to the supply voltage which is independent of the input signal. This result in small and constant on-resistance of the sampling switch. The main important feature of the proposed modified low-power bootstrapped S/H circuit using transmission gate is power consumption. It consumes less amount of power compared to the other two presented bootstrapped techniques in medium and high frequency applications. In addition to that, the SNDR will not have a degradation even in high frequency application when the input signal is 1 MHz or 7 MHz or 13.6 MHz. A simulation was done for this circuit with the same input signal that is mentioned previously and with the aspect ratios shown in Figure (2.21). It has the same noise spectrum as the basic S/H circuit with total RMS output noise of 26.59 uV.

Figure 2.21 Proposed Modified low-power bootstrapped S/H circuit using transmission gate

#### 2.5 Simulation Results

A simulation was done for the various introduced S/H circuits using 90nm CMOS technology on LT Spice IV. It is done on different applications from low (250 Hz), medium (10 KHz) to high (1 MHz, 7 MHz and 13.6 MHz) frequency. It is worth noting that the value of the sampling capacitor is a function of two main factors: the ADC input range and resolution, which translates into an equivalent thermal noise specification ( $\frac{KT}{C_s}$ ) [2]. The sampling capacitor value was chosen based on the highest SNDR. It is chosen to be 5pf for low frequency application (ECG signal). While it is chosen to be 1pf for medium frequency application (audio signal). For high frequency applications (Bluetooth, DVB-H, and WLAN), the sampling capacitor  $C_s$  is 0.1pf.

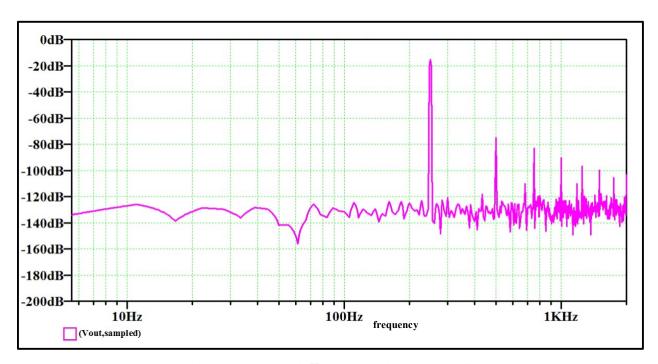

Table (2.1) shows the simulation results of the presented S/H circuits for different applications for a 1V supply voltage and 500 mV<sub>p-p</sub>. Signal to noise and distortion ratio (SNDR) was calculated for the different S/H using equation (2.8). It is calculated from the fast Fourier transform (FFT) spectrum by measuring the peak signal value and the distortions peak values over 45 cycles of ( $V_{out,sampled}$ ). The output noise spectrum and the sampling rate were calculated over the interest bandwidth (2BW<sub>signal</sub>). The average power consumption over one period is measured for the presented S/H circuits neglecting the required power to turn the switch ON and OFF. Figure (2.22) shows the FFT spectrum over 45 cycles of ( $V_{out,sampled}$ ) for the basic S/H circuit. All the presented S/H circuits have the same FFT spectrum as the basic S/H circuit and the difference between them is illustrated in Table (2.1).

$$SNDR (dB) = 20 \log \frac{Signal Peak}{Distortions Peak+RMS Noise}$$

(2.8)

As a result from this study, in term of high SNDR and low power consumption, the differential basic S/H circuit is the best candidate for low frequency applications, while S/H circuit with bootstrapped technique is the best candidate for medium to high frequency applications. In addition to that, all the presented S/H circuits' types have a closest value of SNDR in the low frequency application. This means that for low frequency signals, there is no significant effect of the presented S/H circuits on the SNDR value. Since the main objective of this work is to propose low power SA-ADC for portable biomedical applications. Therefore, it is focused on S/H circuits without active block and / or supply voltage which meets the requirements of biomedical (low-

frequency) applications and low power consumption. As a result, the basic S/H circuit with dummy switch was found the best candidate for single ended low power and high SNDR [17,18].

Figure 2.22 FFT spectrum of  $(V_{out,sampled})$  for the basic S/H circuit

Table 2.1 Simulation results of the presented S/H circuits for different applications

| S/H             | І Туре                       |            |                           |                                   |                                        |                                            |                                         | Proposed                                                                         |  |  |

|-----------------|------------------------------|------------|---------------------------|-----------------------------------|----------------------------------------|--------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------|--|--|

| Application     | Parameters                   | Basic S/H  | Differential Basic<br>S/H | Basic S/H<br>with Dummy<br>Switch | Basic S/H with<br>Transmission<br>Gate | S/H with<br>Boosted<br>Driver<br>Technique | S/H with Boot-<br>strapped<br>Technique | Modified Low-<br>Power<br>Bootstrapped S/H<br>Circuit using<br>Transmission Gate |  |  |

| ECG 250 Hz      | SNDR (dB)                    | 54.34      | 56.27                     | 54.39                             | 54.42                                  | 54.65                                      | 54.63                                   | 54.66                                                                            |  |  |

|                 | Average Power<br>Consumption | -          | -                         | -                                 | 1.4 pW                                 | 1.09 nW                                    | 29.82 nW                                | 29.53 nW                                                                         |  |  |

| Led 230 Hz      | Sampling Rate                |            | 10 KS/sec                 |                                   |                                        |                                            |                                         |                                                                                  |  |  |

|                 | Total RMS<br>Output Noise    | 26.58 μV   | 29 μV                     | 26.57 μV                          | 26.59 μV                               | 26.59 μV                                   | 26.58 μV                                | 26.59 μV                                                                         |  |  |

|                 | SNDR (dB)                    | 53         | 32.6                      | 53.01                             | 53.7                                   | 65.27                                      | 65.13                                   | 65.14                                                                            |  |  |

| Audio 20<br>KHz | Average Power<br>Consumption | -          | -                         | -                                 | 3 pW                                   | 44.28 nW                                   | 51.64 nW                                | 35.76 nW                                                                         |  |  |

|                 | Sampling Rate                |            | 800 KS/sec                |                                   |                                        |                                            |                                         |                                                                                  |  |  |

|                 | Total RMS<br>Output Noise    | 70.13 μV   | 69.58 μV                  | 70.09 μV                          | 70.13 μV                               | 70.13 μV                                   | 70.13 μV                                | 70.13 μV                                                                         |  |  |

|                 | SNDR (dB)                    | 40.05      | 17.02                     | 40.04                             | 40.78                                  | 56.56                                      | 56.78                                   | 56.69                                                                            |  |  |

| Bluetooth 1     | Average Power<br>Consumption | -          | -                         | -                                 | 329.9 pW                               | 2.06 μW                                    | 734.64 nW                               | 201.09 nW                                                                        |  |  |

| MHz             | Sampling Rate                | 40 MS/sec  |                           |                                   |                                        |                                            |                                         |                                                                                  |  |  |

|                 | Total RMS<br>Output Noise    | 223.44 μV  | 223.07 μV                 | 222.88 μV                         | 223.17 μV                              | 223.17 μV                                  | 223.44 μV                               | 223.17 μV                                                                        |  |  |

|                 | SNDR (dB)                    | 22.8       | 8.89                      | 22.79                             | 23.44                                  | 57.06                                      | 57                                      | 57.01                                                                            |  |  |

| DVB-H 7         | Average Power<br>Consumption | -          | -                         | -                                 | 2.11 nW                                | 12.68 μW                                   | 4.46 μW                                 | 883.57 nW                                                                        |  |  |

| MHz             | Sampling Rate                | 280 MS/sec |                           |                                   |                                        |                                            |                                         |                                                                                  |  |  |

|                 | Total RMS<br>Output Noise    | 223.81 μV  | 223.07 μV                 | 223.25 μV                         | 223.55 μV                              | 223.55 μV                                  | 223.81 μV                               | 223.55 μV                                                                        |  |  |

|                 | SNDR (dB)                    | 17.41      | 6.44                      | 17.40                             | 17.73                                  | 56.75                                      | 56.71                                   | 56.706                                                                           |  |  |

| WLAN 13.6       | Average Power<br>Consumption | -          | -                         | -                                 | 3.22 nW                                | 18.08 μW                                   | 8.38 μW                                 | 1.32 μW                                                                          |  |  |

| MHz             | Sampling Rate                |            |                           | 1                                 | 544 MS/sec                             | 1                                          |                                         | 1                                                                                |  |  |

|                 | Total RMS<br>Output Noise    | 223.84 μV  | 223.07 μV                 | 223.28 μV                         | 223.58 μV                              | 223.58 μV                                  | 223.84 μV                               | 223.58 μV                                                                        |  |  |

# Chapter 3

## **Comparator Circuits**

### 3.1 Introduction

The comparator is the second most widely used component in electronic circuits, after operational amplifier [3]. It is a key building block for applications where digital information needs to be recovered from analog signal especially in ADCs. It is the second block of the ADC components in which the output of S/H circuit seen by the input of the comparator. Therefore, it has a significant effect on the whole ADC performance which in turns will affect the overall system.

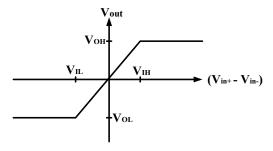

Figure (3.1a) shows the symbol of a differential comparator. Usually, the comparator stage is followed by a latch. Such comparators are well suited for logic circuits as the latch provides a large and fast output signal whose amplitude and waveform are independent of input signal. The transfer curve of the ideal differential comparator is illustrated in Figure (3.1b). In this Figure, the reference voltage ( $V_{ref}$ ) is assigned to the negative input of the comparator. When the positive input is higher than ( $V_{ref}$ ), then the output voltage is high ( $V_{OH}$ ), and if it is lower than ( $V_{ref}$ ), then the output is low ( $V_{OH}$ ). The ideal transfer curve corresponds to an infinite differential gain. However, in the reality, the differential gain has a finite value which is ( $A_v$ ). The transfer curve of such a comparator is shown in Figure (3.1c), where ( $V_{IL}$ ) and ( $V_{IH}$ ), are the input excess voltages called the overdrive. Overdrive is the input voltage that drive comparator from initial saturated input condition to a level required to switch the output state [3].

There are two types of comparators, static comparators, and dynamic comparators. In the static comparators, at every point in time (except during the switching transients), each gate output is connected to either  $(V_{DD})$  or  $(V_{ss})$  via a low-resistance path. It is used in medium speed applications. On the other hand, the dynamic comparators, relies on temporary storage of signal values on the capacitance of high impedance circuit nodes. It is used for high speed applications but it is more sensitive to noise [4]. It's worth noting that different sampling rates are used for different applications. This will affect the noise, speed and power consumption of the comparator

circuit and the overall ADC. Depending on the application, the emphasis will be on different metrics.

The objective of this chapter is to introduce various types of static and dynamic comparators in low voltage operation. All the presented comparators were analyzed, simulated and compared in term of complexity, dynamic range for proper operation regarding the mode of operation of the transistors, and average power consumption. The simulation was on LT Spice IV using 90nm CMOS technology under supply voltage of 1V. Furthermore, they were tested in low (250 Hz), medium (20 KHz), and high (1 MHz) frequency input signals in order to select the best comparator circuit candidate for the required application. This chapter is organized as follows: Section 3.2 illustrates static comparator circuits. Dynamic comparator circuits are presented in section 3.3. Each section includes its simulation results.

Figure 3.1a Differential comparator symbol [3]

Figure 3.1b Transfer curve of ideal comparator [3]

Figure 3.1c Transfer curve of real comparator with finite gain [3]

### 3.2 Static Comparators

Static comparator is a suitable choice for medium speed applications [2]. It has advantages of good performance and robustness (i.e. low sensitivity to noise), but unfortunately it has static power dissipation. The static power dissipation is due to the short circuit power dissipation which is the direct current path from the supply voltage to the ground while the switches are ON simultaneously for a short period [4].

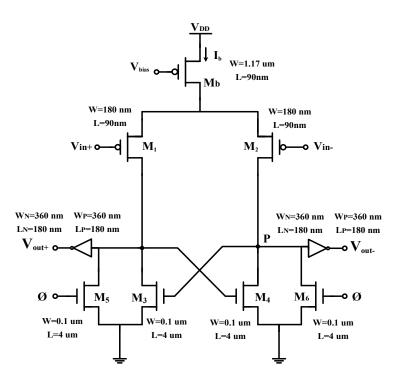

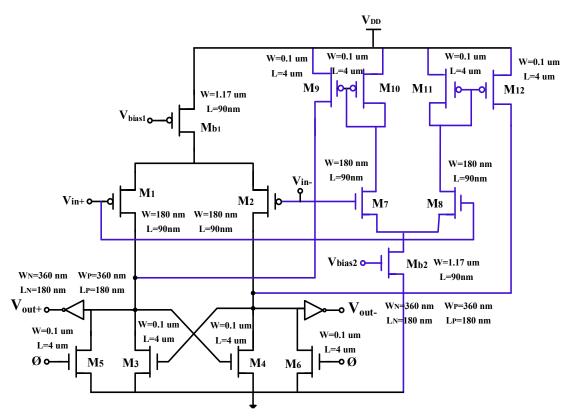

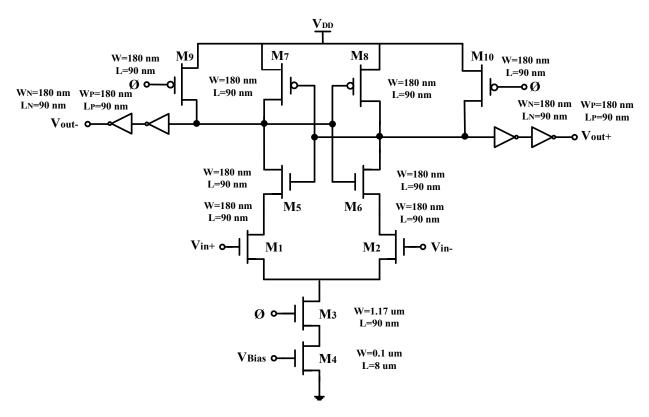

Figure (3.2) shows the static comparator circuit with cross-coupled transistors. The circuit will execute the comparison between the inputs when the clock  $\emptyset$  is low and both  $M_5$  and  $M_6$  transistors are turned OFF. If  $(V_{in+} > V_{in-})$ , the transistor  $M_2$  will be ON, and the transistor  $M_1$  is OFF. Therefore,  $(V_{out-})$  is low, and  $M_3$  turns ON causing  $(V_{out+})$  high. On the other hand, if  $(V_{in+} < V_{in-})$ , the transistor  $M_2$  will be OFF and the transistor  $M_1$  will be ON. Therefore,  $(V_{out+})$  is low and  $M_4$  turns ON causing  $(V_{out-})$  high. When the clock  $\emptyset$  is high, the comparator circuit is operating in the resetting mode, and both outputs  $(V_{out+})$  and  $(V_{out-})$  are pulled high to  $(V_{DD})$  via  $M_5$  and  $M_6$ . The two inverters with a designated threshold voltage amplify the complimentary outputs to their full rail-to-rail logic levels. In the resetting phase, the comparator circuit is idle for a short time until the remaining blocks of the ADC complete their operation. The transistors  $M_5$  and  $M_6$  are included to avoid hysteresis or delayed response on the resetting phase which in turn speeds up the comparator. At node P, the dominant pole frequency of the comparator is located, and is given as follows:

$$\omega_{\rm p} = \frac{g_{\rm m1}}{C_{\rm p}}, \ C_{\rm p} = C_{\rm gs3} + C_{\rm db2} + C_{\rm db4} + C_{\rm db\_6} + C_{\rm buffer}$$

(3.1)

Where  $C_p$  is the total capacitances at node P [2,11].

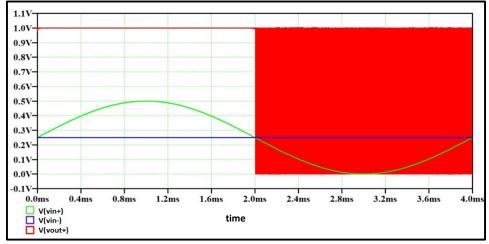

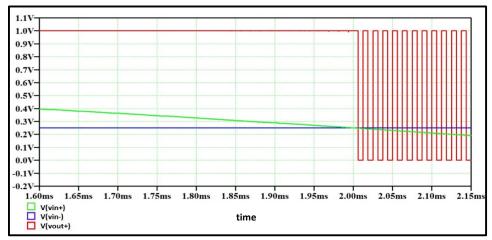

All the presented comparators in this chapter were simulated to evaluate their performance in low (250 Hz), medium (20 KHz) and high (1 MHz) frequency input signals for a sinusoidal wave with amplitude of 500 mV<sub>p-p</sub>. In order to fit the 10 KS/s, 800 KS/s, and 40 MS/s sampling rate in low, medium, and high input frequency signals respectively of the 8-bit SA-ADC, the speed of the comparator must be operated at no less than 80 KHz, 6400 KHz, and 320 MHz respectively. For all the presented comparators; the supply voltage is 1V and the bias voltage is set to be 0.55V to generate low bias current. Figure (3.3) and Figure (3.4) shows the simulation of the static

comparator output and a zoomed part respectively. Table (3.1) and Table (3.2) shows the transistors' aspect ratios for (1 MHz) input frequency and the static comparator simulation results respectively. The transistors' aspect ratios for (250 Hz) and (20 KHz) input frequency are shown in Figure (3.2). All the introduced comparators have the same static comparator output shape and the main difference between them is illustrated in the simulation results Tables.

Figure 3.2 Static comparator with cross-coupled transistors [2]

Figure 3.3 Static Comparator output when vin- = 0.25 V at speed of 80 KHz

Figure 3.4 Zoomed static comparator output

Table 3.1 Transistors aspect ratios for static comparator with a cross-coupled transistors for high (1 MHz) input frequency signal

| Transistor     | Dimensions (W/L)<br>(1 MHz) |

|----------------|-----------------------------|

| $M_1$          | 540nm/180nm                 |

| M <sub>2</sub> | 540nm/180nm                 |

| $M_3$          | 0.1μm/180nm                 |

| $M_4$          | 0.1μm/180nm                 |

| M <sub>5</sub> | 0.1μm/180nm                 |

| M <sub>6</sub> | 0.1μm/180nm                 |

| M <sub>b</sub> | 1.17μm/180nm                |

| inverters      | 360nm/180nm                 |

Table 3.2 Static comparator simulation results for different applications

|                                 | equency<br>ameters        | Low (250 Hz) | Medium (20<br>KHz) | High (1 MHz) |  |

|---------------------------------|---------------------------|--------------|--------------------|--------------|--|

| No. of                          | transistors               |              | 11                 |              |  |

| Dynamic                         | Vin+ 0-0.5                | 0.01 - 0.5   | 0.01 - 0.5         | 0.04 - 0.49  |  |

| Range of Vin-<br>Based on the   | Vin+ 0.1-0.6              | 0.11 – 0.59  | 0.11 – 0.59        | 0.11 - 0.54  |  |

| Dynamic<br>Range of Vin+<br>(V) | Vin+ 0.2-0.7              | 0.21 – 0.69  | 0.21 – 0.65        | 0.22 - 0.56  |  |

|                                 | Vin+ 0-0.5<br>Vin- 0.25   | 637.68 nW    | 710.99 nW          | 1.84 μW      |  |

| Average Power Consumption       | Vin+ 0.1-0.6<br>Vin- 0.35 | 544.36 nW    | 626.68 nW          | 1.68 μW      |  |

|                                 | Vin+ 0.2-0.7<br>Vin- 0.45 | 429.9 nW     | 529.92 nW          | 1.43 μW      |  |

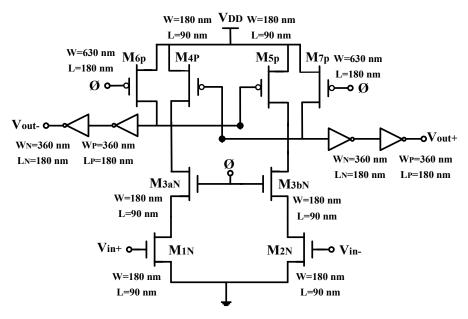

At low supply voltage, the maximum input signal swing of the ADC is limited which in turn leads to poor signal-to-noise ratio (SNR). In order to overcome such a problem, a rail-to-rail input range is required in the design. A comparator with a rail-to-rail common mode input range is necessary for this design in order to gain the required rail-to-rail input swing [11].

As shown in the Figure (3.5), the p- and n-type differential pairs are connected in parallel to extend the common mode input range to the power rails. These differential pairs eventually convert the differential input voltages into differential output currents. The summing up of currents drives the regenerative load formed by  $M_3$  and  $M_4$ . Large differential output currents are produced by appropriate design of the tail currents of the differential pairs which drives the regenerative loads at worst conditions [11].