Task 1:

First thing that I noticed is that we would need an 8-bit inverter for implementing the ALU.

Figure 1: DRC clean 8 bit inverter

Figure 2: Simulation verification of 8 bit inverter

Figure 3: ALU simulation verification of both S1 and S0 low, output is verified corret

Figure 4: Simulation 2 of ALU with S0 at 5V and S1 at 0V, verified correct

Figure 5: ALU simulation 3 S0 and S1 are 5V, output is verified correct.

Task 2:

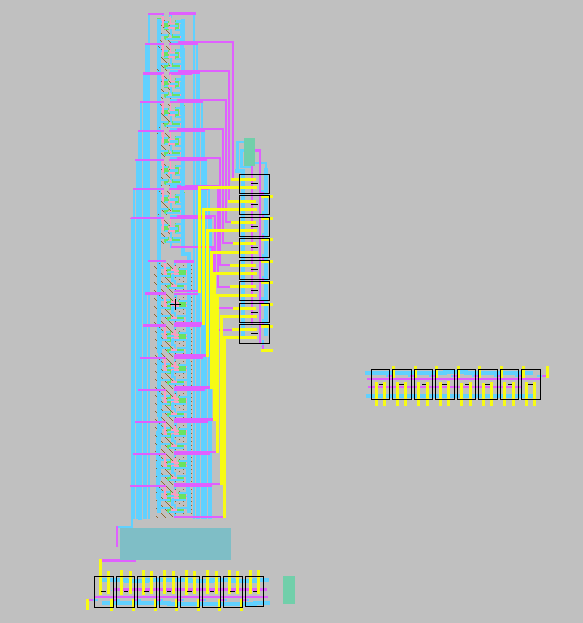

Figure 6: In progess layout of ALU

Figure 7: Library output error

Conclusion:

During the process of building the layout of the ALU my save became corrupted and I could no longer open the library that contained all of my components. I made some attempts at debugging the Java error and tried moving the library to different directories to attempt to fix it. Right now I am unable to get it to work, I will continue to try to fix the error but I will not be able to restart the lab since I would have to go back all the way to making the logic gates used for the FA and ALU and I just dont have the time to do this.