ENGR 351 HW 3

MSP430 Part 1

Name: Zane Sauer

Email:

zmsauer@fortlewis.edu

Introduction:

In this lab we use Electric VLSI to create a R 2R ladder.

Task 1:

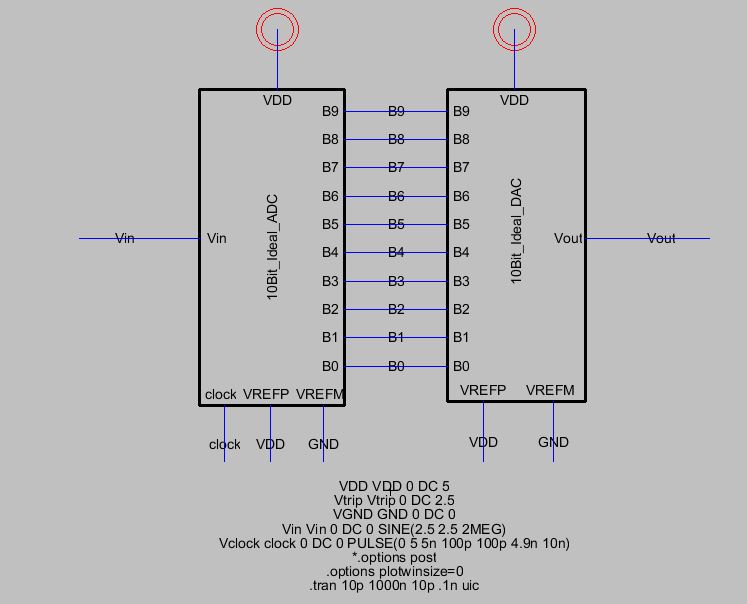

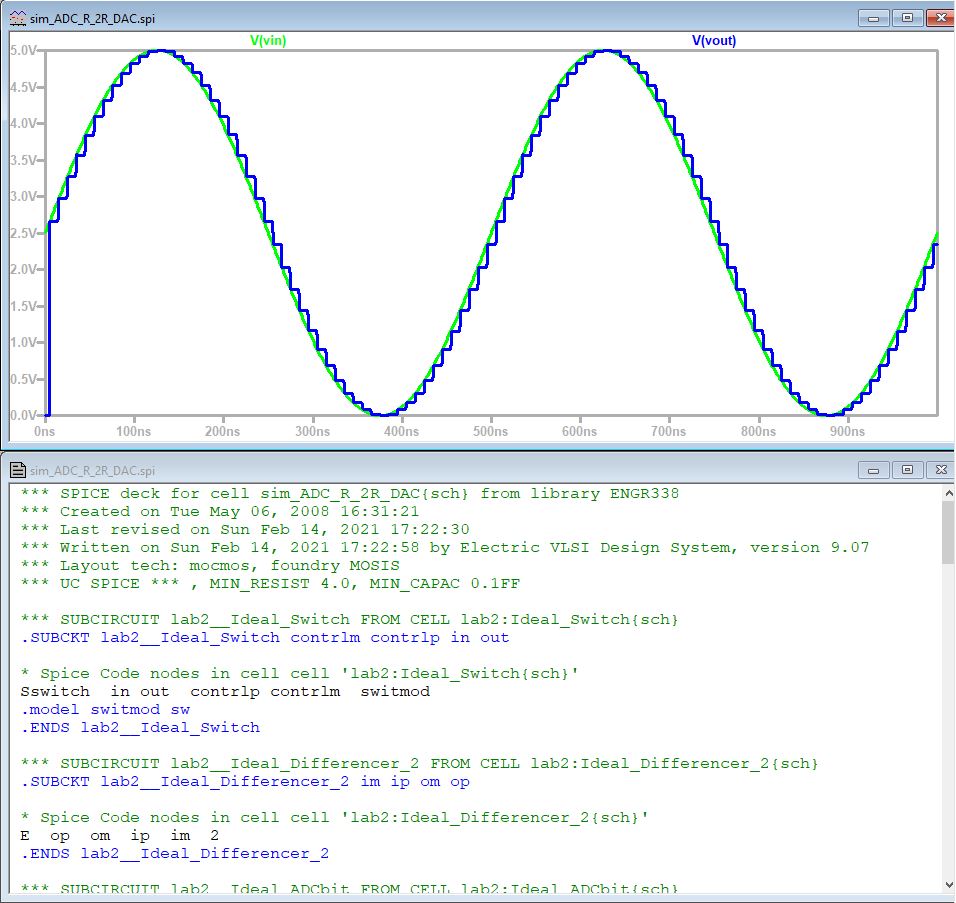

Figure 1: ADC to DAC given in tutorial

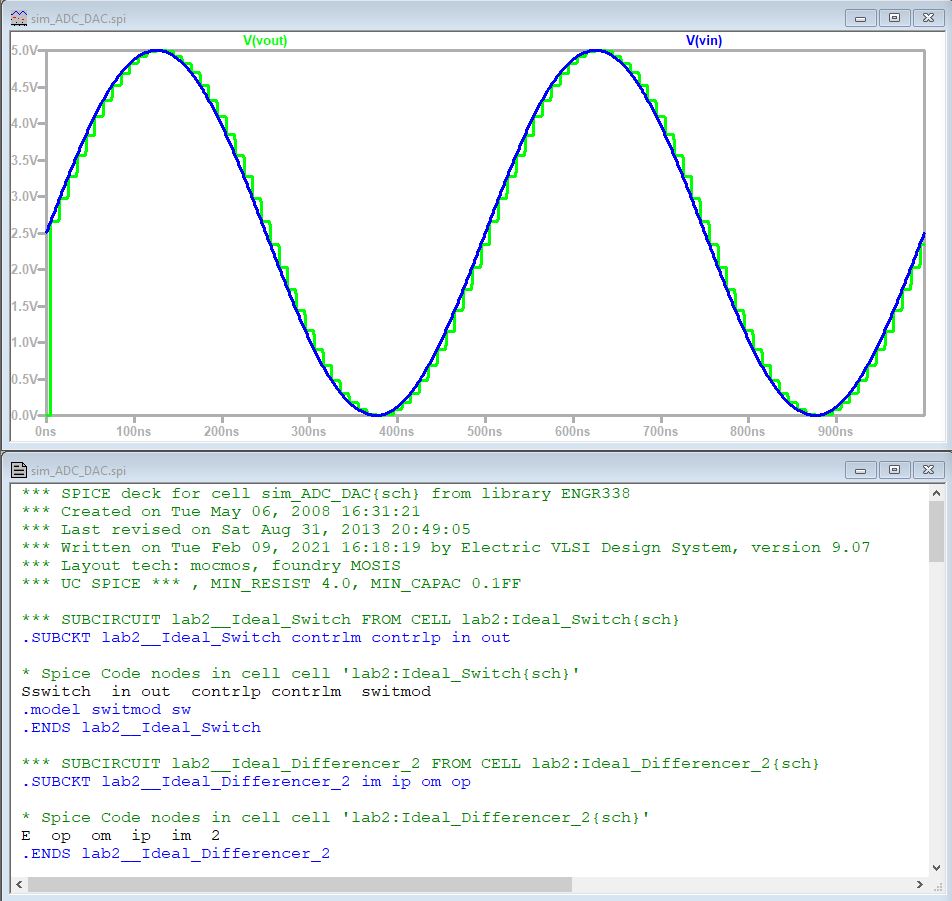

Figure 2: Simulation Results from ADC to DAC

Task 2:

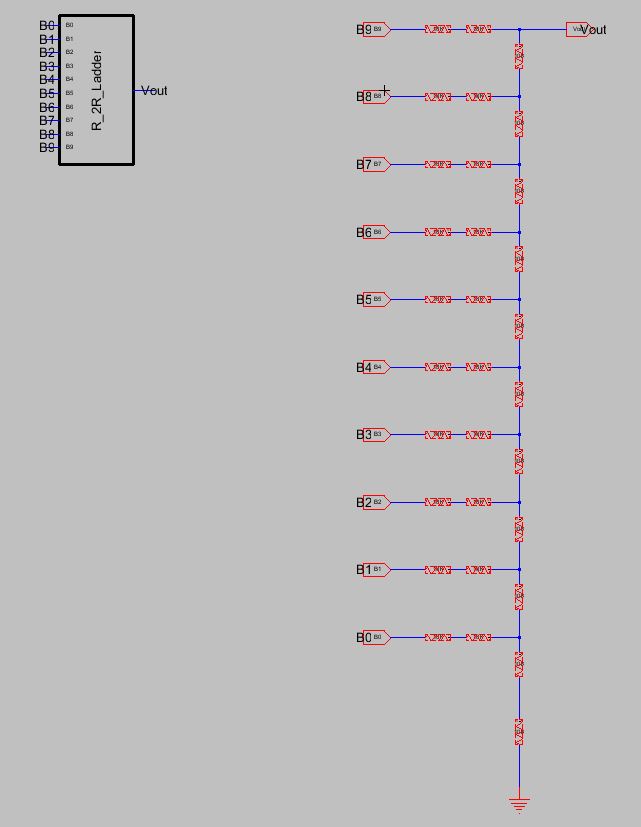

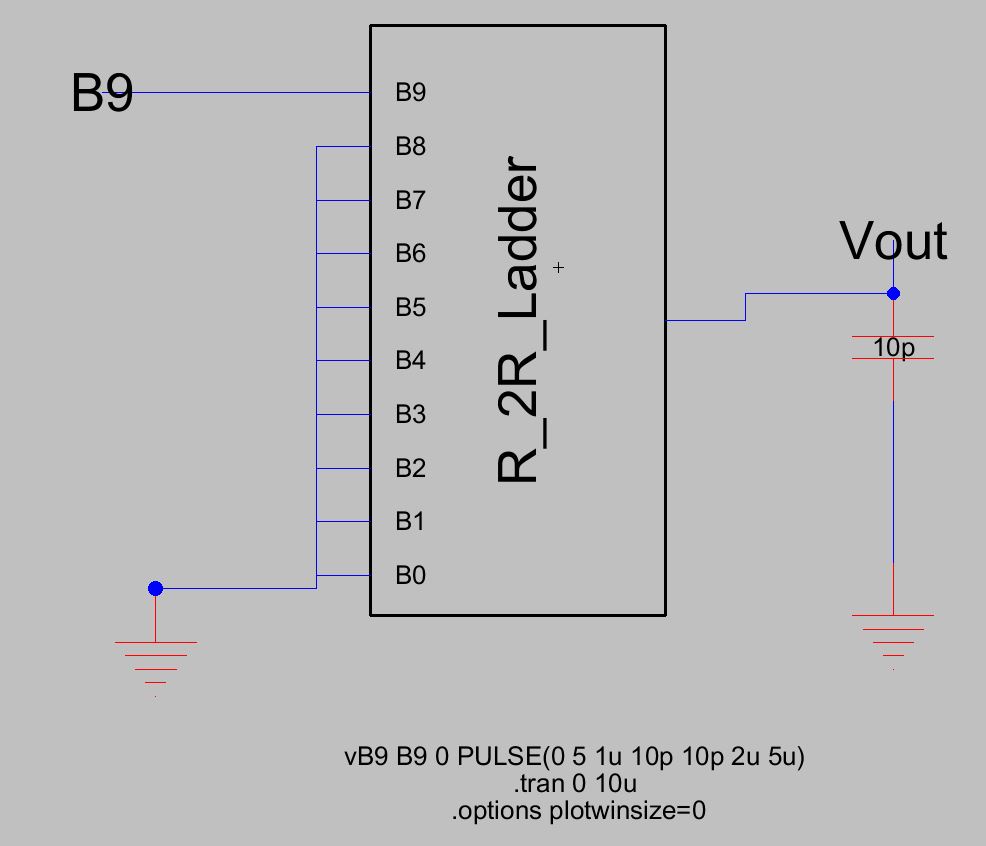

Figure 3: Schmatic of R 2R ladder

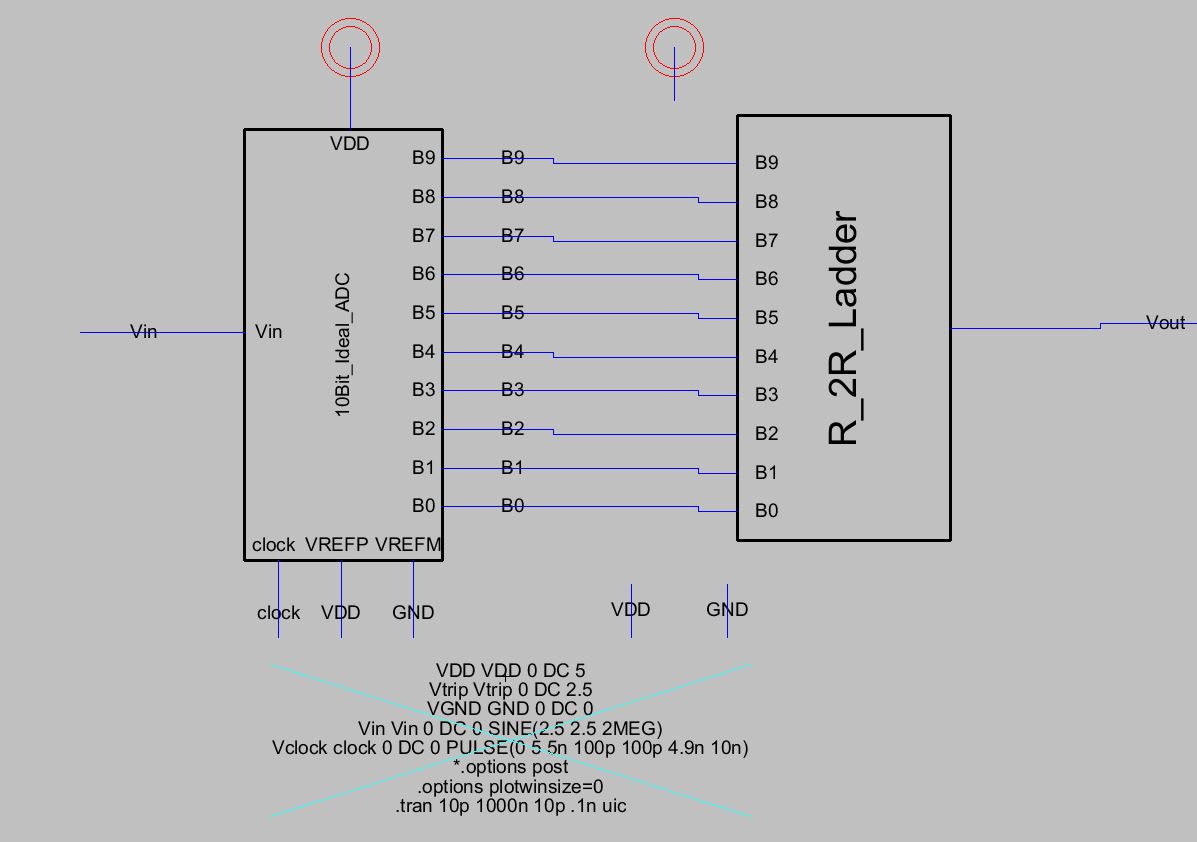

Figure 4: Schematic of ADC to R 2R ladder for sumulation

Figure 5: Simulation Results of ADC to R 2R Ladder

Task 3:

Figure 6: Schematic for time delay

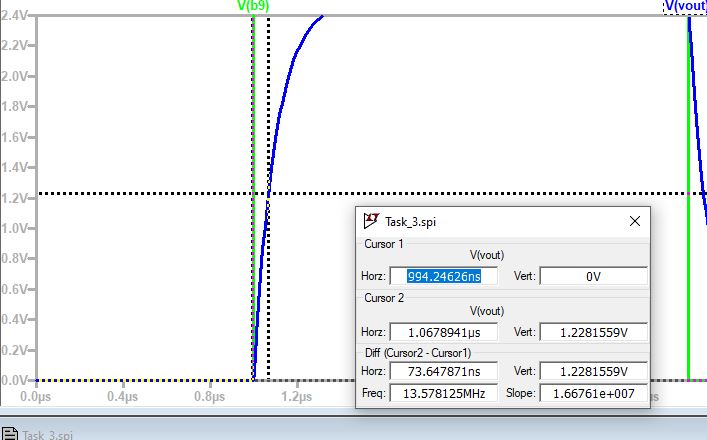

Figure 7: Time Delay confirmation

Conclusion:

This

lab a great lab to start working with Electric VLSI again. In Figure 7

simulation match the results from calcuation of time delay

approximately. Td = 0.7(10K)(10pF) = 7*10^(-8)