ENGR 338 Spring 2021

Final Project: Design an 8-bit SAR ADC

Taylor Nakai

tsnakai@fortlewis.edu

Introduction:

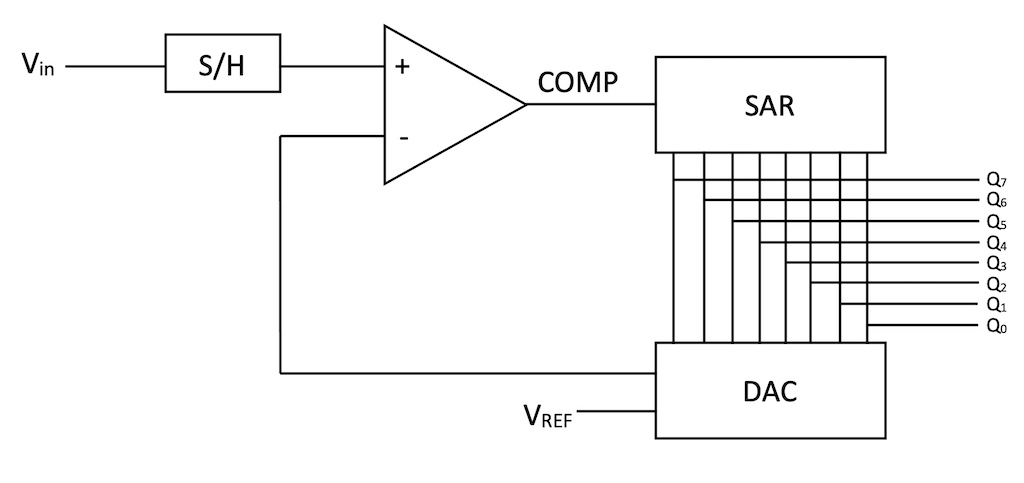

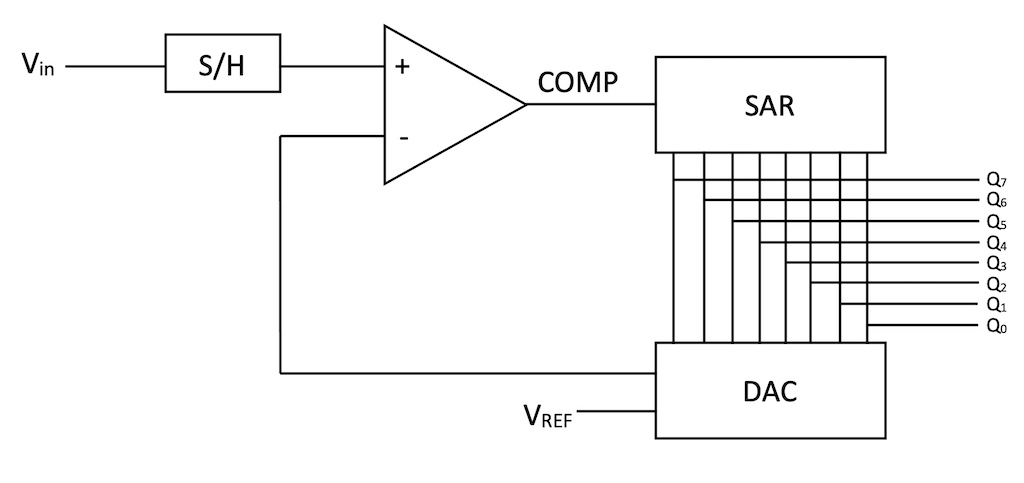

In

this project we were given the task to complete a 8-bit Successive

Approximation Register (SAR) Analog-to-Digital Converter (ADC), as

seen in Figure 1. The advantages of using a SAR ADC is that it is

usually low cost, has a high resolution, and requires low power. The

components of the 8-bit ADC consists of the Sample/Hold (S/H) block,

the comparator, the SAR logic block, 8-bit DAC, and timing block. The

inspiration behind this project was based on the 8-bit SAR ADC graduate

project being completed in the Electrical Engineering Department at

Columbia University. The project was pivoted to just complete the 8-bit

SAR block due to time constraints. This project implemented the 50 nm

CMOS technology. In order to complete the 8-bit SAR block, we needed to

build a 3-input NAND gate, build a TI D-Flip-Flop, and build the 8-bit

SAR Block. With each component that was build, we used LTSpice to

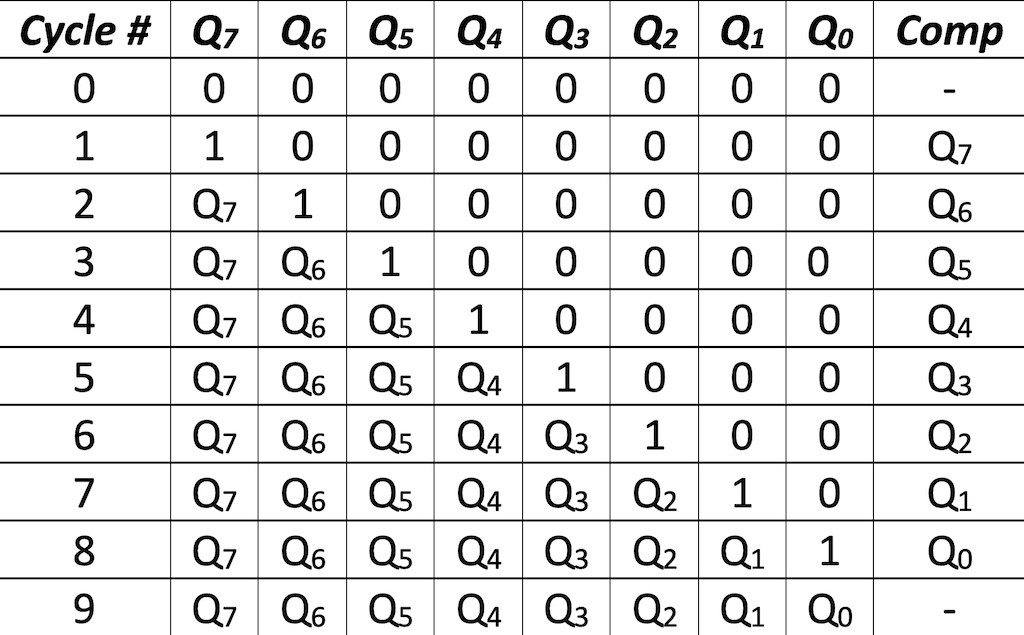

perform simulations to verify the logic of the component. The finite

state machine of the 8-bit SAR ADC is shown in Figure 2.

Figure 1. 8-bit SAR ADC.

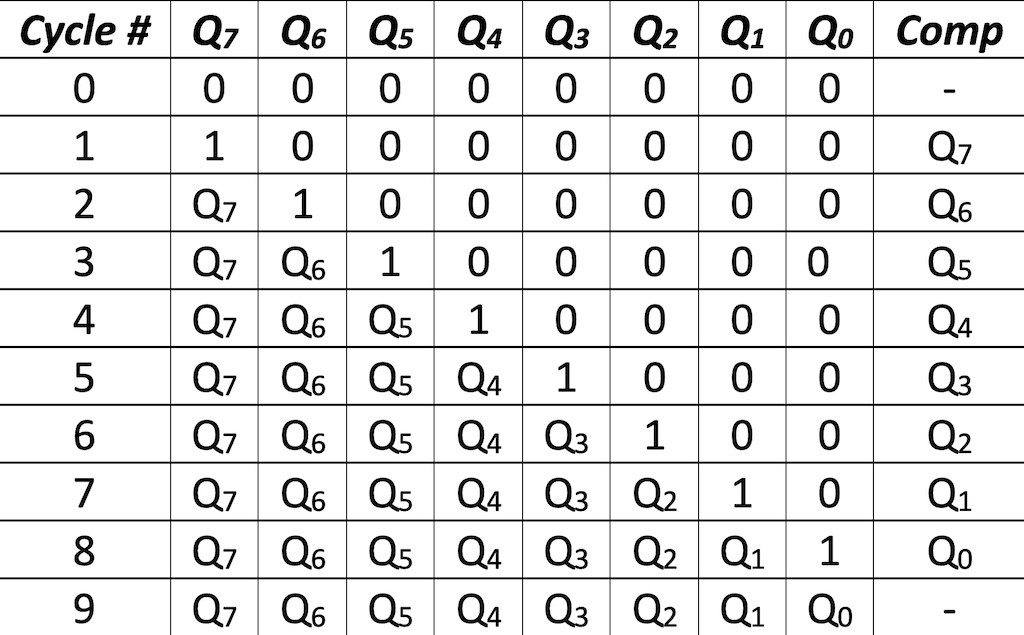

Figure 2. 8-bit SAR finite state machine.

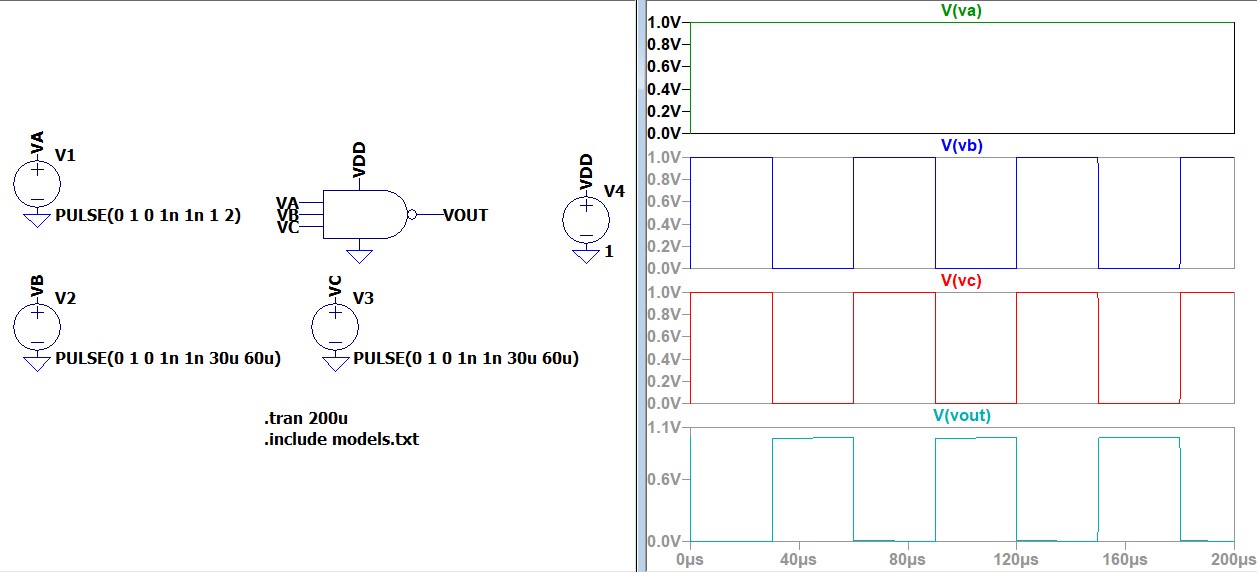

3-Input NAND Gate:

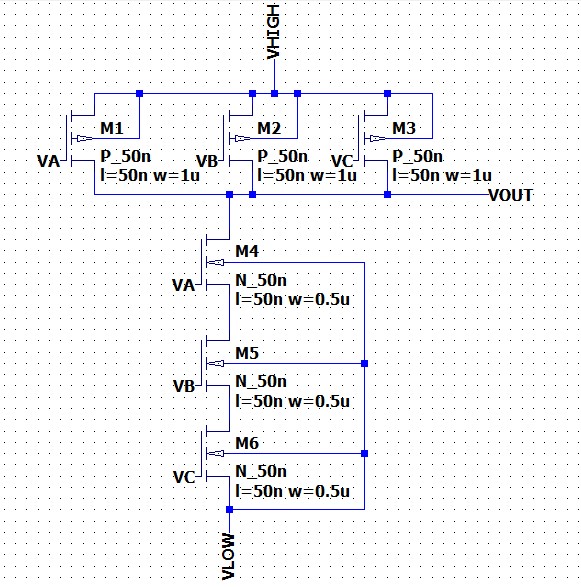

A

3-input NAND gate needed to be created using the 50nm technology so

that the TI D-Flip-Flop could be created. Using LTSpice, a schematic

was created and the NAND gate was implemented using PMOS and NMOS

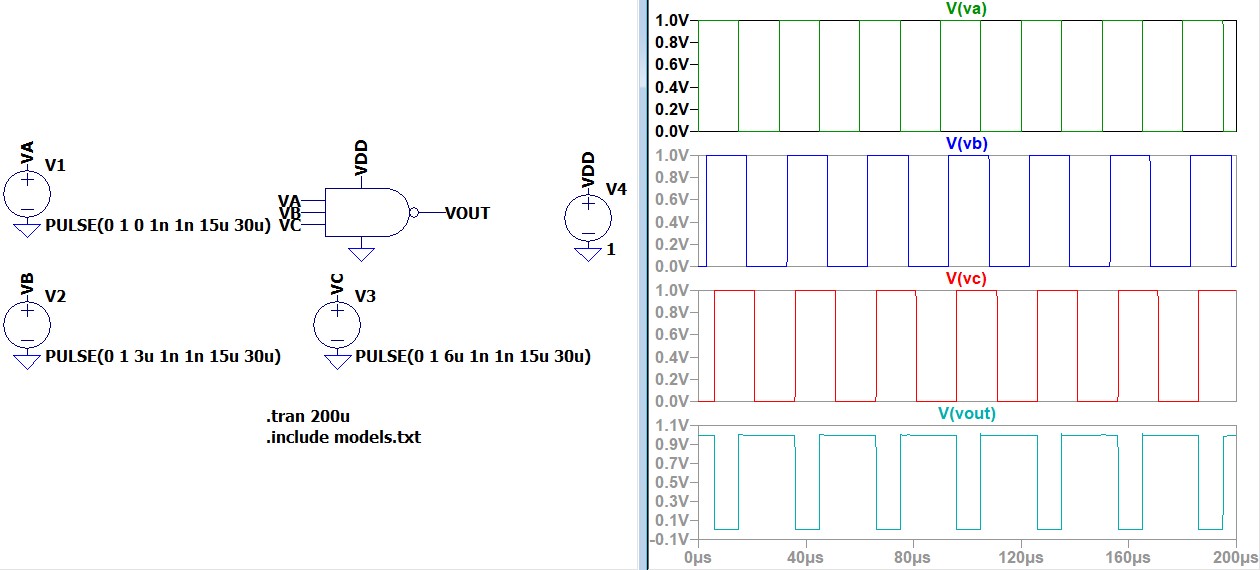

transistors as shown in Figure 3. Once the schematic was completed, a

symbol for the NAND gate was created. Using the symbol, two simulations

were conducted to verify the logic of the NAND gate, shown in Figure 4

and 5, as the NAND gate needed to function correctly as it is used in

the TI D-Flip-Flop.

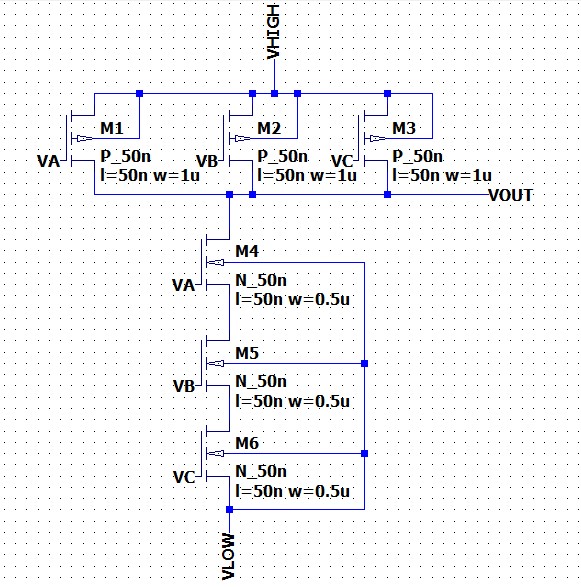

Figure 3. Schematic of 3-input NAND gate using the 50nm process.

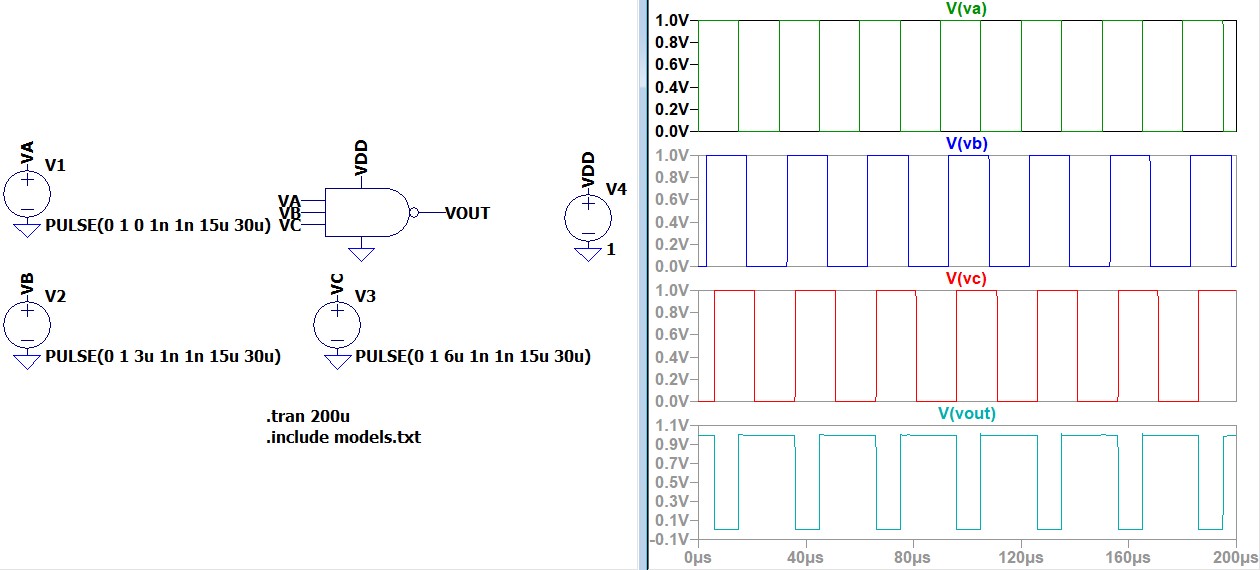

Figure 4. Simulation 1 of 3-input NAND gate using LTSpice to verify logic.

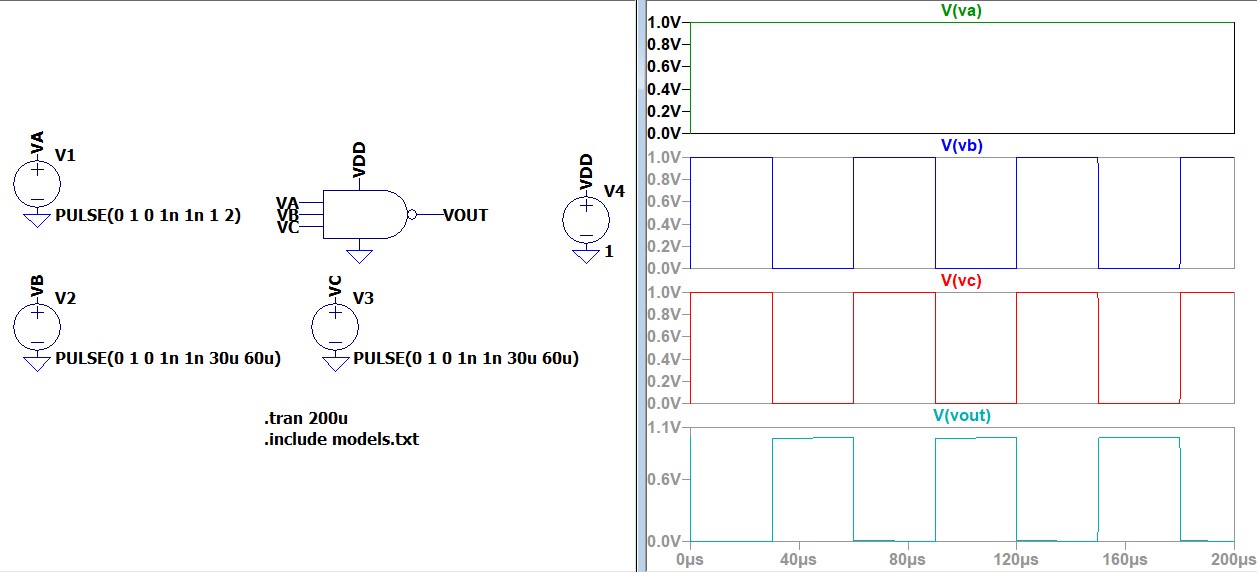

Figure 5. Simulation 2 of 3-input NAND gate using LTSpice to verify logic.

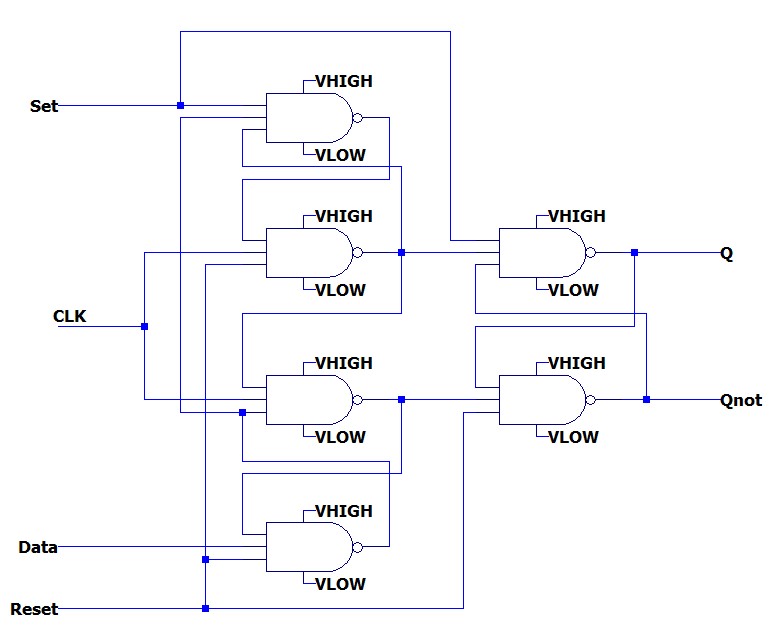

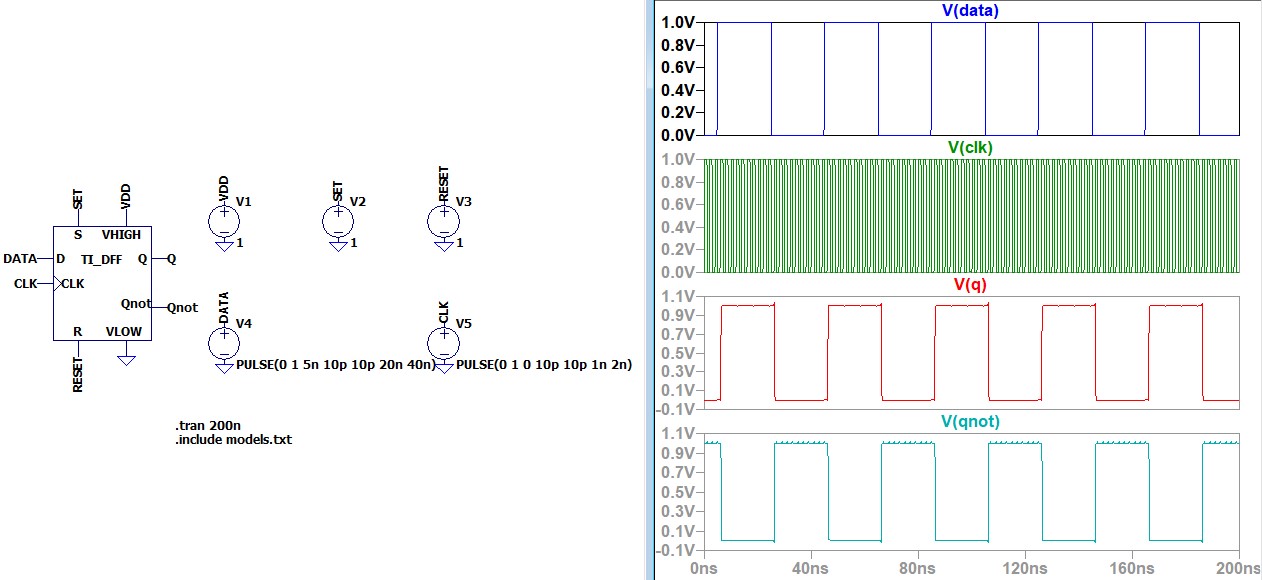

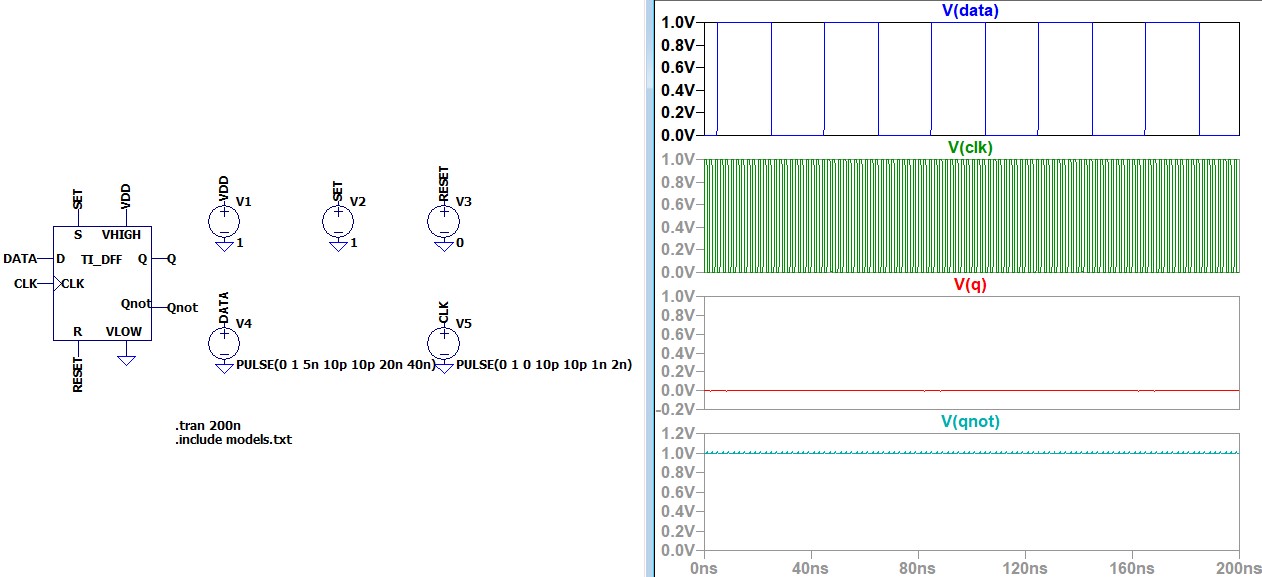

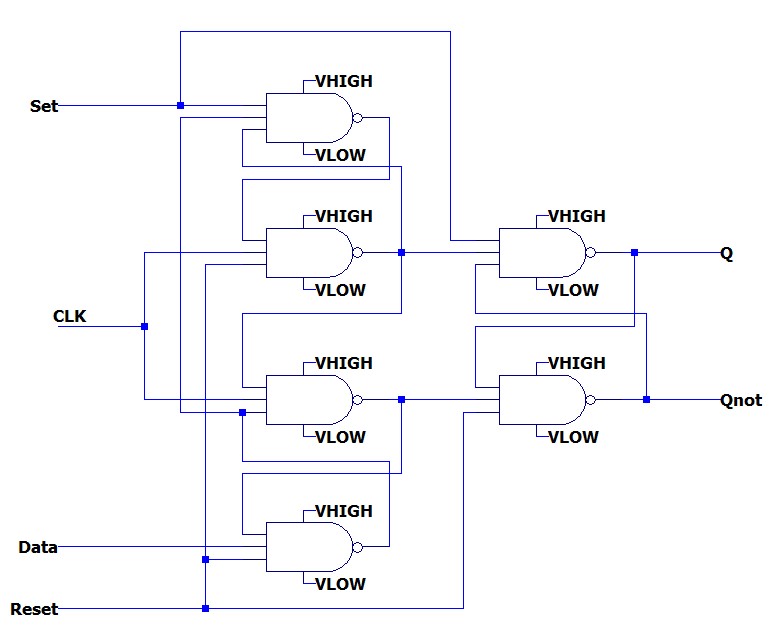

TI-DFF:

A

TI D-Flip-Flop was needed as it would be implemented within the SAR

block for the sequencer and the shift register. Using LTSpice, a

schematic was created and the TI D-Flip-Flop was implemented using the

3-input NAND gate created previously, as shown in Figure 6.

Once the schematic was completed, a symbol for the TI D-Flip-Flop was

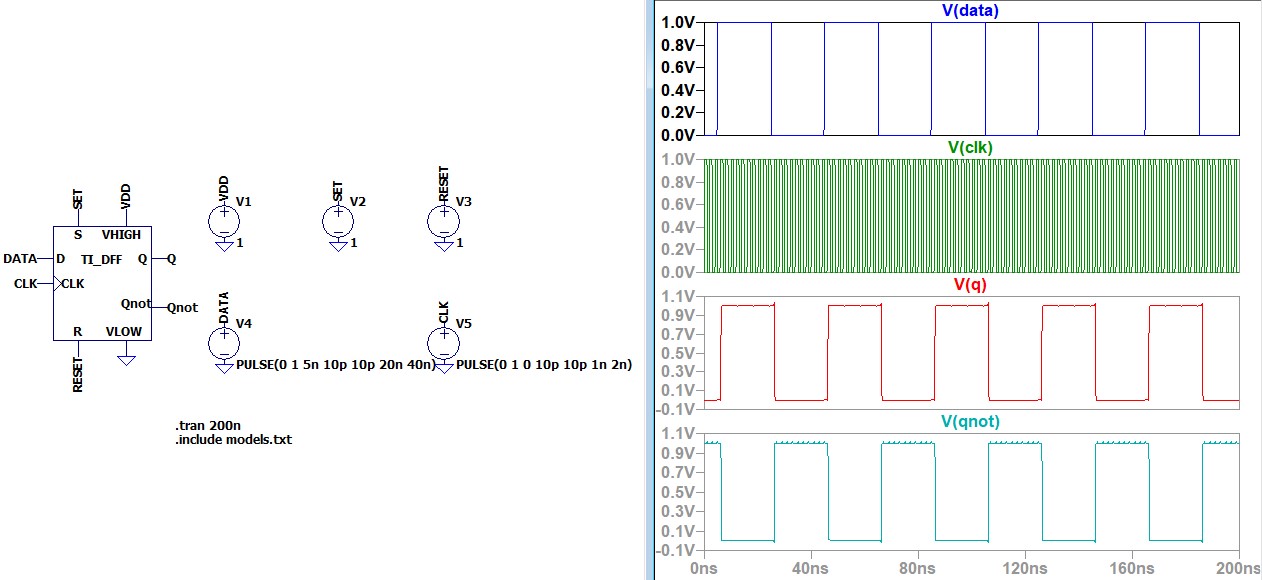

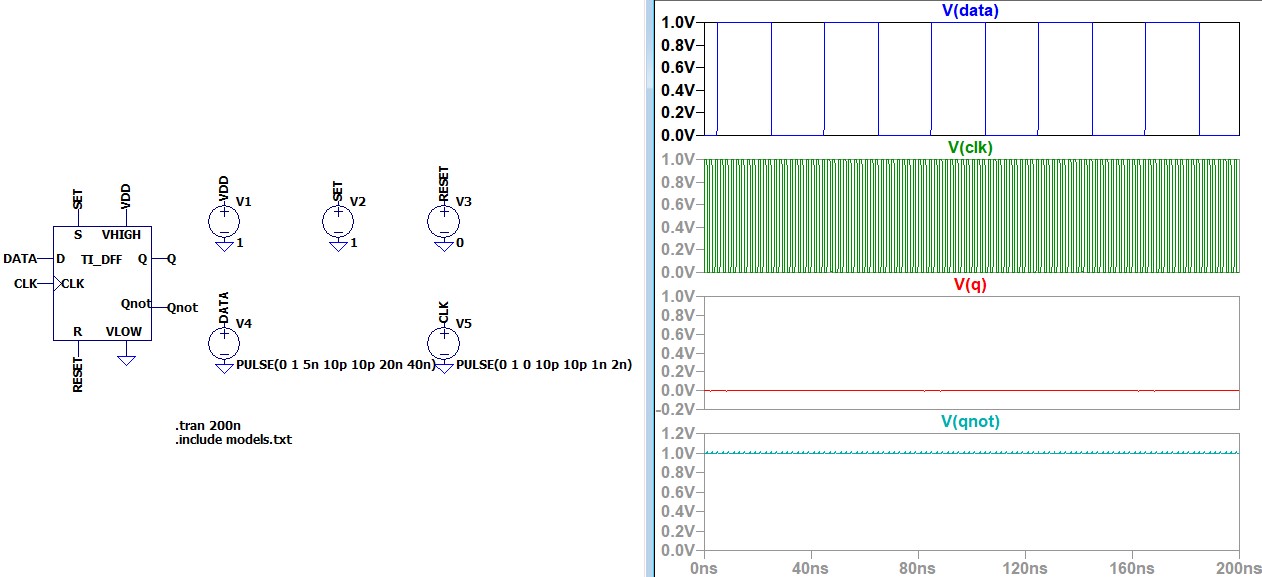

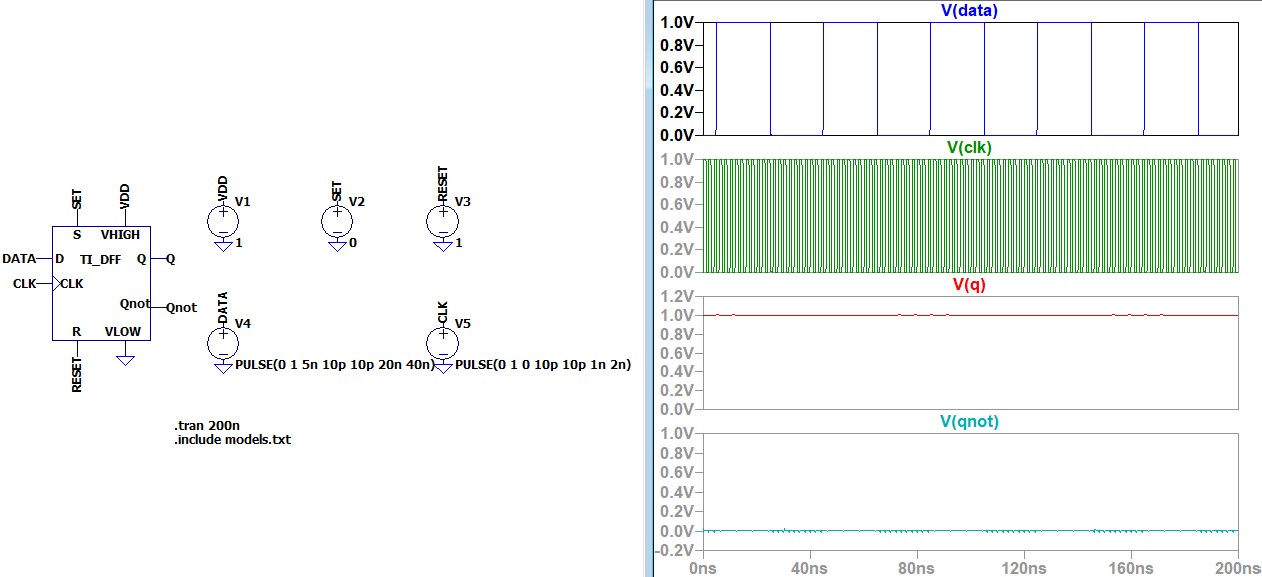

created. Using the symbol, three simulations were conducted to verify

the

logic of the TI D-Flip-Flop testing the set and reset functionalities,

shown in Figure 7 through 9. The TI D-Flip-Flop needed to function

correctly as it is a critical component within the SAR block, so

testing the different possibilities was required.

Figure 6. Schematic of TI D-Flip Flop using 3-input NAND gates.

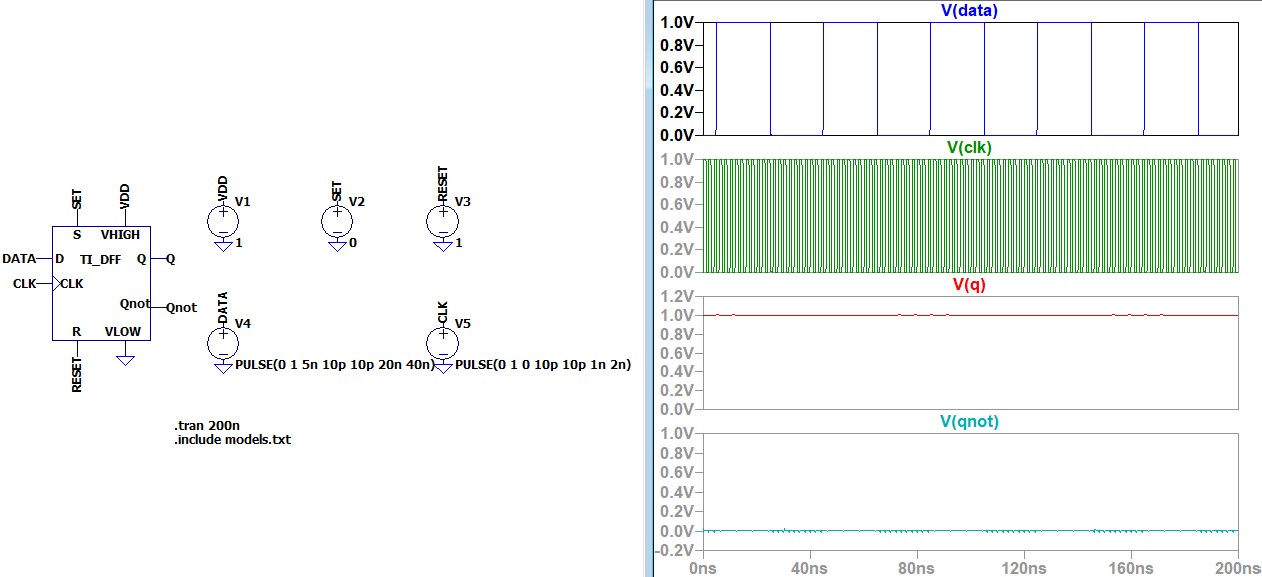

Figure 7. Simulation 1 of TI D-Flip Flop using LTSpice to verify logic.

Figure 8. Simulation 2 of TI D-Flip Flop using LTSpice to verify logic.

Figure 9. Simulation 3 of TI D-Flip Flop using LTSpice to verify logic.

8-bit SAR:

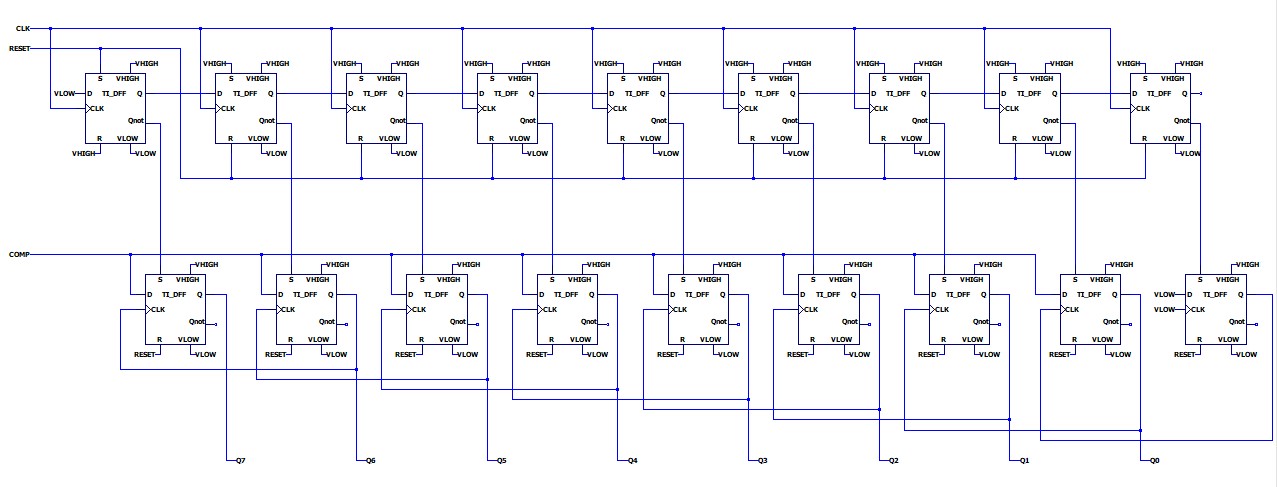

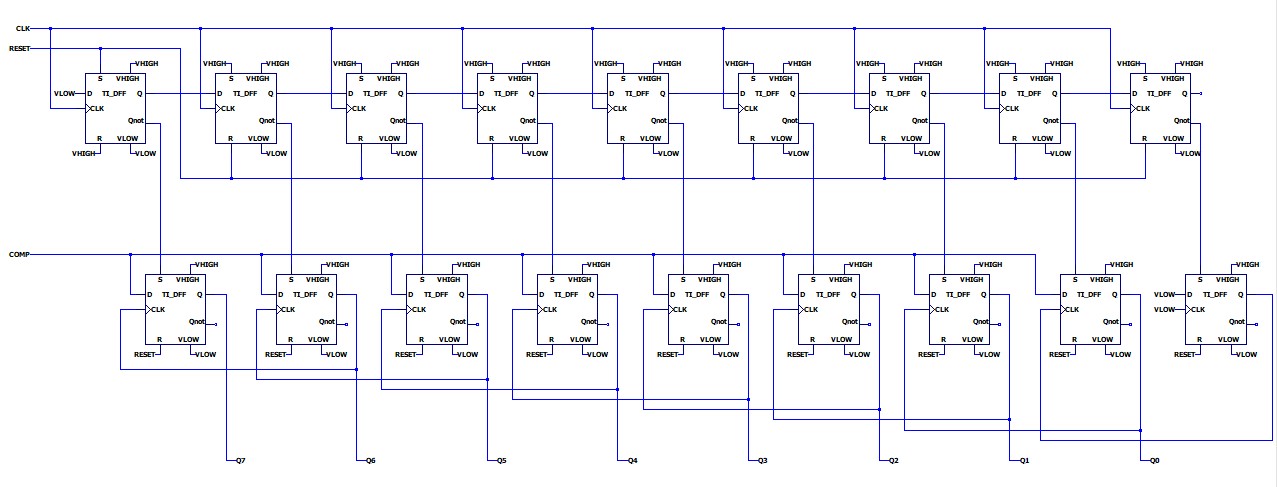

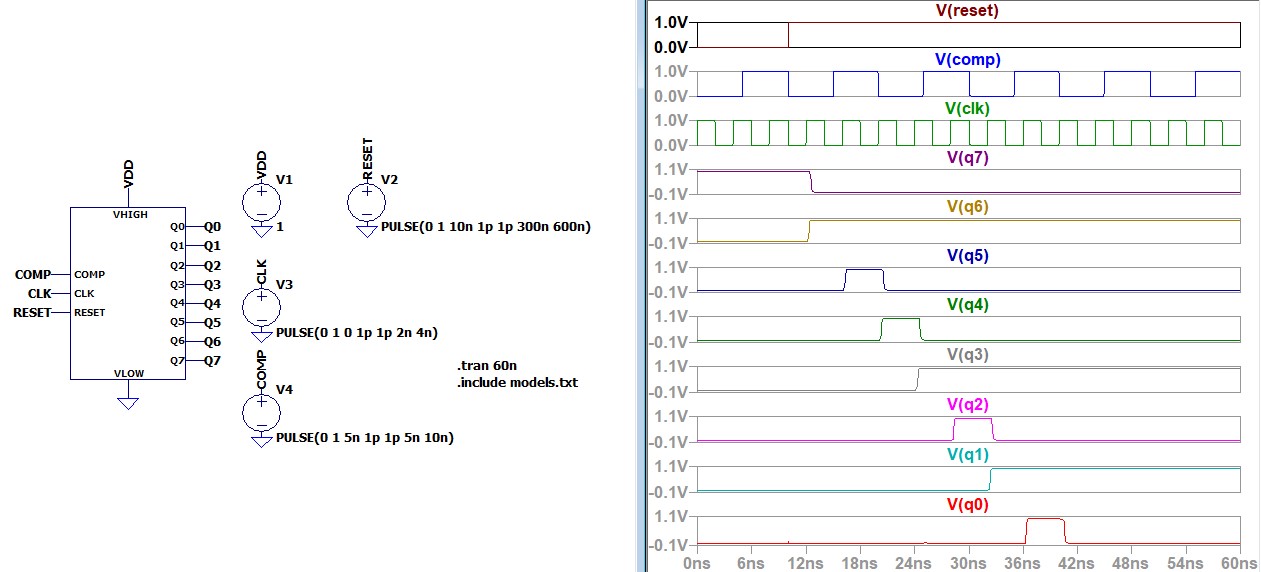

The

SAR block was finally able to implement using the components that were

made. In order to create the SAR block, two units needed to be

implemented using the TI D-Flip-Flop, the sequencer and the shift

register. The

registers of the sequencer are in charge of providing the sequence and

the shift registers are responsible for saving the state. Using

LTSpice, a schematic was created and the SAR block was created using

the TI D-Flip-Flop, as seen in Figure 10. Once the schematic was

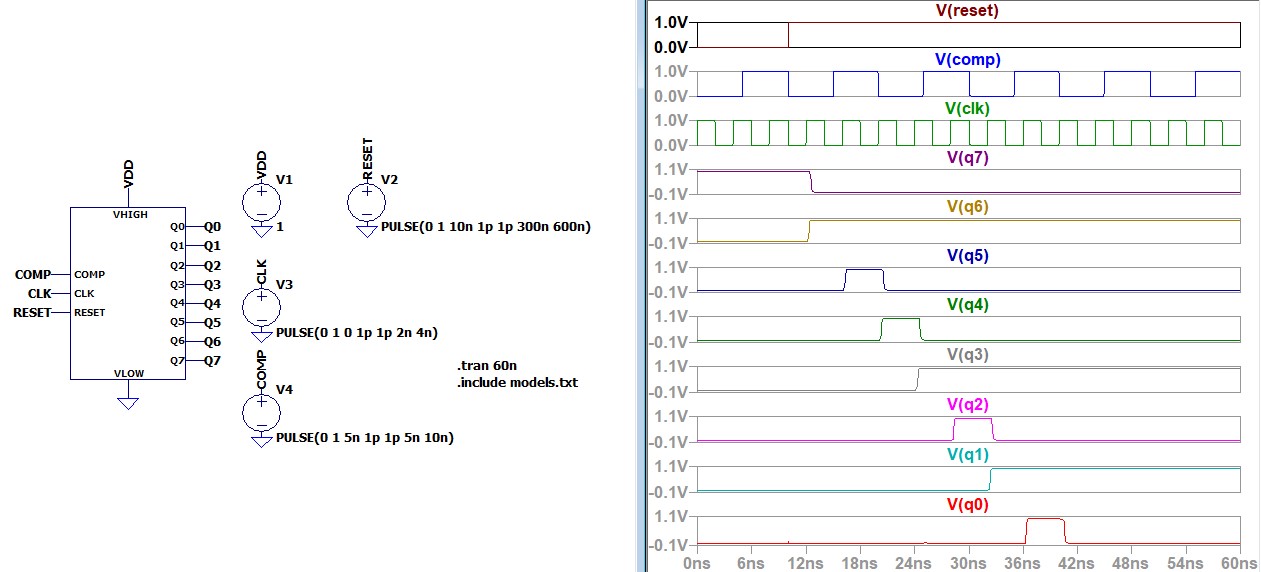

completed, a symbol for the SAR block was created. Using the symbol, a

simulation was conducted to verify that the SAR block worked as

designed, as shown in Figure 11.

Figure 10. Schematic of 8-bit SAR using TI D-Flip Flop.

Figure 11. Simulation of 8-bit SAR using LTSpice to verify the logic.

Discussion:

Completing this project,

allowed us to learn about the SAR ADC and all the components that are

associated with it, especially the SAR block. By creating the SAR

block, we were able to get to see the components that are implemented

within. This project was interesting as we got implement the component

and test the component to ensure correct functionality, which required

us to use the skills that we had acquired over the course of the

semester. Unfortunately, we were not able to implement the entire SAR

ADC due to time constraints but were able to implement an important

part of the SAR ADC.