CE 433 Spring 2022

Basics Tutorial

Taylor Nakai

tsnakai@fortlewis.edu

Introduction:

In

this homework we were given the tasks to review vim basics and review

verilog basics. To review vim basics, we needed to download vim and

look over the different commands that vim has to offer. Reviewing

verilog basics, we learned about structural modeling, dataflow

modeling, behavioral modeling, blocking (sequential) and non-blocking

(concurrent) in behavioral modeling, timing and delay in modeling, and

hierarchical module representation. mvim and vivado were used to complete these tasks.

Task 1:

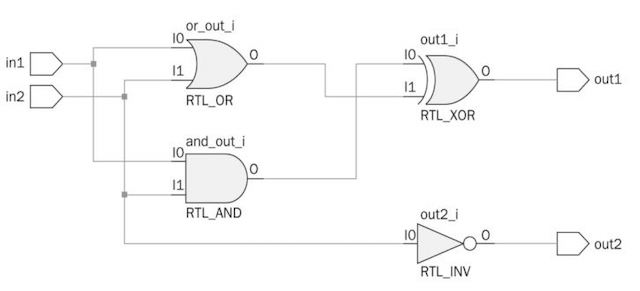

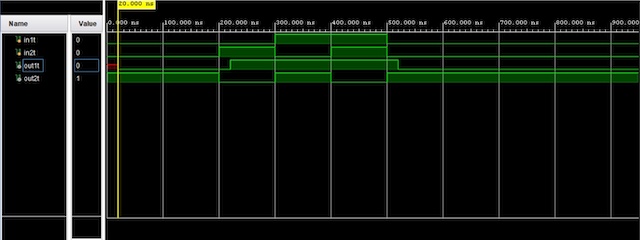

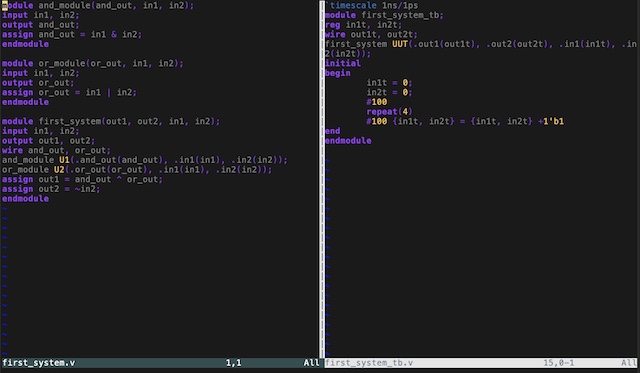

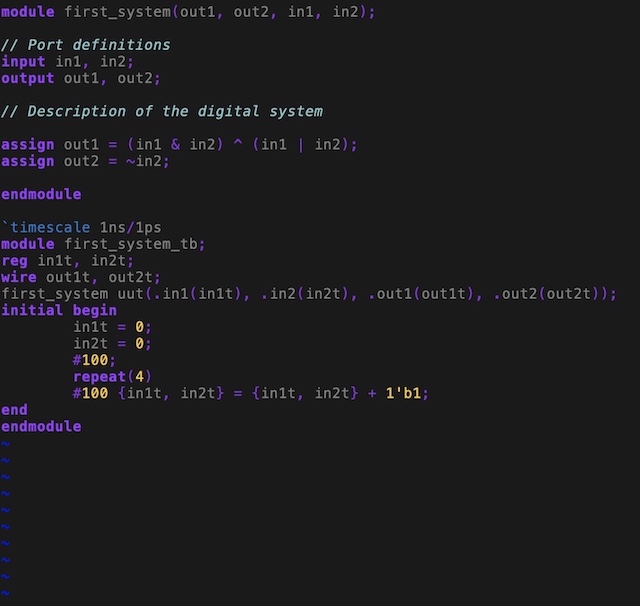

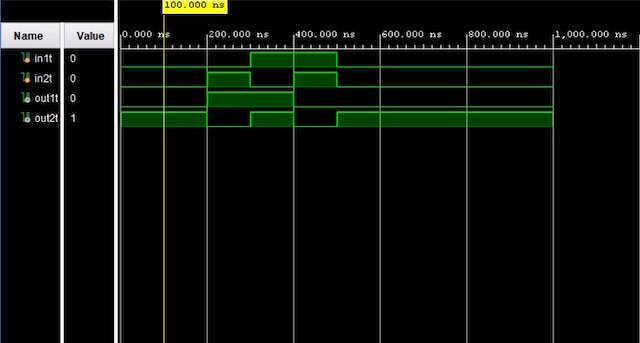

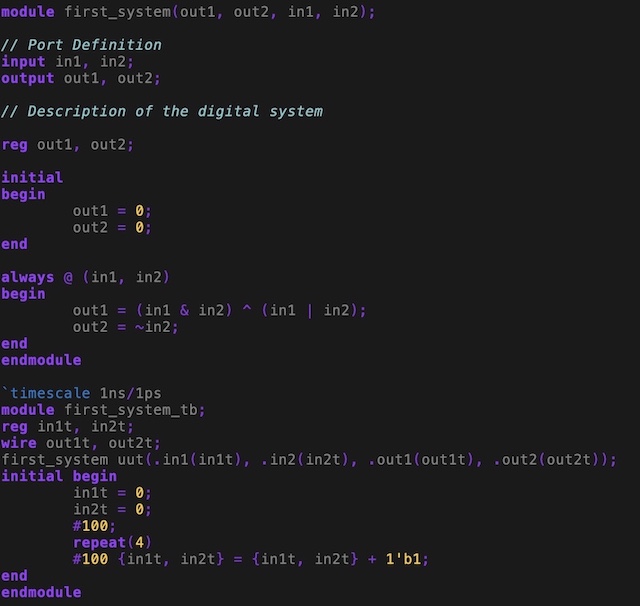

In

the first task, we were introduced to the three modeling methods:

structural modeling, dataflow modeling, and behavioral modeling. These

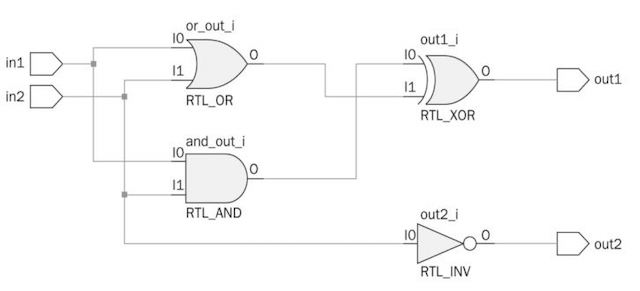

three methods were used to model the example schematic shown in Figure

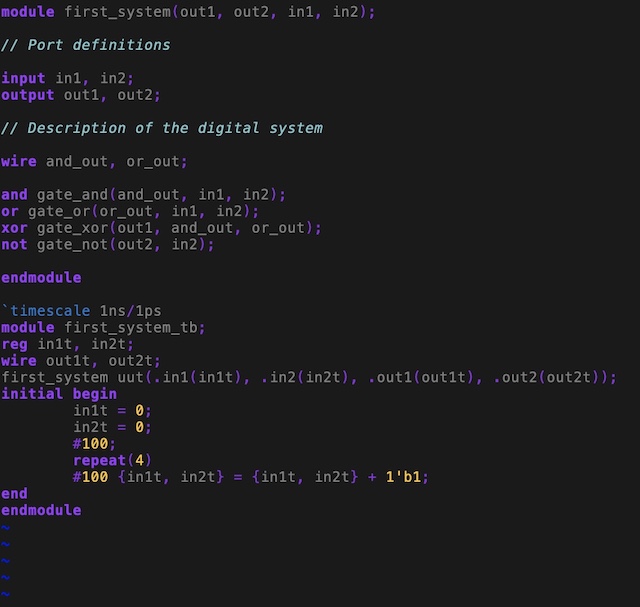

1. Using the structural modeling method, we modeled the example and

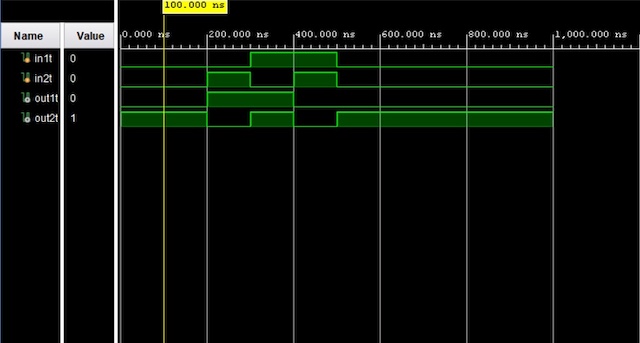

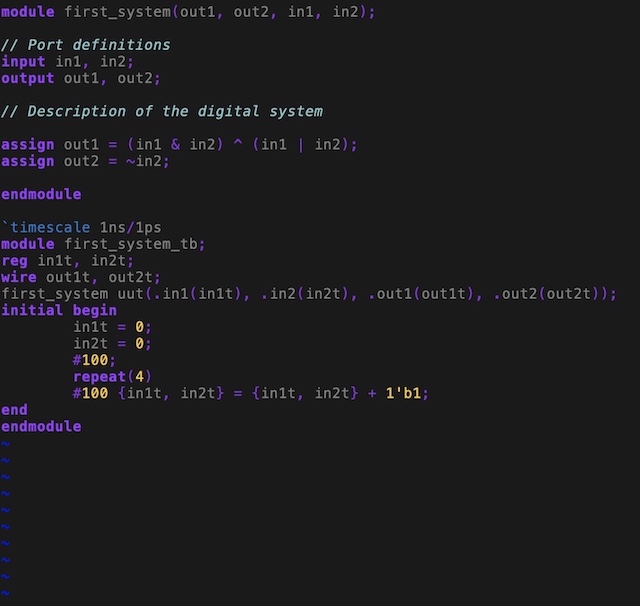

showed the results shown in Figure 2. Using the dataflow modeling method, we modeled the example and showed the results shown in Figure 3. Using the behavioral modeling method, we modeled the example and showed the results shown in Figure 4.

Figure 1. Example schematic that will be used to model.

Figure 2. Structural modeling of example schematic with vivado simulation.

Figure 3. Dataflow modeling of example schematic with vivado simulation.

Figure 4. Behavioral modeling of example schematic with vivado simulation.

Task 2:

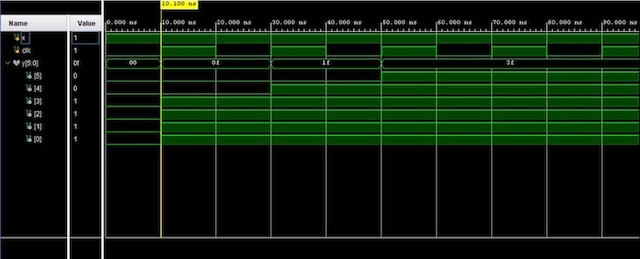

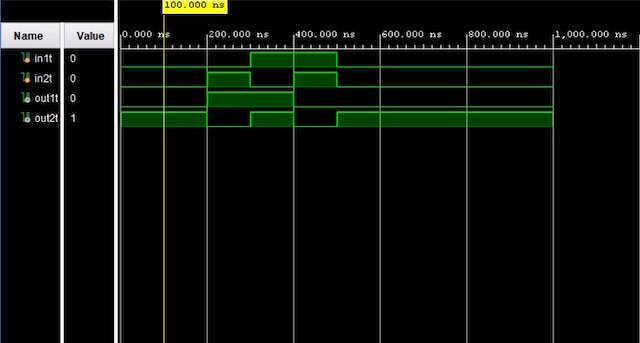

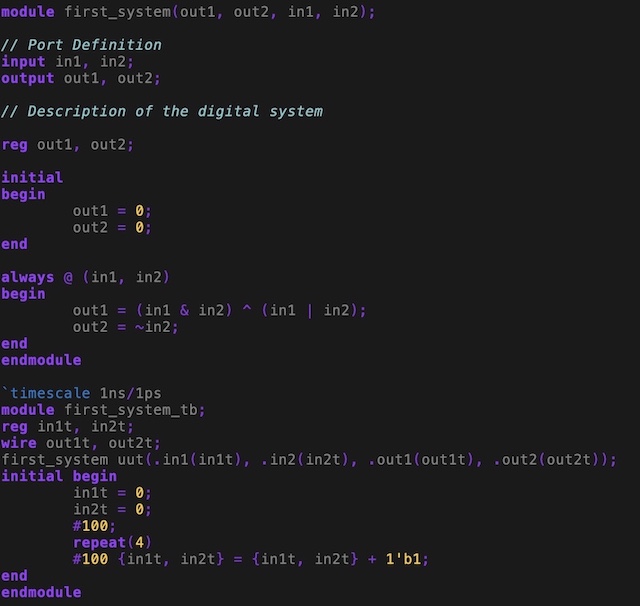

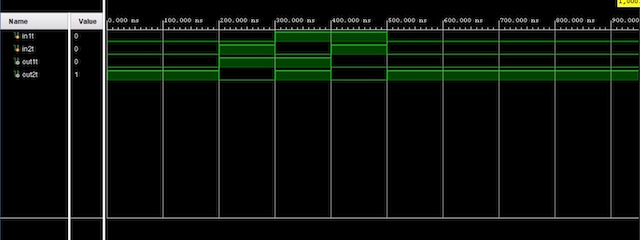

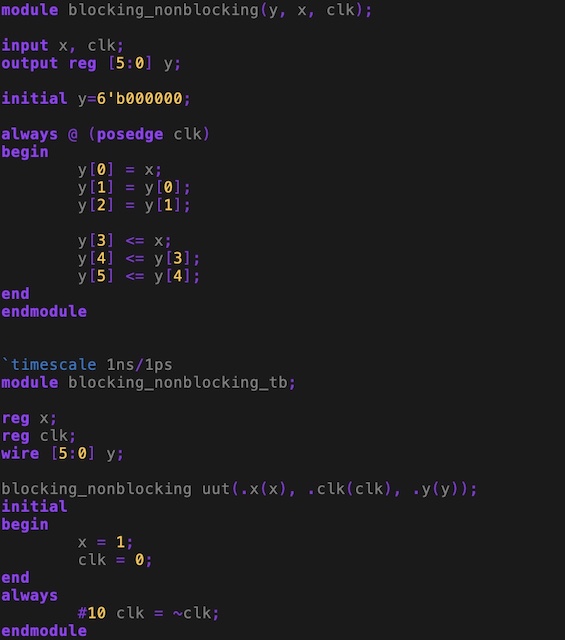

In

the second task, we learned about the blocking (sequential) and

non-blocking (concurrent) in behavioral modeling. An example to show

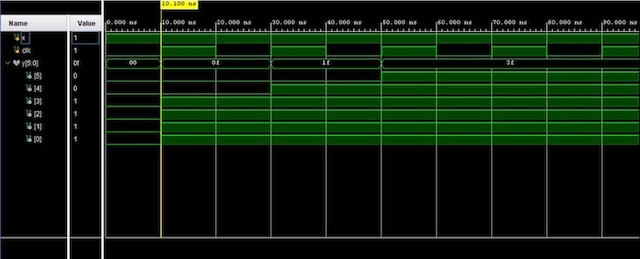

how blocking and non-blocking works is shown in Figure 5. We can see

the difference in how y[0] - y[2] are affected compared to y[3] - y[5].

We also learned that it is strongly suggested that blocking should be

used in combinational circuits while non-blocking should be used in

sequential circuits.

le

le

Figure 5. Behavioral modeling of blocking and non-blocking with vivado simulation.

Task 3:

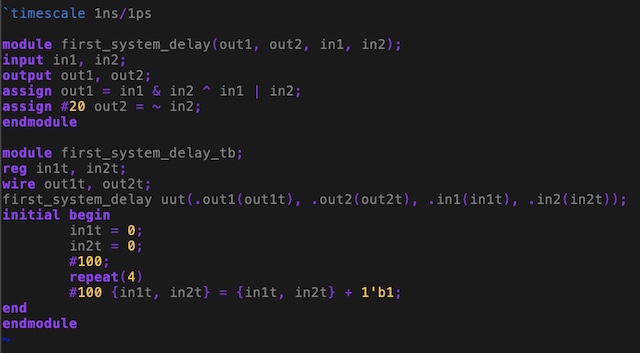

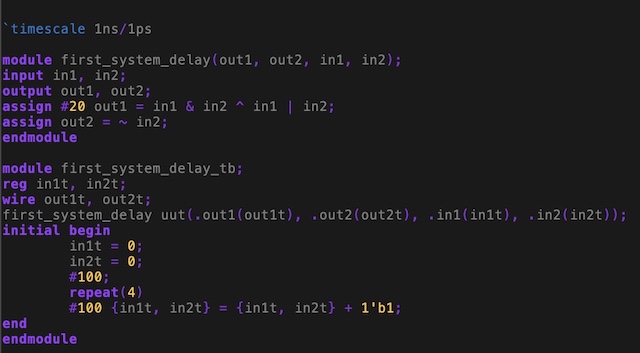

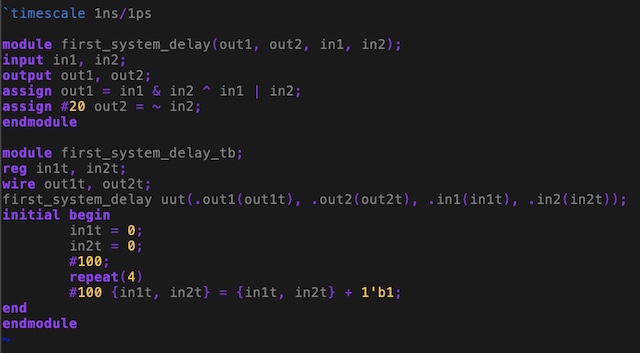

In

the third task, we learned about the timing and delay in modeling. To

give a good representation of timing and delay we ran the example given

as shown in Figure 6.

Figure 6. Timing and delay example given with vivado simulation.

Task 4:

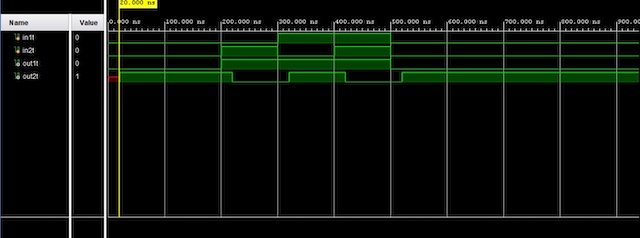

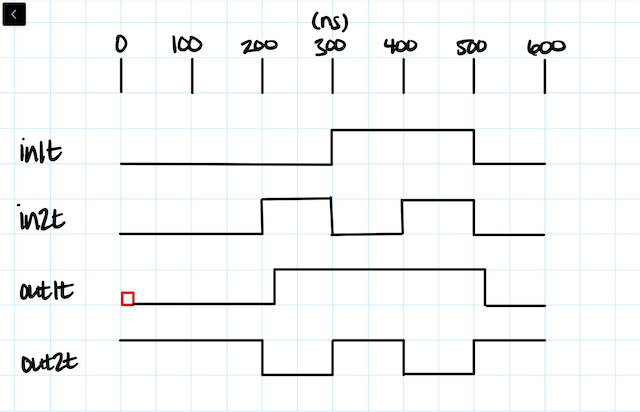

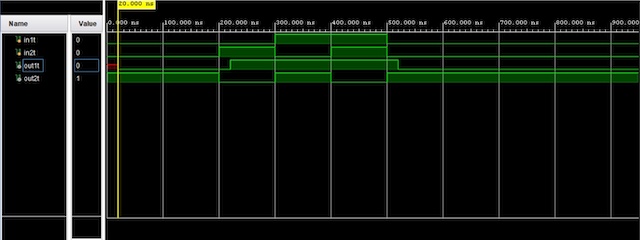

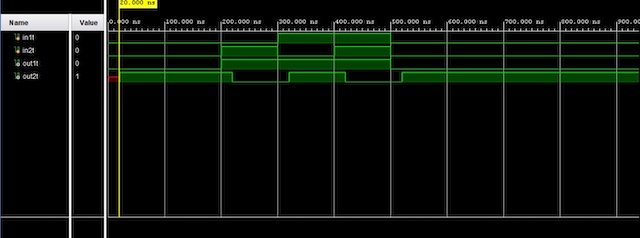

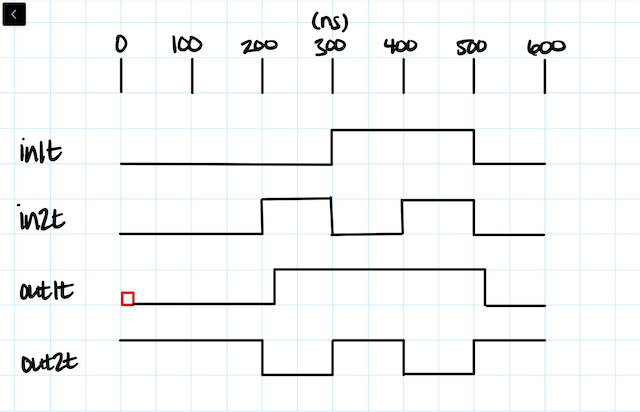

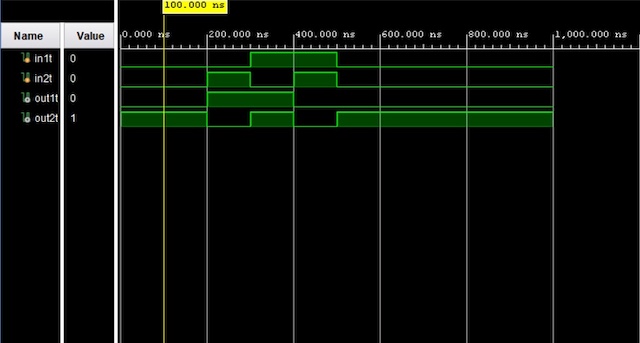

In the fourth task, we

expanded learning about the timing and delay in modeling. We modified

task 3 so that the 20 ns delay was moved to the line above instead and

we were asked to hand draw the timing diagram. The timing diagram is

shown in Figure 7. The simulation results of the example are shown in

Figure 8 and match the hand drawn timing diagram.

Figure 7. Hand drawn timing diagram.

Figure 8. Timing and delay example given with vivado simulation showing the same results as the hand drawn diagram.

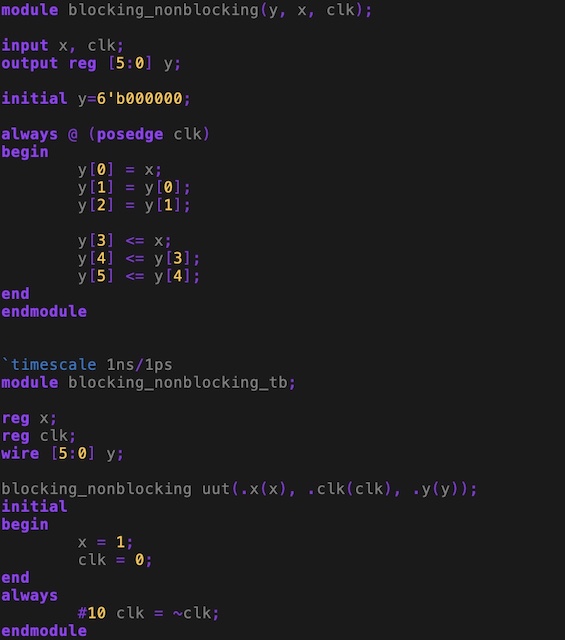

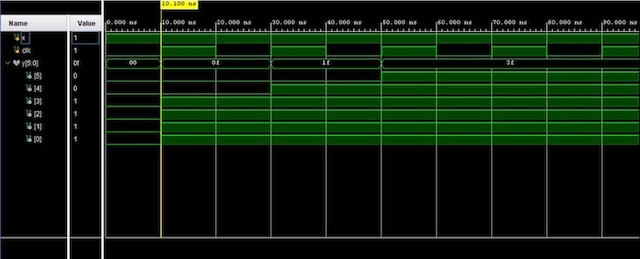

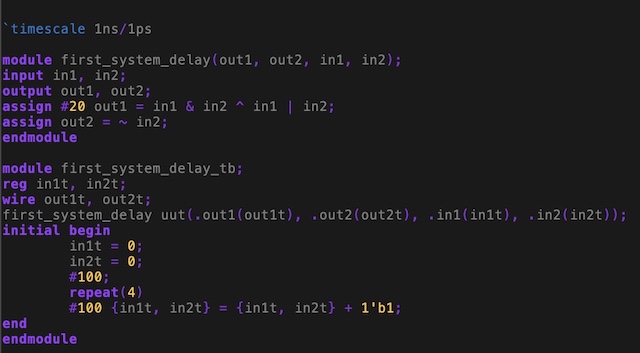

Task 5:

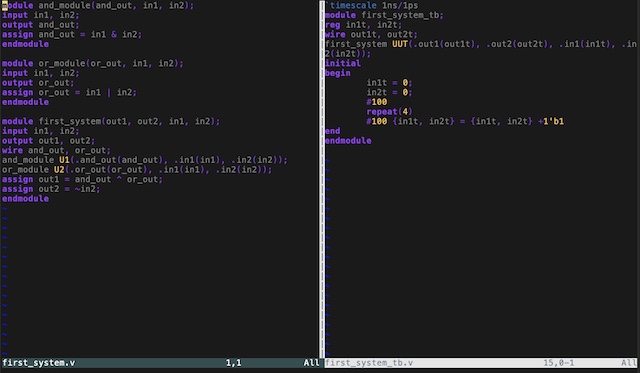

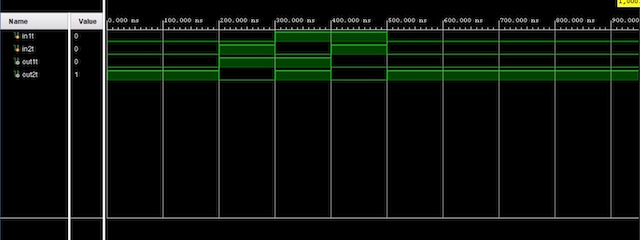

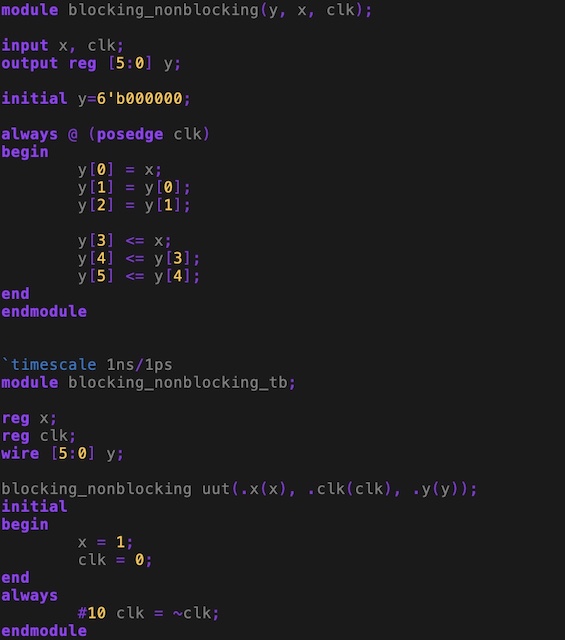

In

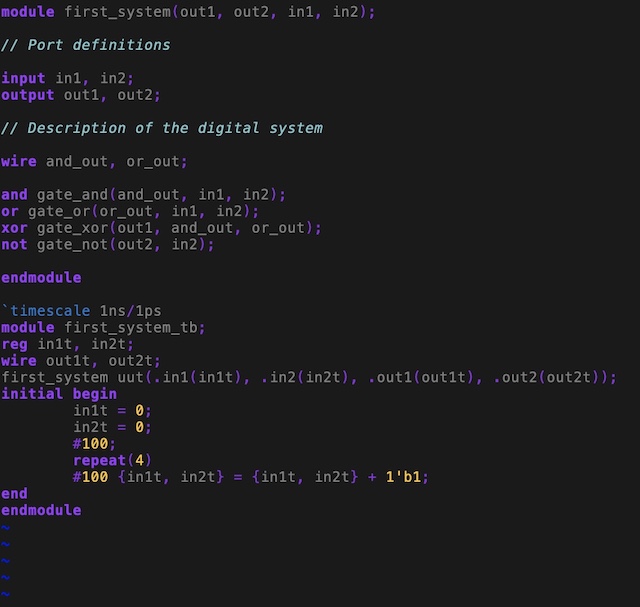

the fifth task, we learned about hierarchical module representation. We

were given an example where multiple modules were included in one '.v'

file and we were able to create a testbench for it. The simulation

results are shown in Figure 9, which verifies the logic.

Figure 9. First system example with vivado simulation results.

Discussion:

By

completing this homwork, we were able to get a better understanding of

the three modeling methods, blocking and non-blocking in behavioral

modeling, timing and delay, and hierarchical module representation.

This homework allowed me to develop my skills using verilog, vim, and

vivado. I am able to see the value of learning these skills as I can

see myself applying them in the industry. Overall, this homework was

really helpful and look forward to the rest.

....................................................................

le

le

le

le