Figure 1. NMOS_IV{sch} final design with LTSpice code and DRC/NRC scans passed

Figure 2. NMOS_IV{lay} final design with LTSpice code and ERC scan passed

Both of these designs were ran and simulated a waveform in LTSpice for us to see the various outcomes. The results from both NMOS designs can be seen below in Figures 3 and 4.

Figure 3. NMOS_IV{sch} LTSpice waveform results from "Id" probed

A quick side-note, for what ever reason, the waveform would display upside down if "Is" (source current) was probed instead of "Id" (drain current). This is irregular because every other waveform created by the other NMOS and PMOS designs all had appropriate orientations when probing "Is".

Figure 4. NMOS_IV{lay} LTSpice waveform results from "Is" probed

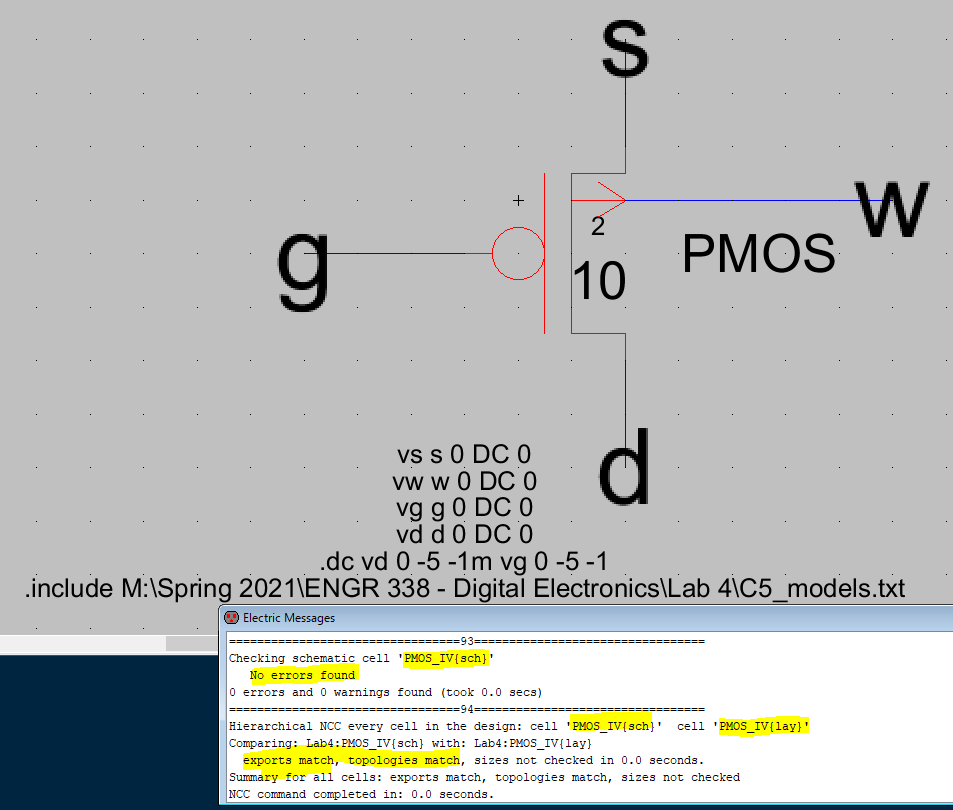

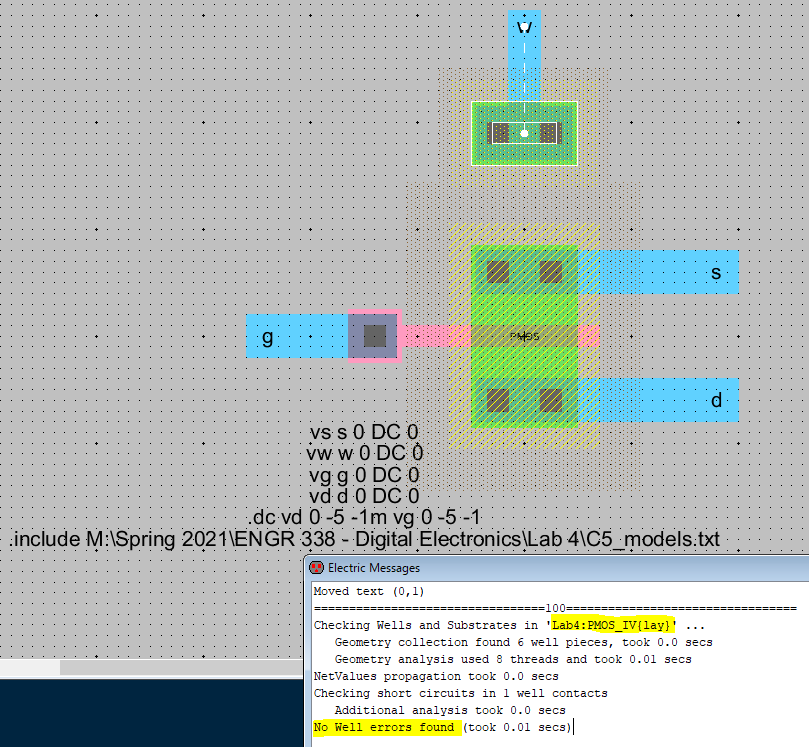

The same process was done for the PMOS with the development of the schematic and layout which can be seen in Figures 5 and 6.

Figure 5. PMOS_IV{sch} final design with LTSpice code and DRC/NRC scans passed

Figure 6. PMOS_IV{lay} final design with LTSpice code and ERC scan passed

The same process was done for the PMOS with the development of the schematic and layout which can be seen in Figures 5 and 6.

Figure 5. PMOS_IV{sch} final design with LTSpice code and DRC/NRC scans passed

Figure 6. PMOS_IV{lay} final design with LTSpice code and ERC scan passed

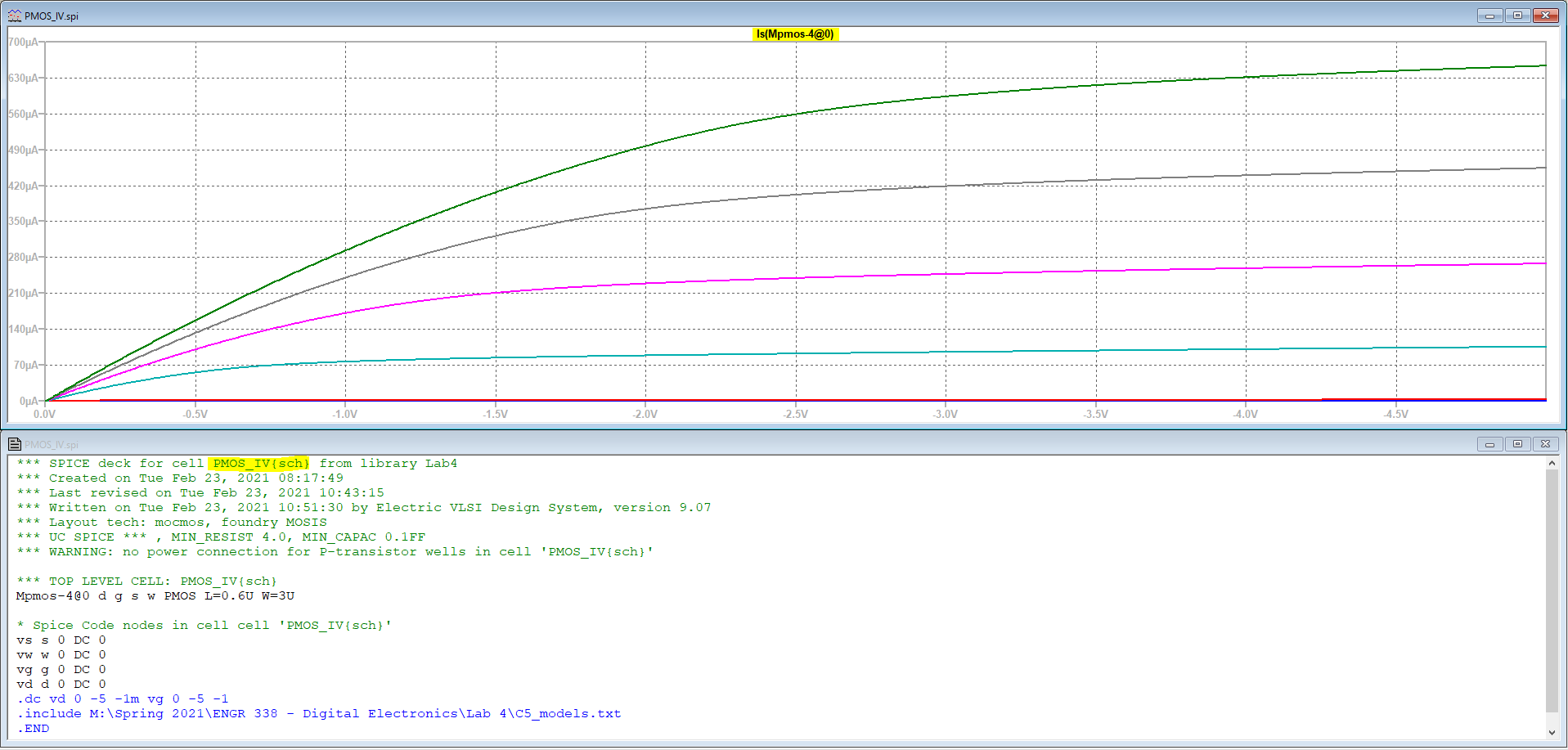

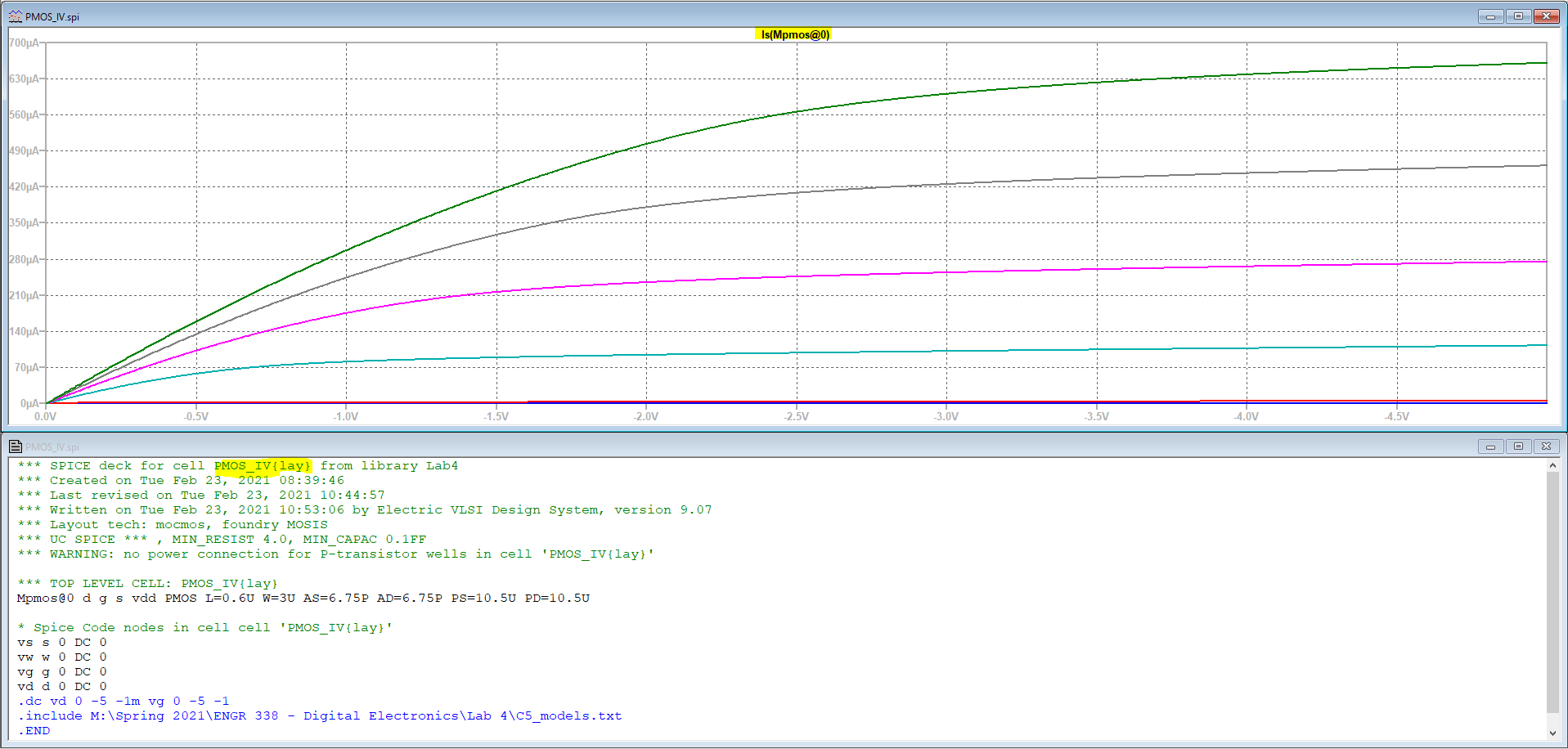

Next were the LTSpice waveforms

generated by both of these designs. These two waveforms can be seen in

Figures 7 and 8. It can be noted that both of these are smaller than

the NMOS waveforms; the scale of the NMOS waveforms are 0A - 1.2mA while PMOS waveforms are defaulted to 0A - 700uA.

Figure 7. PMOS_IV{sch} LTSpice waveform results from "Is" probed

Figure 8. PMOS_IV{lay} LTSpice waveform results from "Is" probed

Figure 7. PMOS_IV{sch} LTSpice waveform results from "Is" probed

Figure 8. PMOS_IV{lay} LTSpice waveform results from "Is" probed