ENGR338

2021 Spring

Lab 4: MOSFETs and IV Curves

Sophie Turner

sjturner@fortlewis.edu

MOSFETs and IV Curves

1. Introduction

The purpose of this lab was to create MOSFETs in ElectriVLSI and use LTSpice to run the simulations to analysis the IV curves.

2. Methods

ElectriVLSI software

was used to create the schematics and layouts of the MOSFETs. LTSpice

software was used to simulate the IV curves generated by the MOSFETs.

C5_models.txt was used to simulate the NMOS and PMOS nodes. For a

detailed methods go to http://www.yilectronics.com/Courses/ENGR338L_CE/lab4_MOSFETs/Lab4.html

3. Results

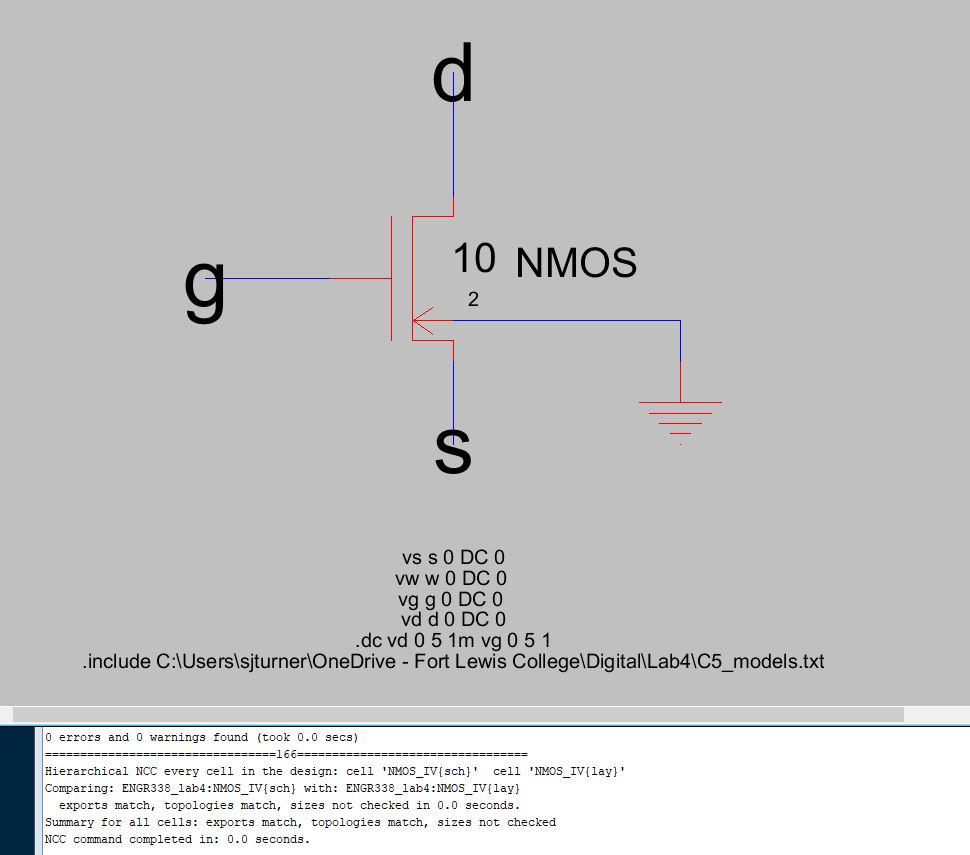

NMOS schematic was created using a NMOS node and converting it to a 4 port device.

Figure 1. NMOS schematic.

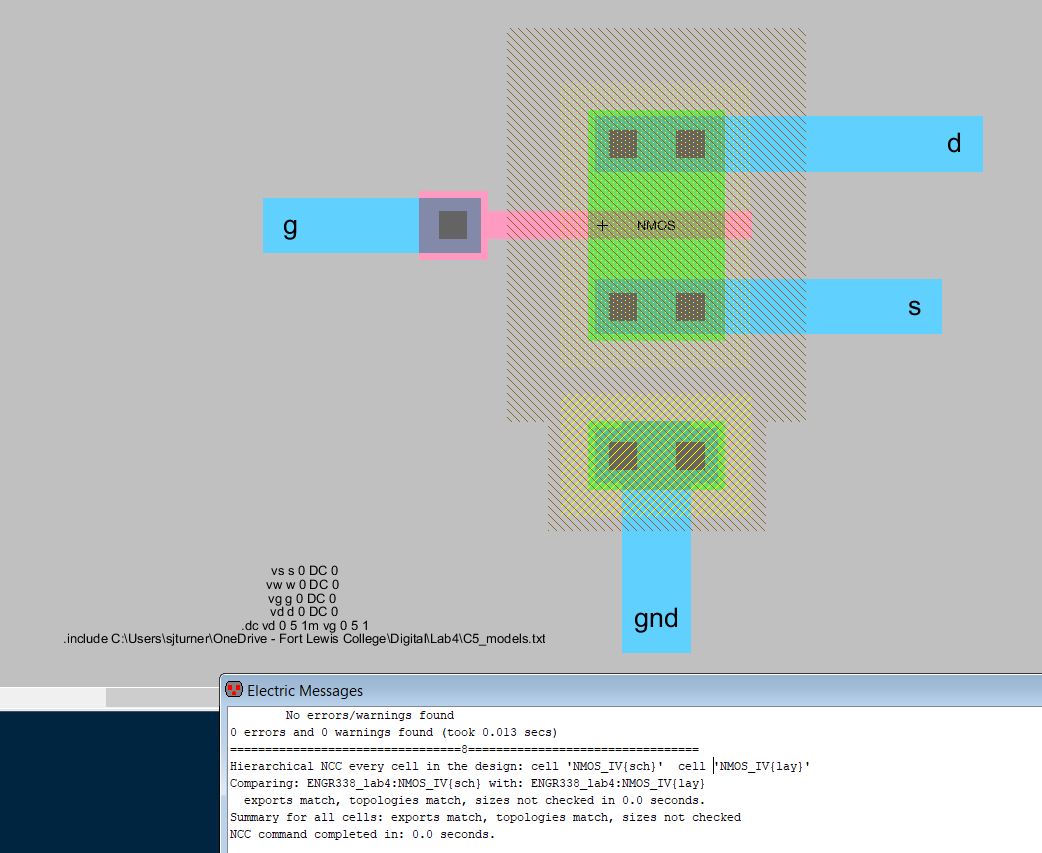

The NMOS layout was created with nMos node, two nAct nodes, metal-poly

contact, and a p-well. The components had a width of 10 excluding

the metal-ploy contact. The nodes were connected using arcs, then connected to gnd and to the correct terminals. DRC and NCC checks were run throughout the process of making this device.

Figure 2. NMOS layout

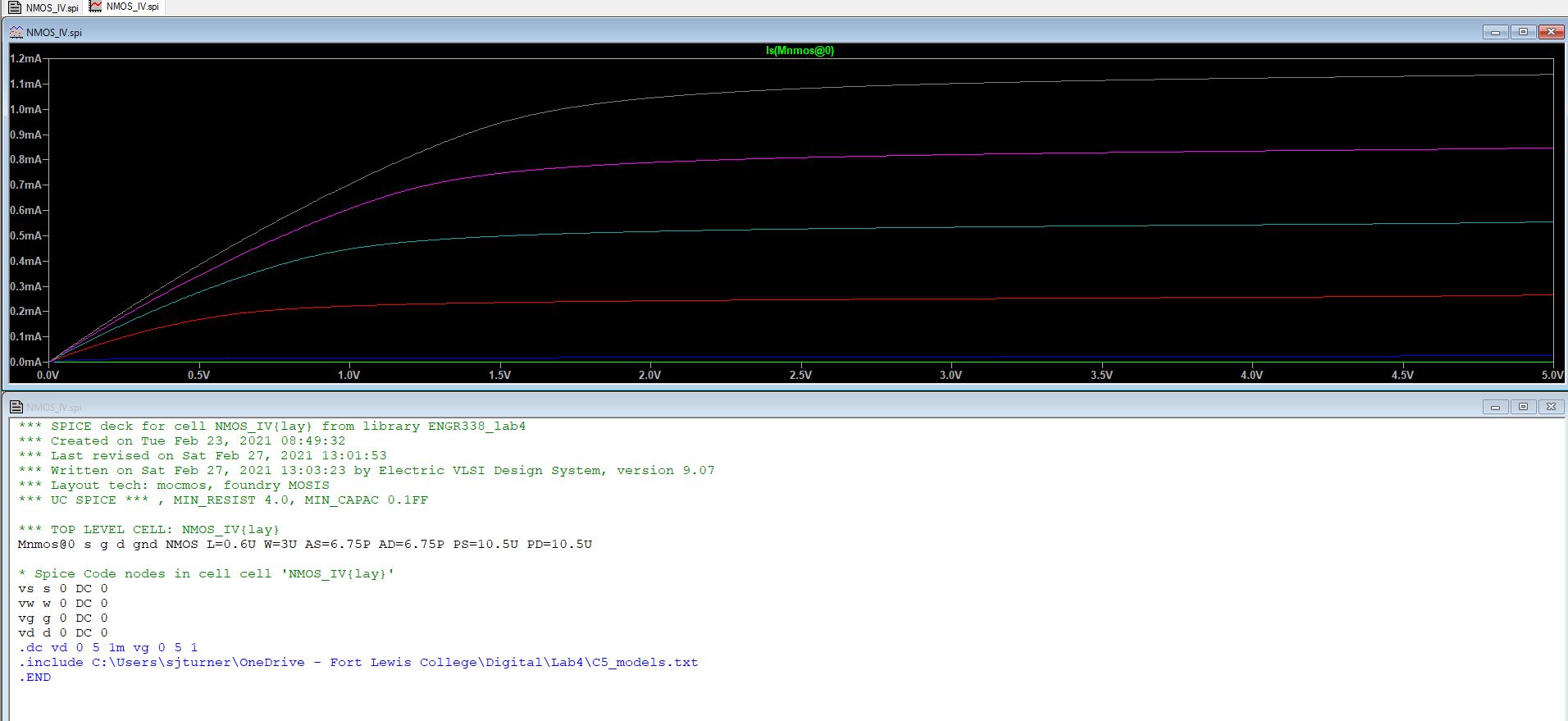

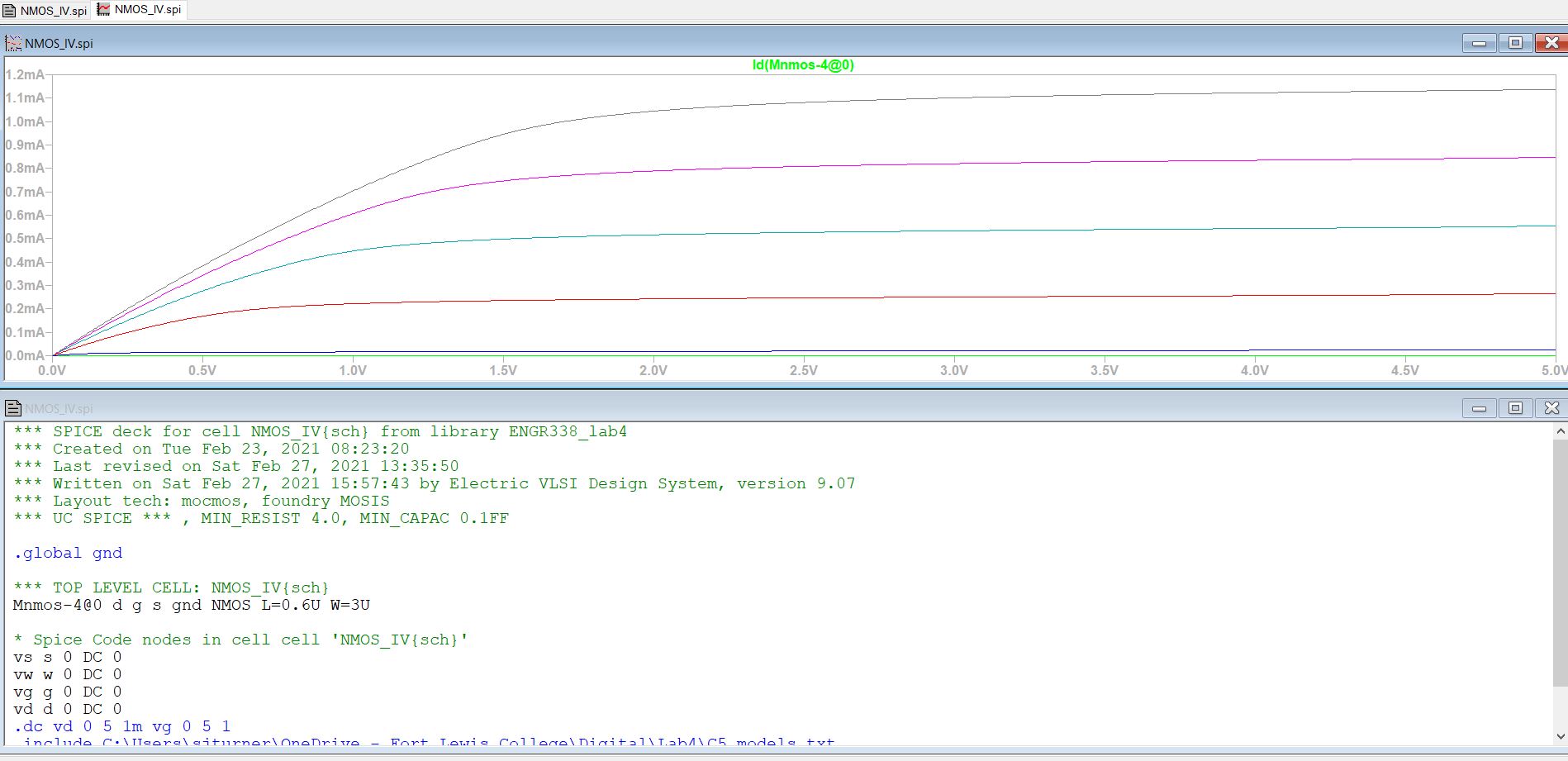

LTSpice was used to simulate the NMOS layout and schematic as shown in Figures 3 and 4.

Figure 3. LTSpice simulation of NMOS layout.

Figure 4. LTSpice simulation of NMOS schematic.

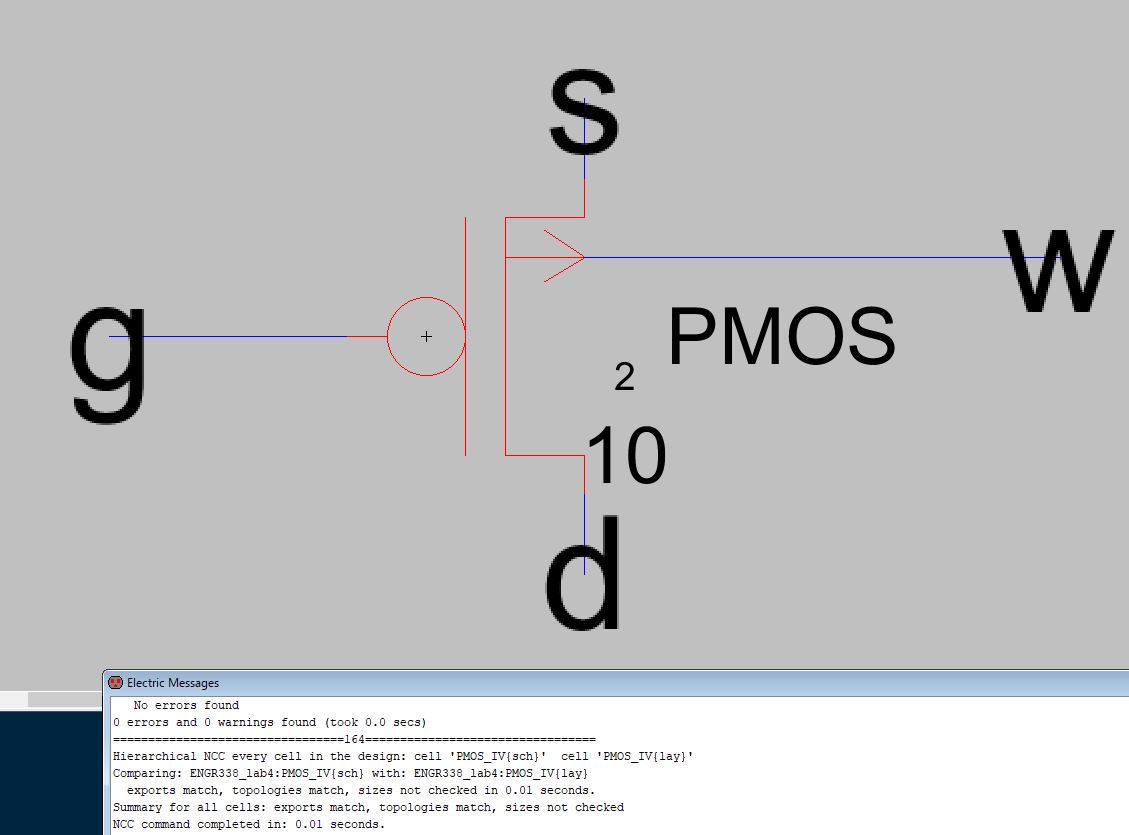

PMOS schematic was created using a PMOS node and converting it to a 4 port device.

Figure 5. PMOS schematic

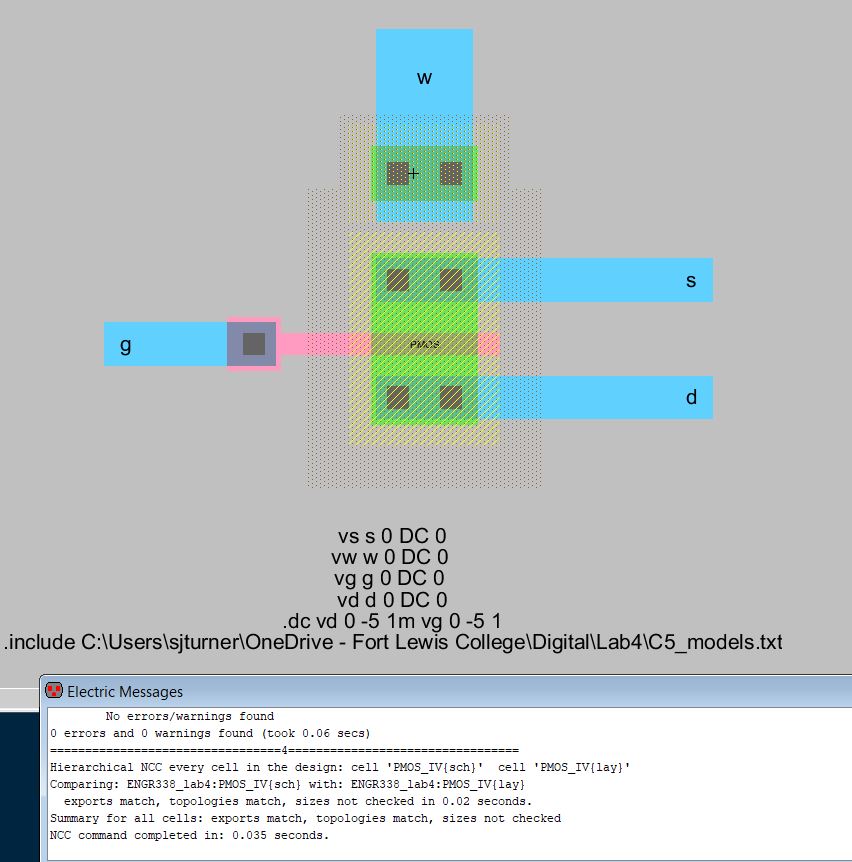

The PMOS layout was created with pMos node, two pAct nodes, metal-poly contact, and a n-well. The nodes were

connected using arcs then connected to

terminals. The components had a width of 10 excluding the metal-poly contact. DRC and NCC checks were run throughout the process of

making this device.

Figure 6. PMOS layout

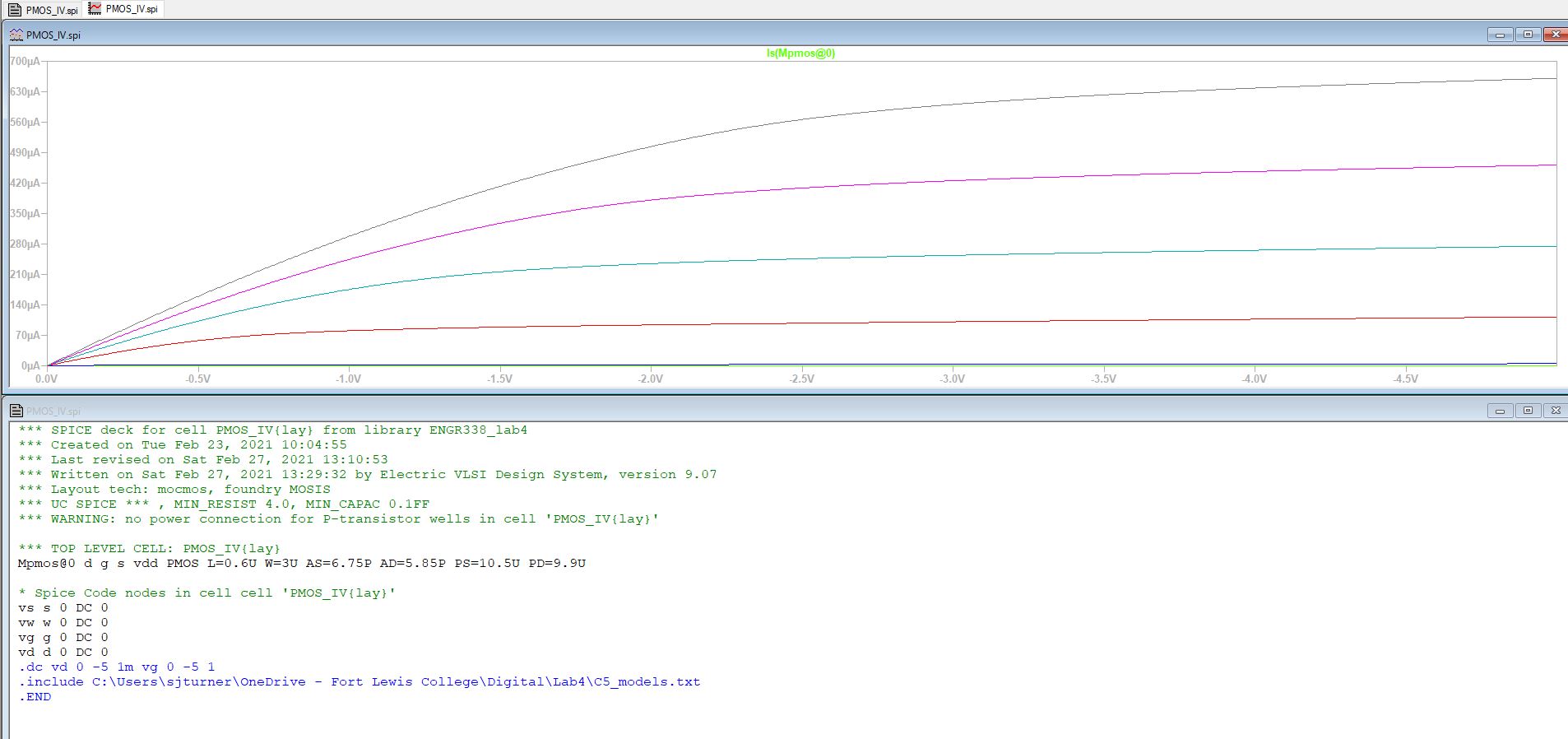

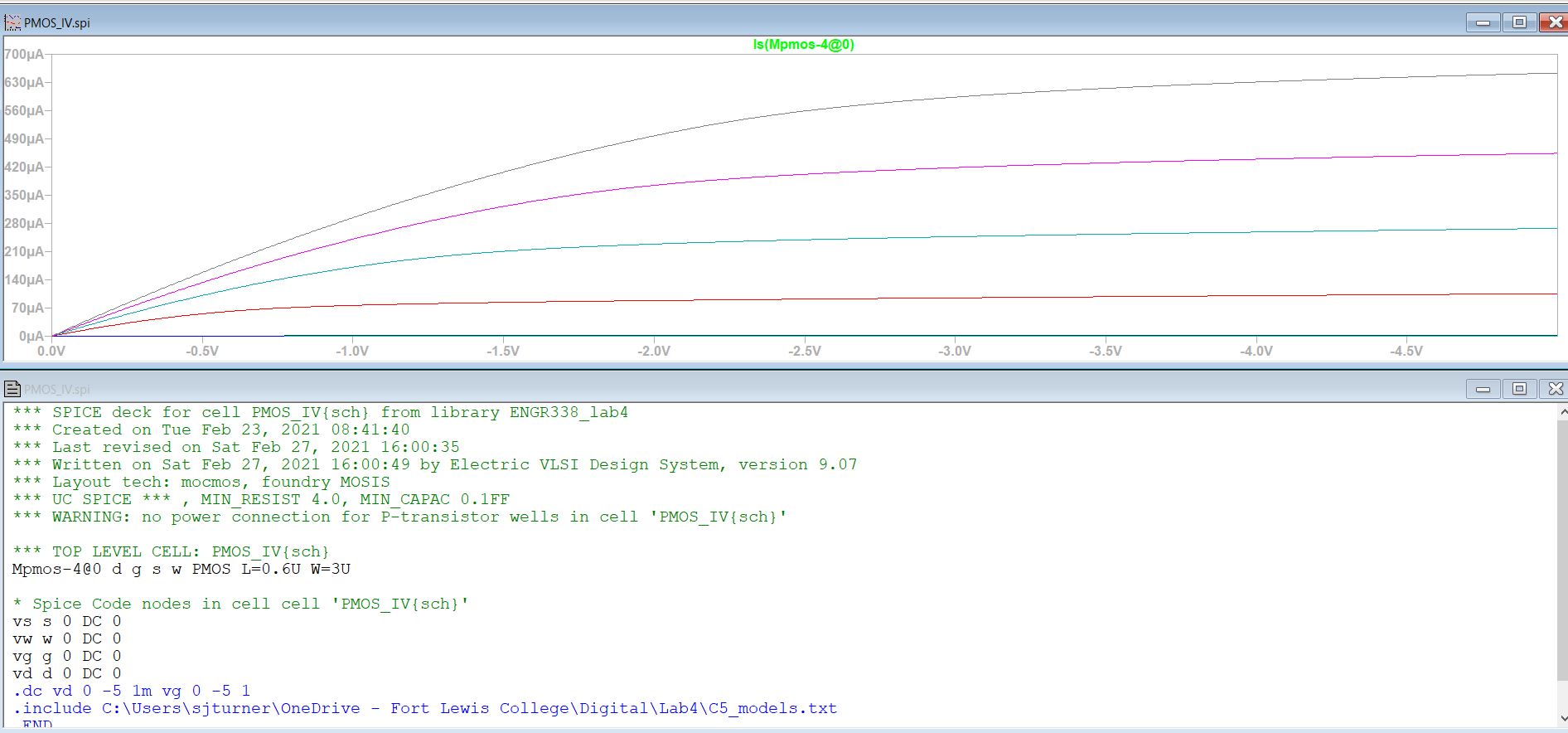

LTSpice was used to simulate the PMOS layout and schematic as shown in Figures 7 and 8.

Figure 7. LTSpice simulation of PMOS layout.

Figure 8. LTSpice schematic of NMOS layout.

2. Discussion

This

lab allowed me to gain more experience building devices on ElectriVLSI.

The schematic simulation and layout simulations for the MOSFETs

were verified and looked as expected. I learned more about PMOS and

NMOS transistors during this lab.