ENGR338

2021 Spring

Lab 3: Layout the R-2R DAC

Sophie Turner

sjturner@fortlewis.edu

Layout the R-2R DAC

1. Introduction

The purpose of this lab is to use ElectriVLSI

to create a R-2R DAC layout using N-Well resistors. LTSpice was used to

verify the DAC.

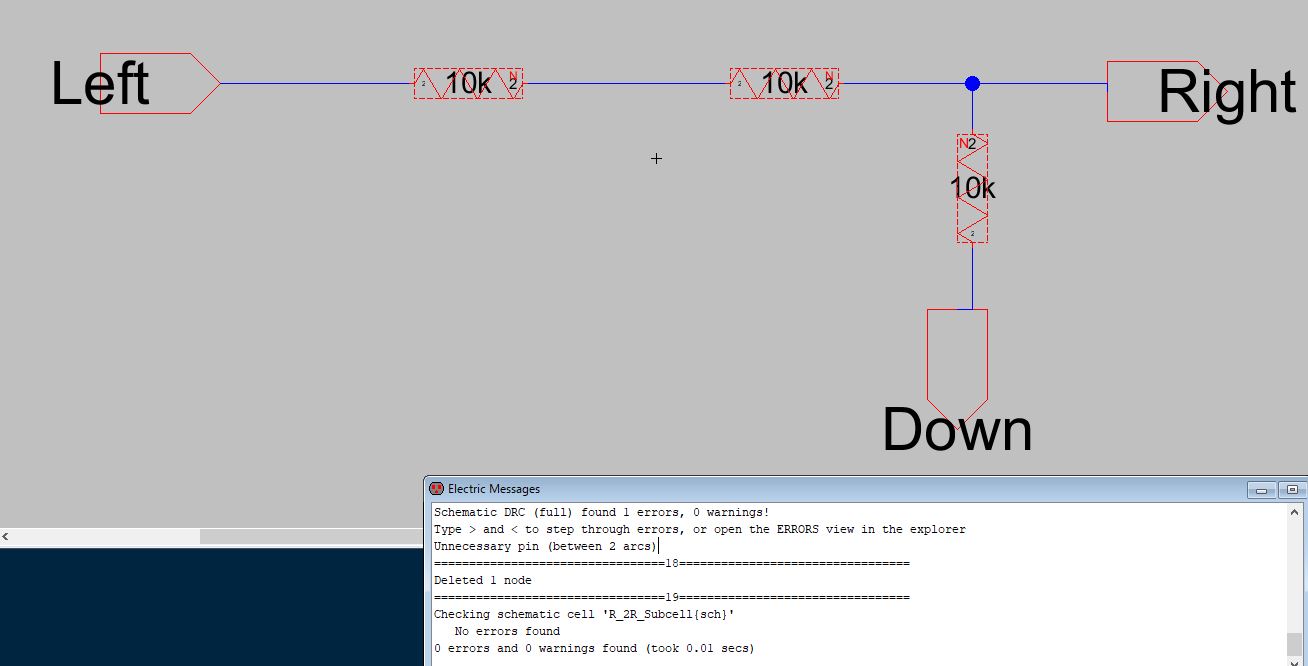

Task 1:

Task 1 was to create a schematic of the subcells

for a R-2R ladder. A subcell was created to make debugging a large design easier.

A subcell with a portion of the R-2R ladder was created and DCR checked for

errors.

Figure 1. Schematic of the subcell.

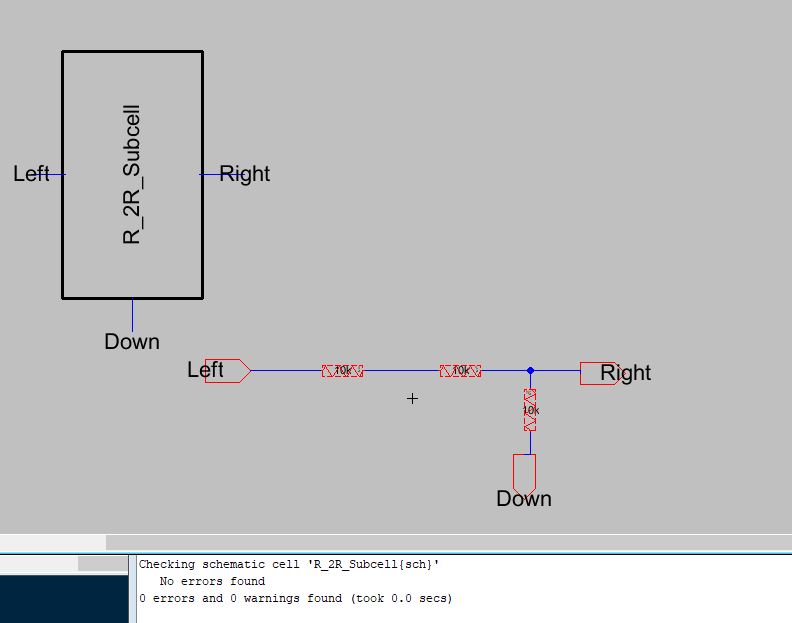

An icon was created and edited to follow the tutorial.

Figure 2. Subcell's schematic and icon.

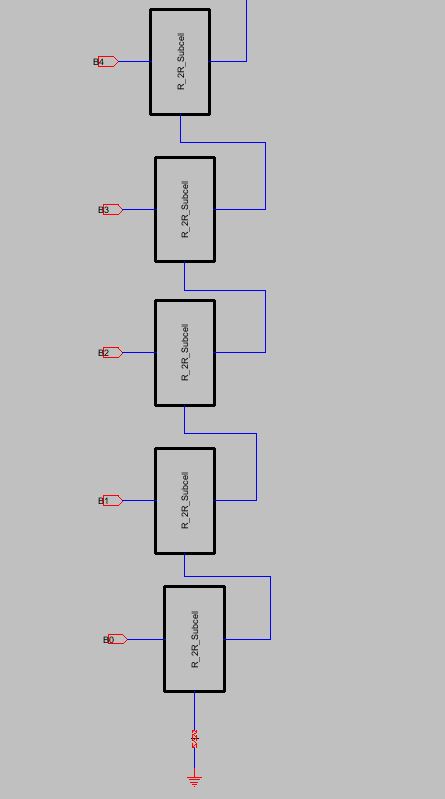

A schematic was

created and called 'R_2R_Ladder_v2' and the subcell icon was copied and

pasted 10 times. The 10 subcells were connected to a 10k resistor and

ground.

Figure 3. Icon and of the R-2R ladder and the schematic of 10 subcells connected.

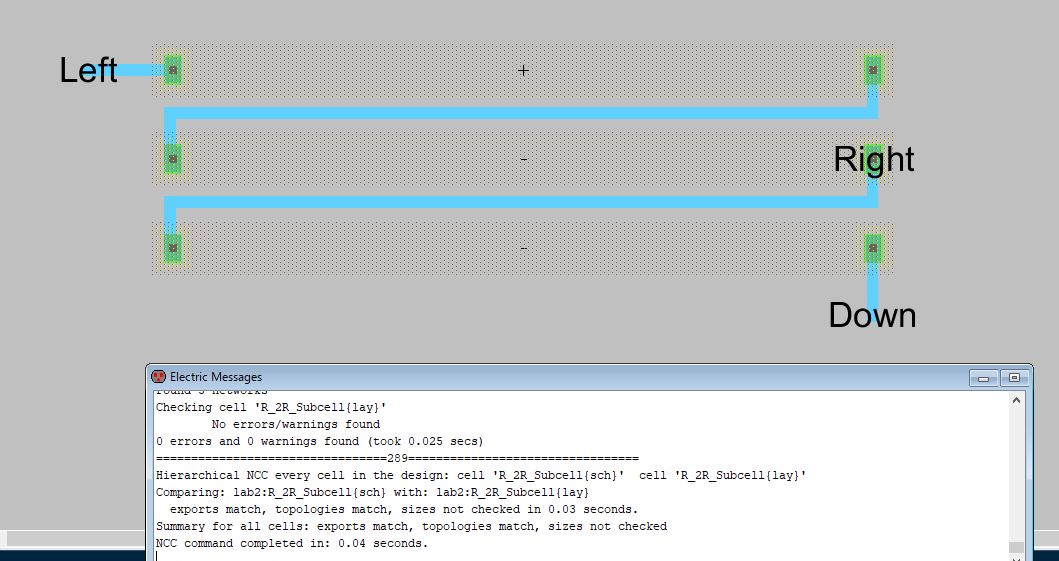

Task 2:

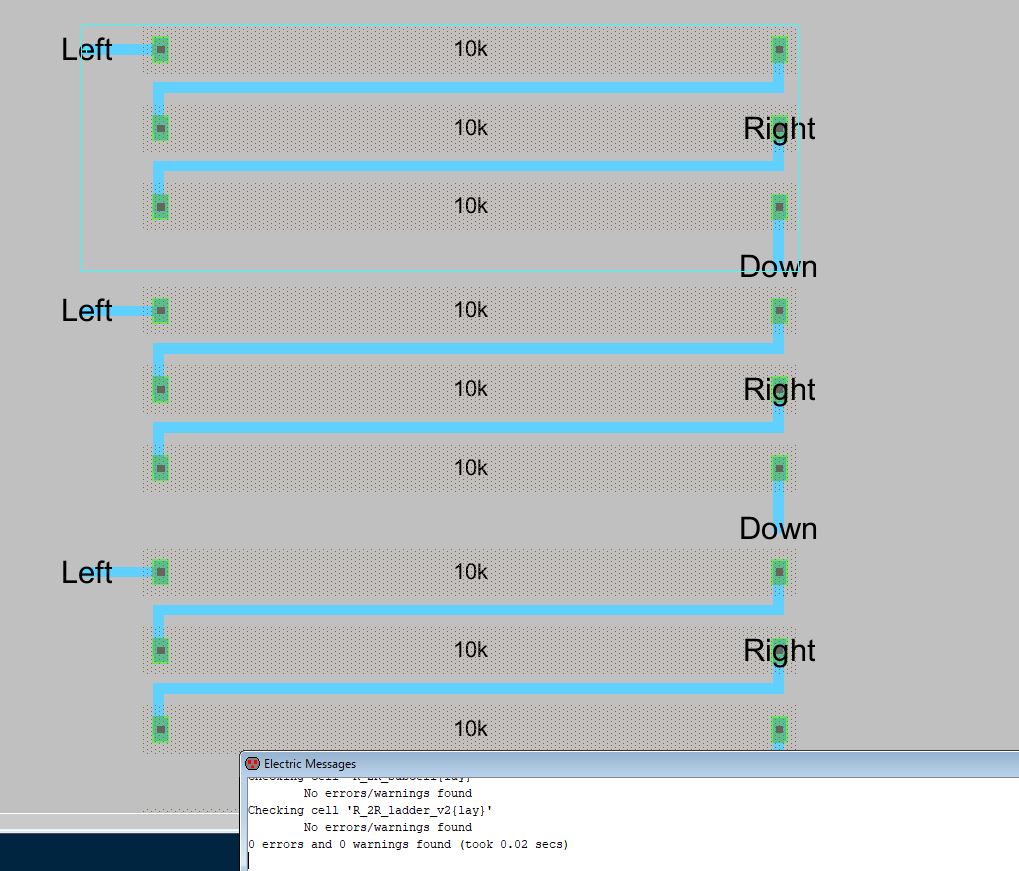

Task 2 asked to create a layout of the subcells for the R-2R

ladder. A layout was created for the R-2R ladder. Three 10k n-well

resistors were added using a width of 15 and length of 187.5 with 25

Lambda spacing between each resistor.

Figure 4. Layout view of the R_2R_ subcell using three 10k n-well resistors.

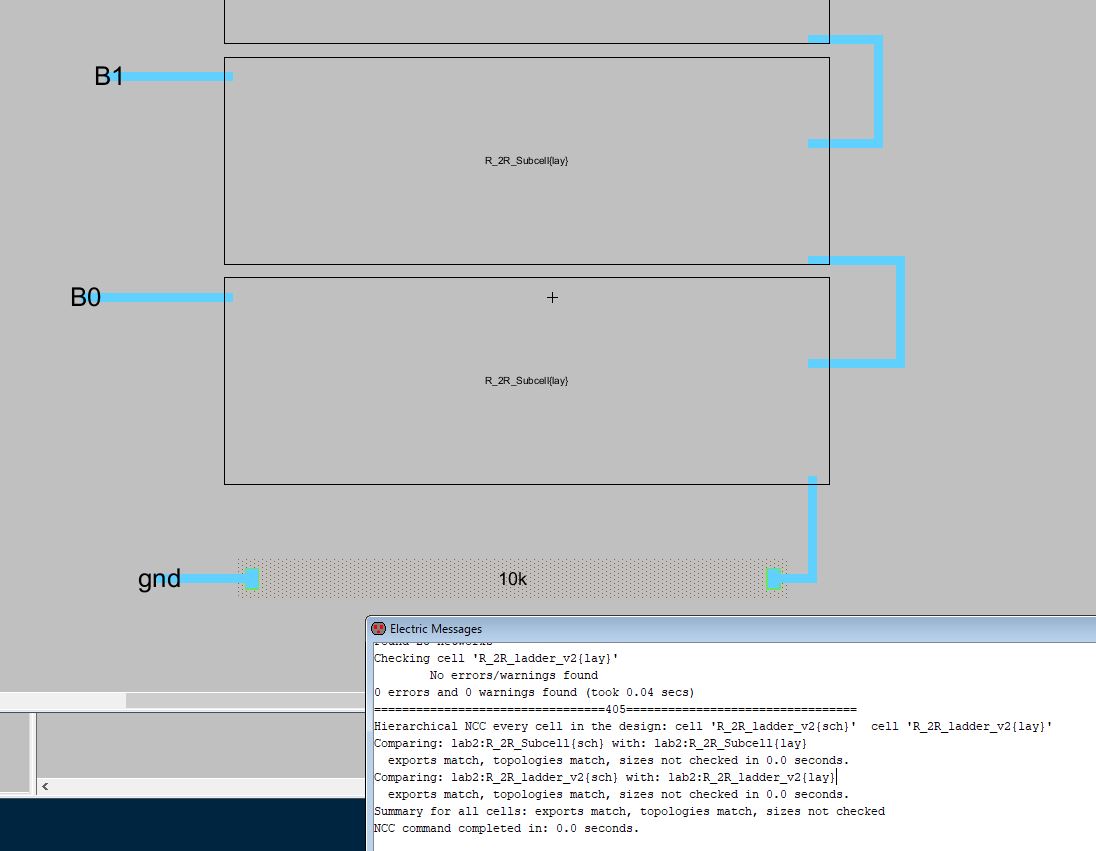

A schematic was created for the 'R_2R_Ladder_v2'

layout view. Ten of the subcells in Figure 4 were copied and pasted with 78

Lambda spacing. A 10k resistor and ground was added to end of the schematic. A

DRC and NCC check were run to ensure there were no errors.

Figure 5. 10-cells creating R_2R ladder using R_2R subcells.

Figure 6. Connecting the 10 subcells to a 10k resistor and ground and running DRC and NCC checks.

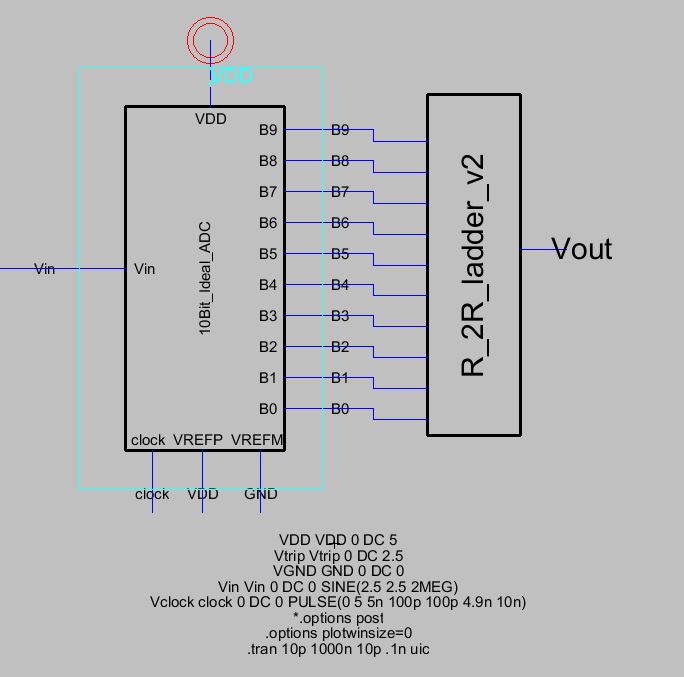

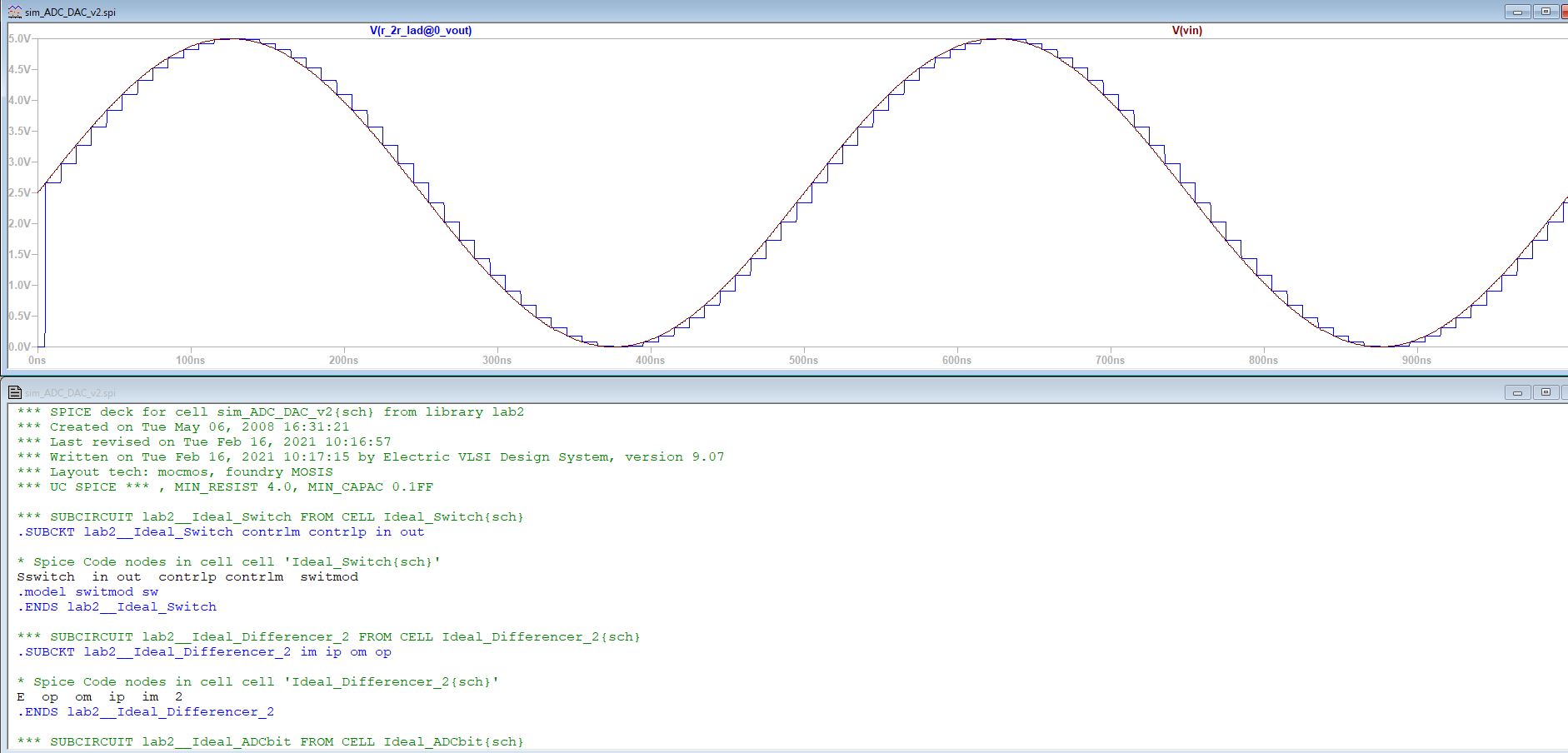

The DAC that was created for lab2 was replaced with the new

R_2R_ladder_v2 icon. The R_2R_ladder_v2 was connected to the ideal

10-bit ideal ADC as seen in the figure below. This schematic was

simulated in LTSpice and the waveform was as expected. The simulation

was similar to when the ADC was connected to the DAC.

Figure 7. Connecting 10-bit ideal ADC to the new R_2R_ladder_v2 icon.

Figure 8. Simulation and code in LTSpice for the ideal ADC with the R_2R ladder.

2. Discussion

This

lab allowed me to become for familiar with ElectriVLSI. This lab showed the

importance of subcells and how useful they are. I gained more experience in

creating a R_2R ladder a different way by using subcells.