ENGR338 Spring 2021

Course Project

Scott Orban

SJOrban@fortlewis.edu

Introduction

The purpose of this project was to build and simulate an 8-bit SAR ADC.

Materials and Methods

LTspice was used to create and simulate the curcuit.

Results

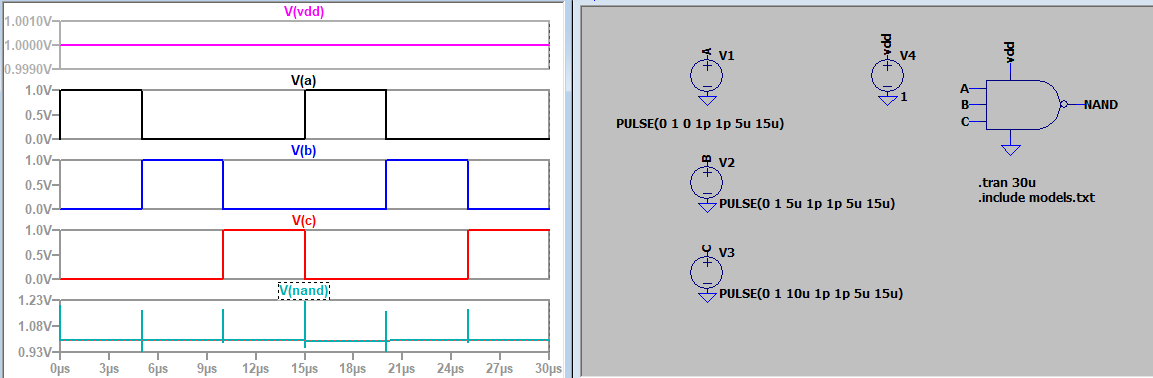

Figure 1: Schematic of the 3-input

NAND gate used in the DFF.

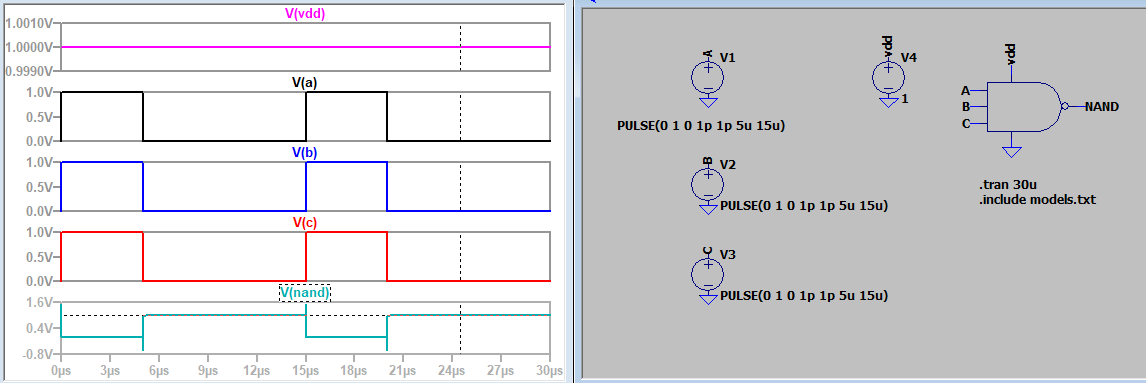

Figure 2: Simulation of the NAND gate showing when any of the inputs

are low the output is high.

Figure 3: Simulation of the NAND gate

showing when all of

the inputs are high the output is low.

Discussion

The simulation results matched the expected behavior of each circuit.