ENGR338 Lab Spring 2021

Lab 4: MOSFETs and IV Curves

Scott Orban

SJOrban@fortlewis.edu

Introduction

The purpose of this lab was to learn how to build MOSFETs in Electric

VLSI, run simulations, and view and analyse their IV curves.

Materials and Methods

The transistors were built using Electric VLSI and simulated using

LTSpice.

Results

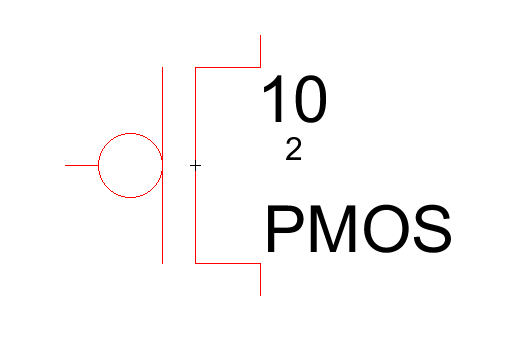

Figure 1: NMOS transistor

schematic with width 10.

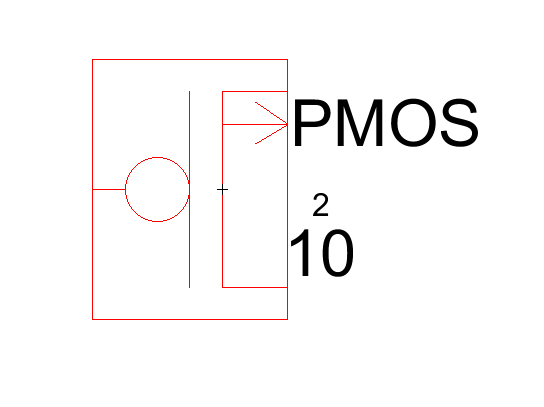

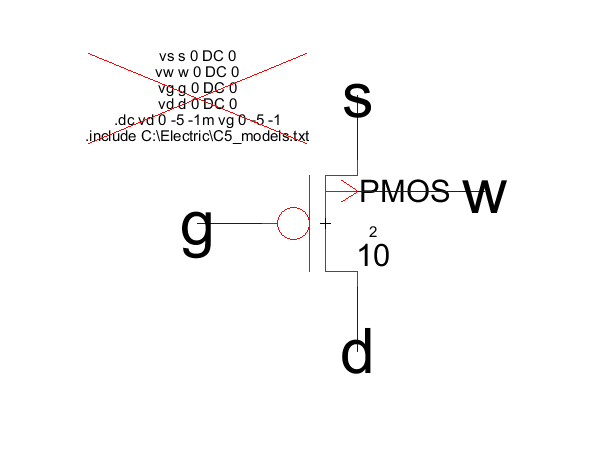

Figure 2: PMOS

transistor schematic with width 10.

Figure 3: 4 input PMOS

transistor schematic with width 10.

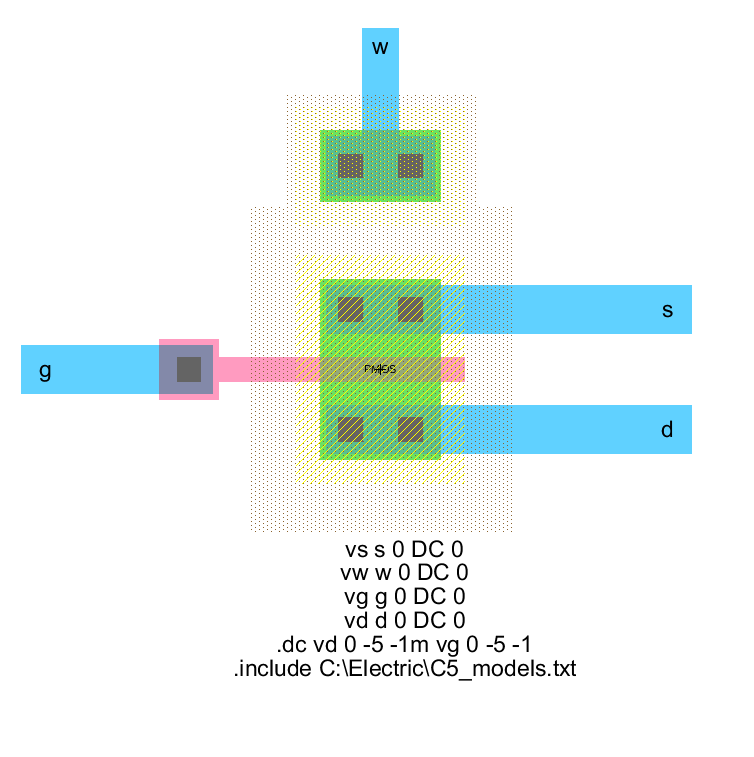

Figure 4: PMOS transistor

layout with spice code.

Figure 4: PMOS transistor

layout with spice code.

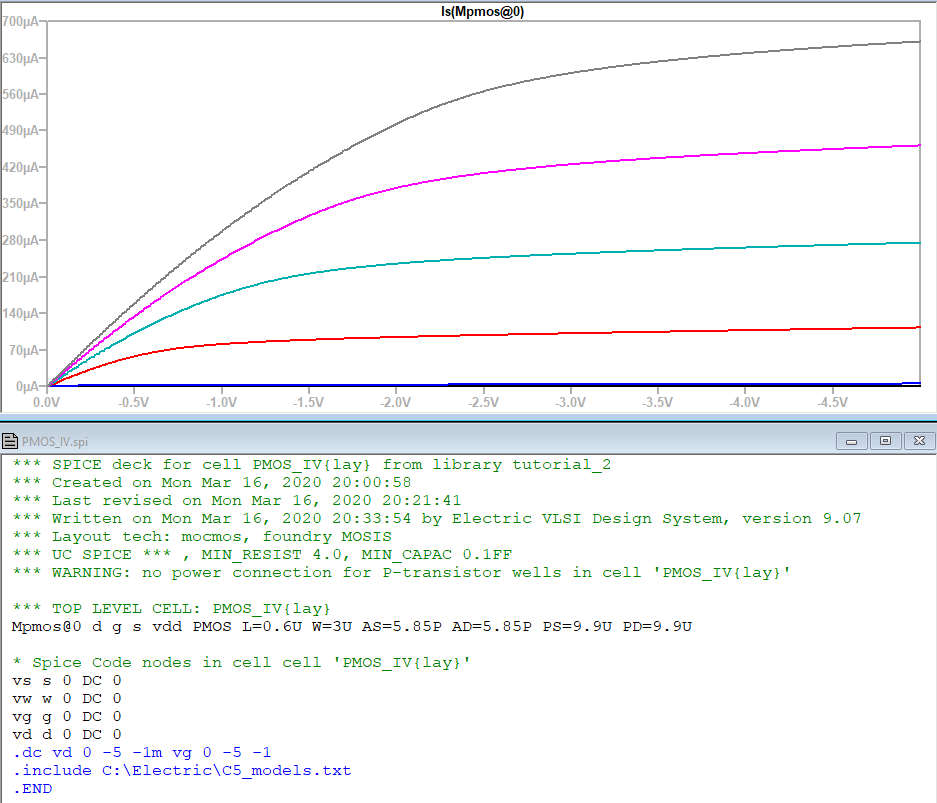

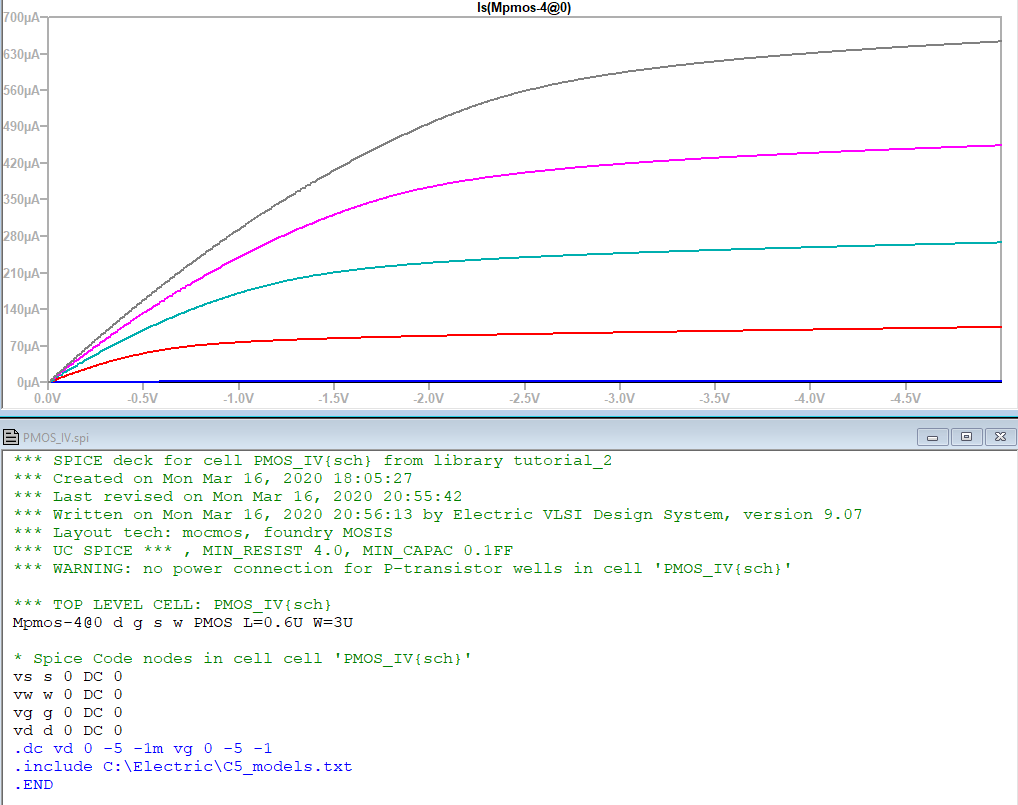

Figure 5: Spice simulation

results of the PMOS transistor.

Figure 5: Spice simulation

results of the PMOS transistor.

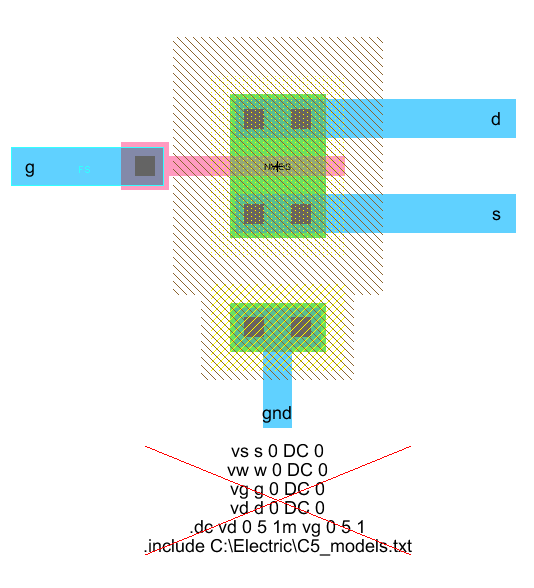

Figure 6: NMOS transistor

layout with spice code.

Figure 6: NMOS transistor

layout with spice code.

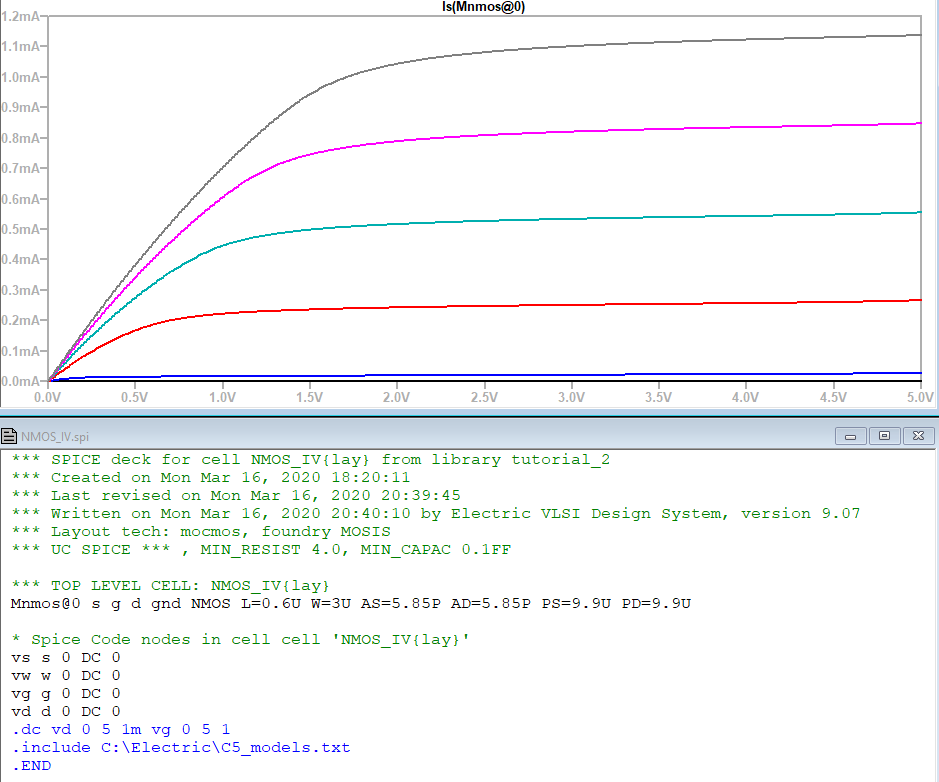

Figure 7: NMOS transistor

simulation results.

Figure 7: NMOS transistor

simulation results.

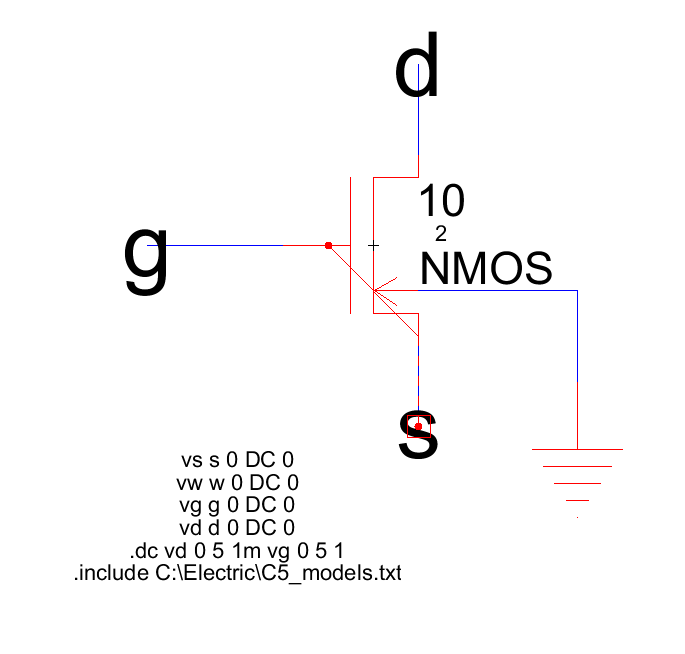

Figure 8: Completed NMOS

transistor schematic.

Figure 8: Completed NMOS

transistor schematic.

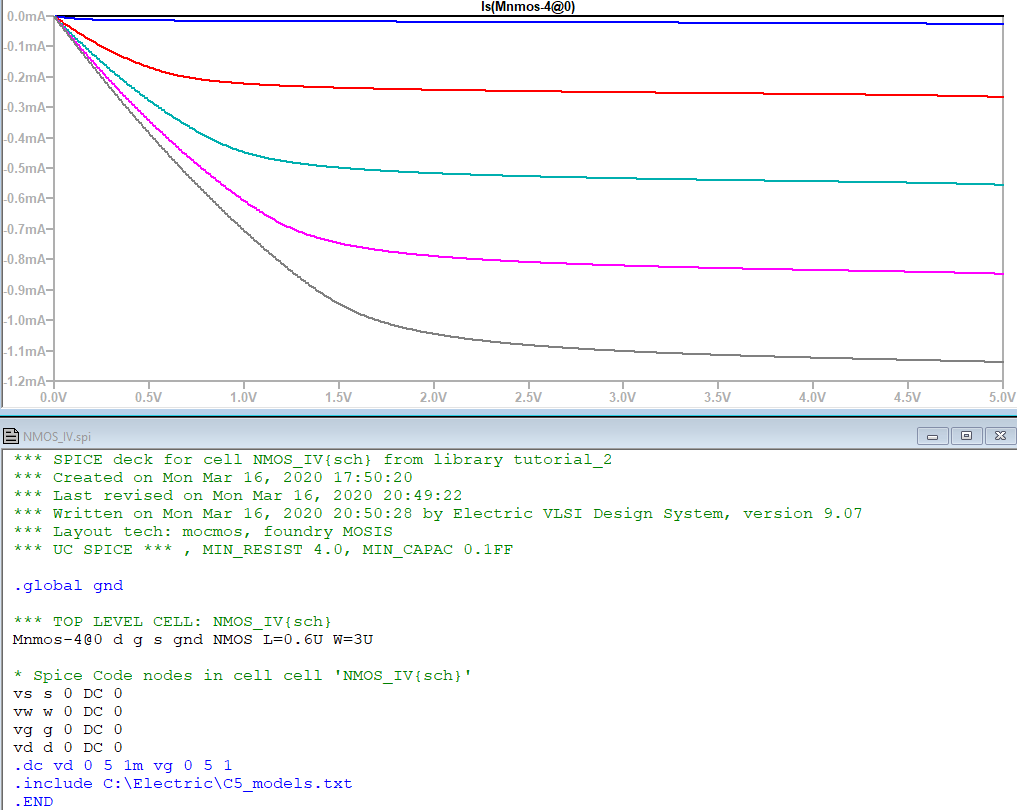

Figure 9: Completed NMOS

transistor schematic simulation results.

Figure 9: Completed NMOS

transistor schematic simulation results.

Figure 10: Completed PMOS transistor schematic.

Figure 10: Completed PMOS transistor schematic.

Figure 11: Completed PMOS transistor

schematic simulation results.

Figure 11: Completed PMOS transistor

schematic simulation results.

The schematics and layouts matched and were error free, and the

simulation values were as expected.