CE433 Embedded Devices Spring 2022

Lab 4 - Combinational Blocks

Name: Ryan Jeanes

Email: rejeanes@fortlewis.edu

Lab 4 - Combinational Blocks

Introduction

This lab was focused on combinational blocks logic in verilog.

Results

Task 1

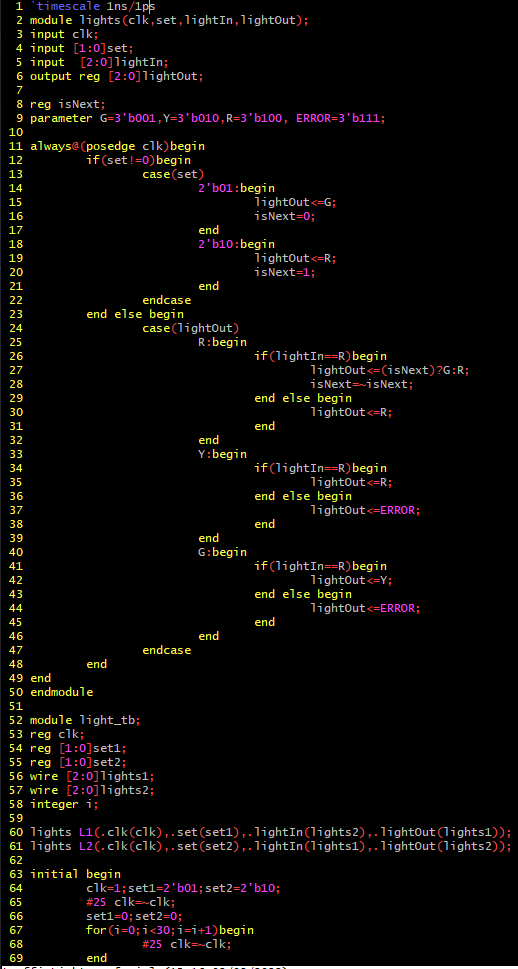

Since

I was already working on a state-based solution, I decided to keep with

that for the simulation and use the encoder method for uploading to the

FPGA board.

Figure 1 - Code used for the traffic light simulation

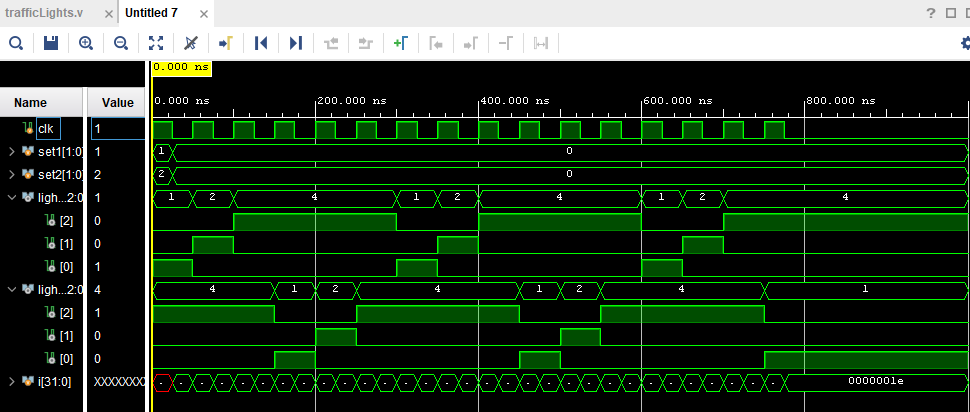

Figure 2 - Traffic light simulation showing no conflicting light configurations.

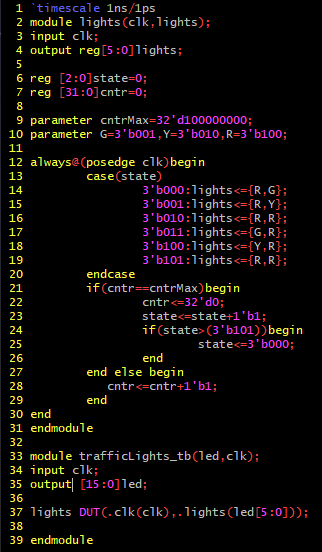

Figure 3 - Code used for the FPGA board.

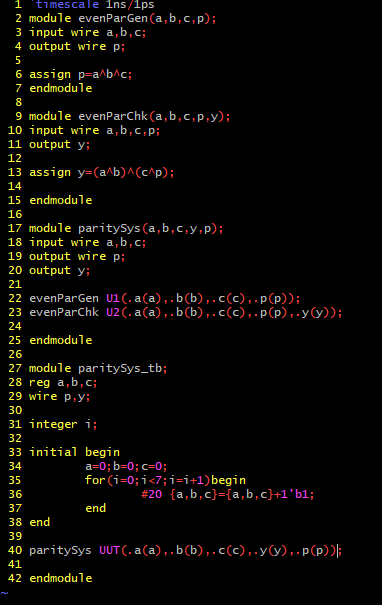

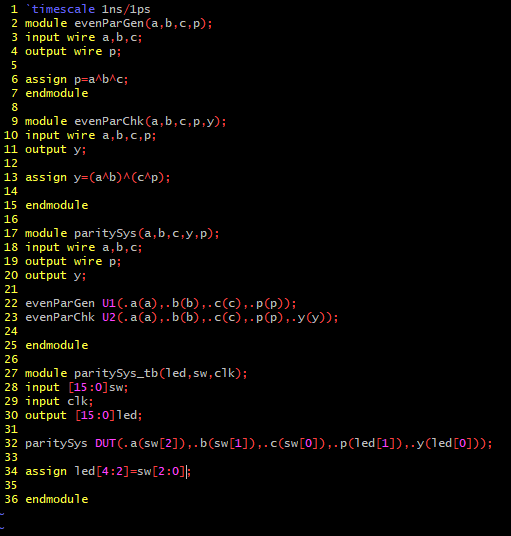

Figure 4 - Code for the even parity and checker

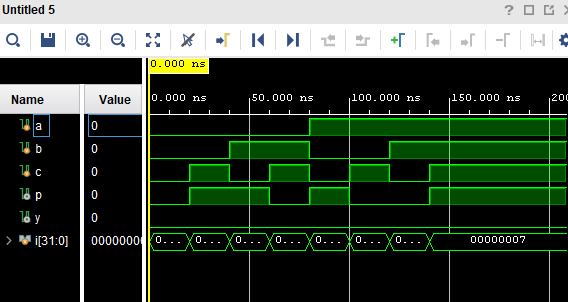

Figure

5 - Simulation of even parity checker and generator that shows the even

parity generator is functioning as intended as y is always 0.

Figure 6 - Code of even parity generator and checker uploaded to the FPGA board.