Figure 1 - Simulation of section 2.1 structural modeling example

Figure 2 - Vim window of section 2.1 structural modeling example.

Figure 3 - Simlation of section 2.2 dataflow modeling example

Figure 4 - Vim window of section 2.2 dataflow modeling example.

Figure 5 - Simulation of section 2.2 merged dataflow modeling example.

Figure 6 - Vim window of section 2.2 merged dataflow modeling example.

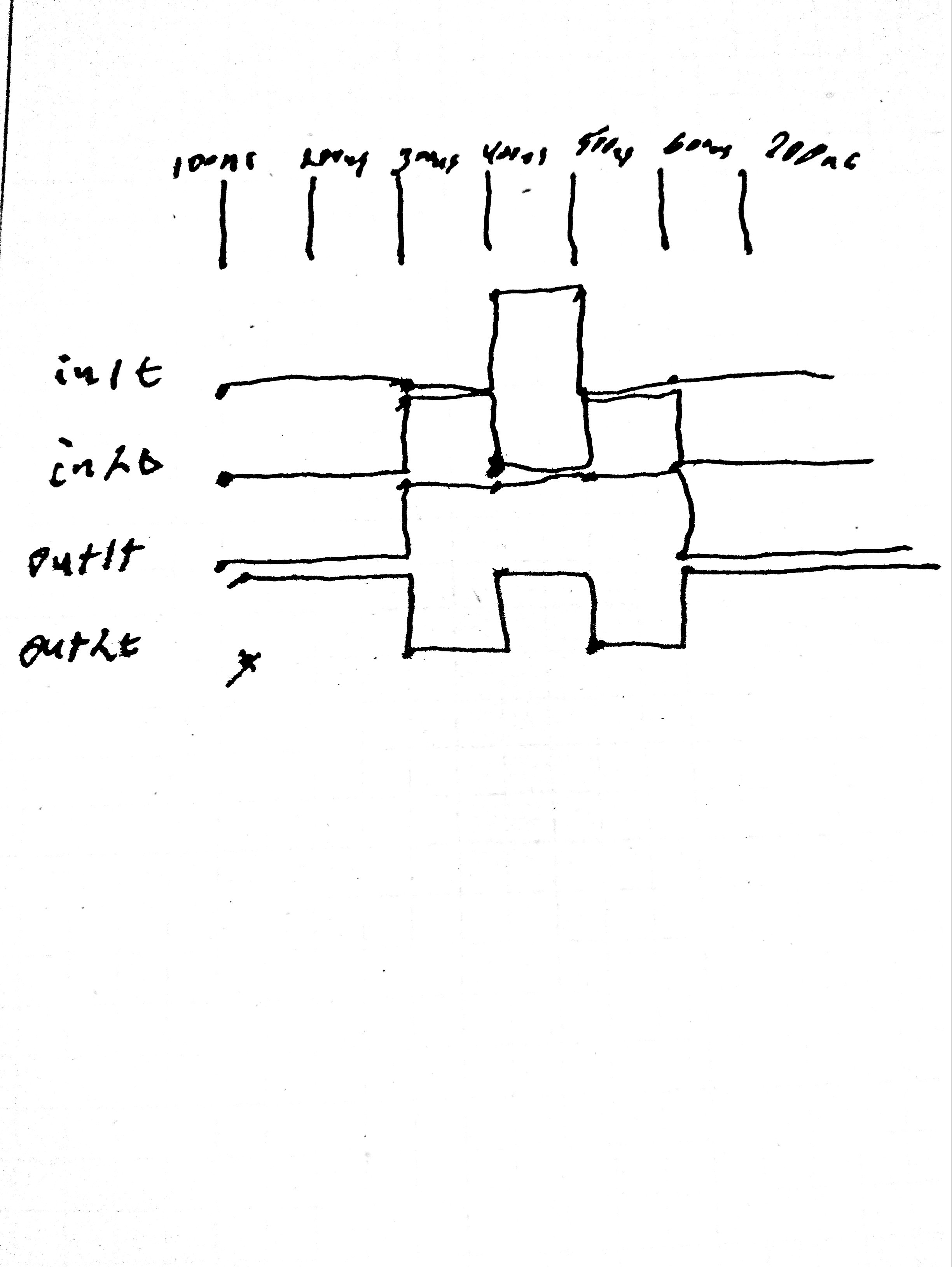

Figure 7 - Simulation of section 2.3 example

Figure 8 - Vim window of section 3.3 example.