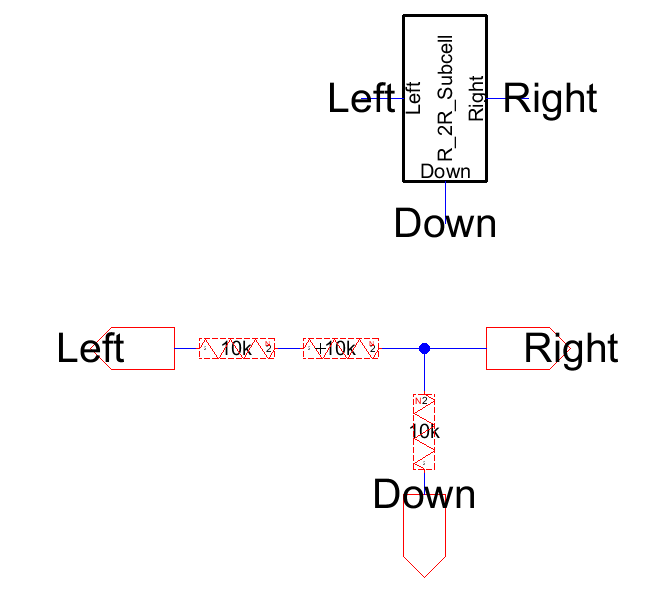

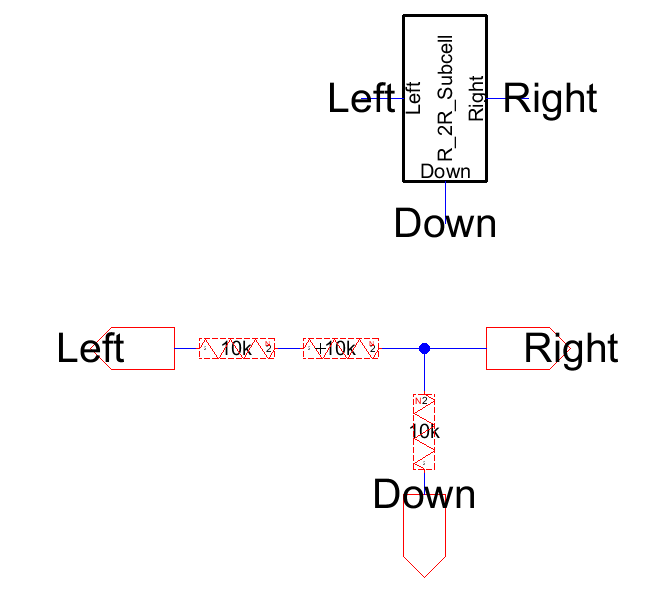

Figure 1: Schematic view of the R-2R sub cell.

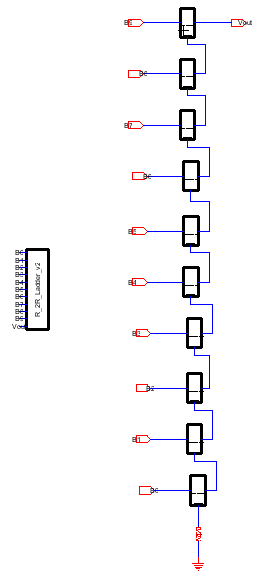

The resistor ladder was simplified into the following, using the R-2R sub cell.

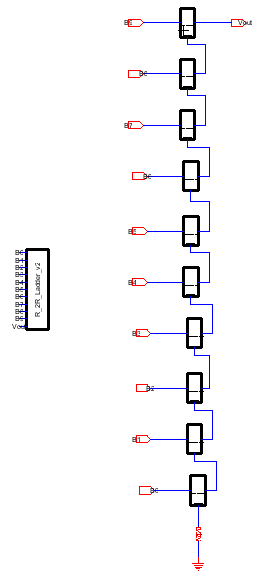

Figure 2: Schematic view of the R-2R ladder composed of the sub cells.

|

|

|

| Item |

Quantity |

|

|

|

| LTspice Electric VLSI Ideal ADC/DAC Library |

1 1 1 |

|

|

|