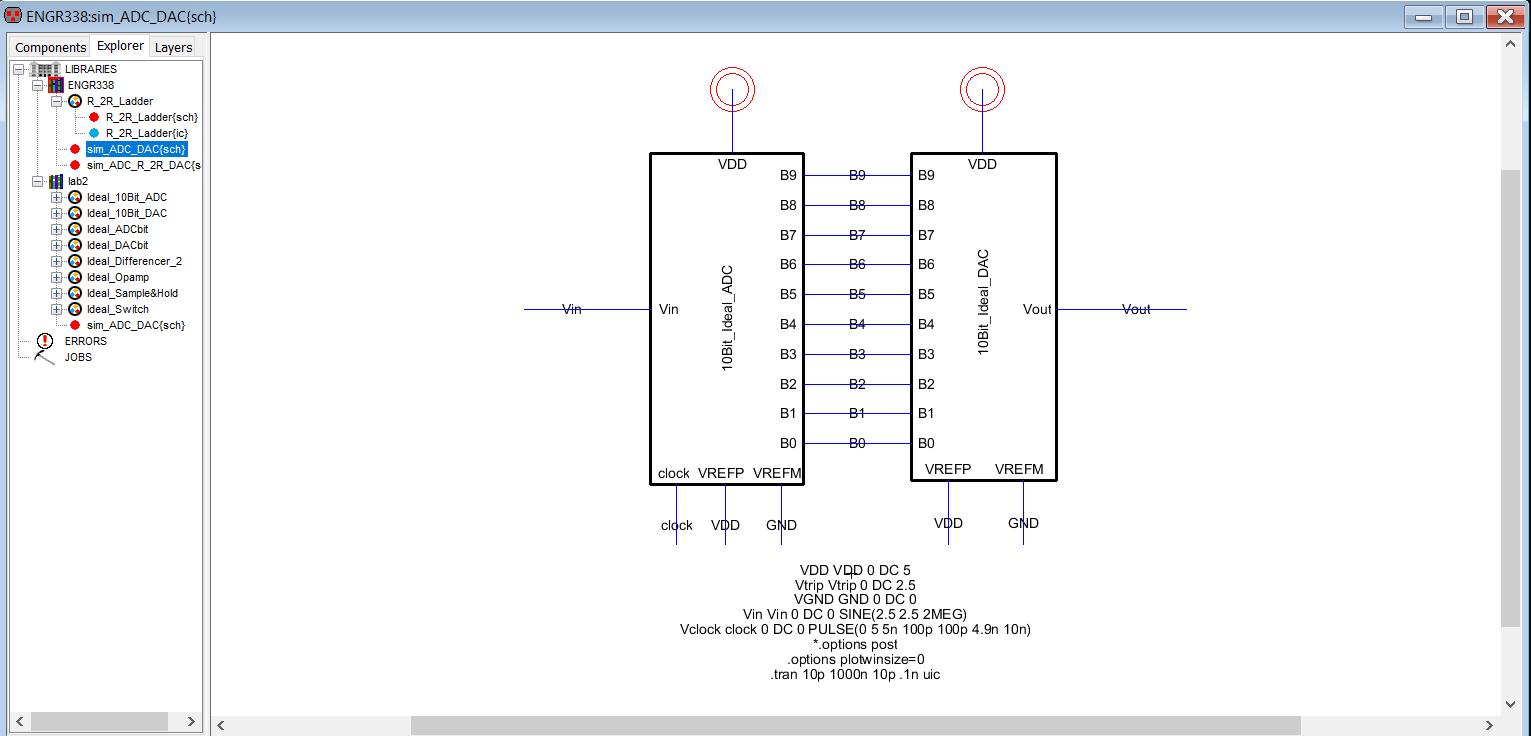

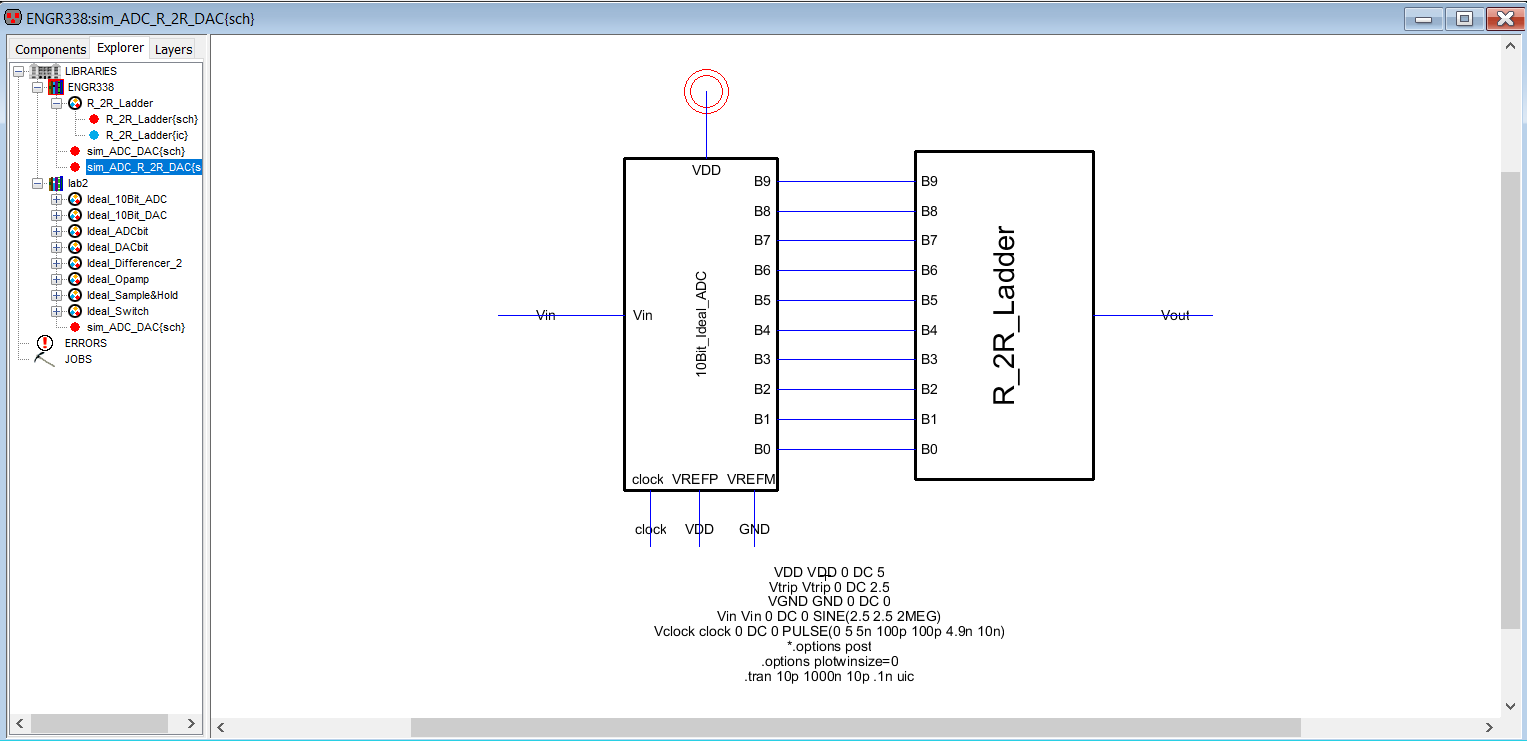

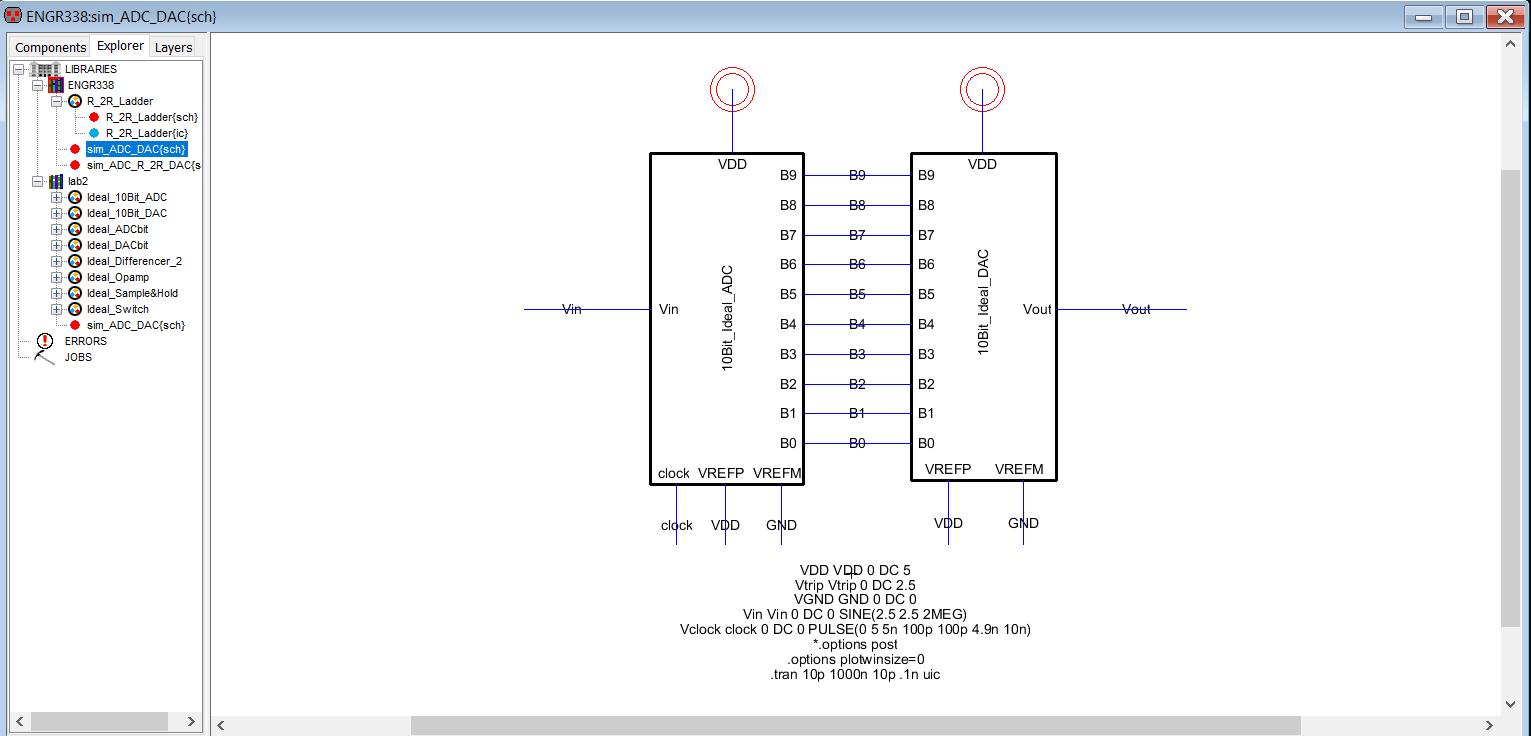

Figure 1: Schematic view of the ideal ADC/DAC.

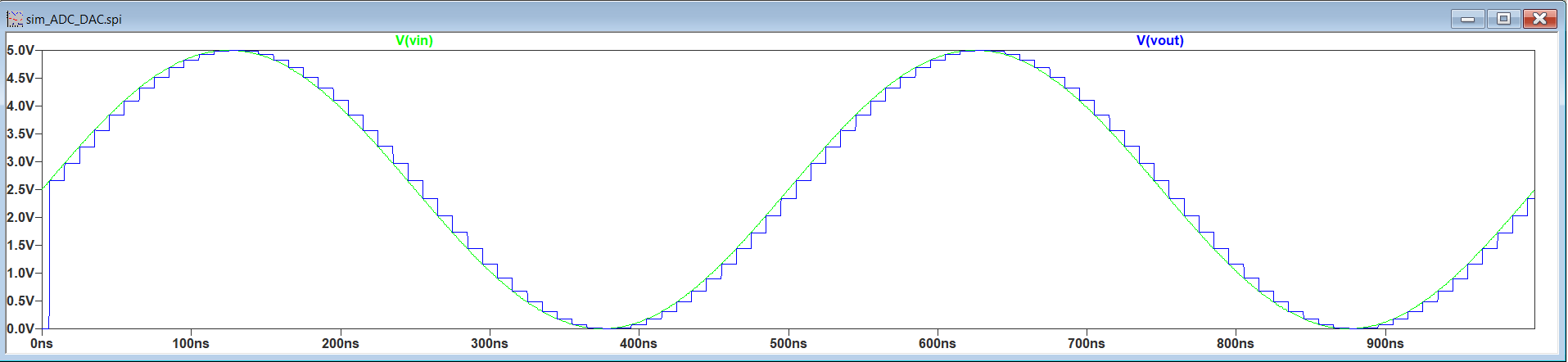

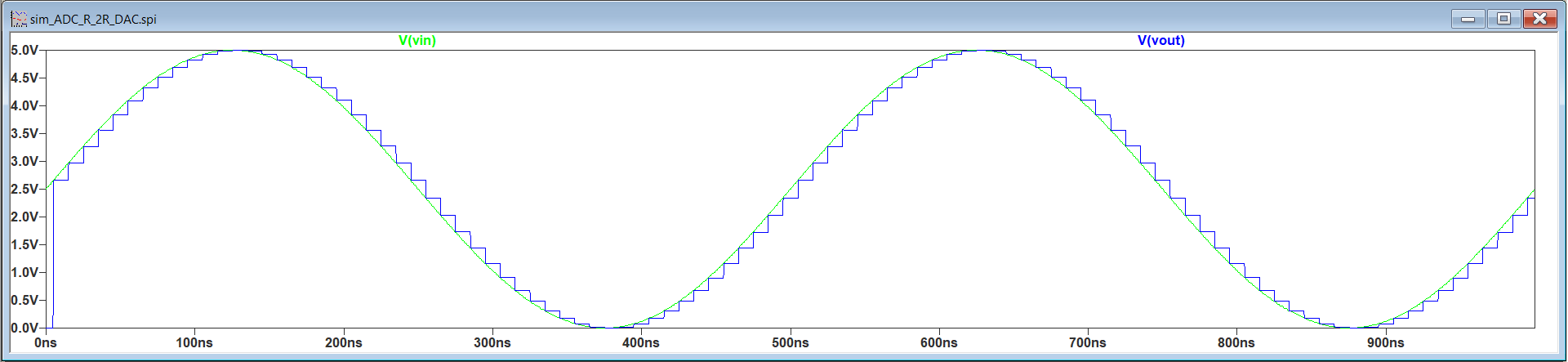

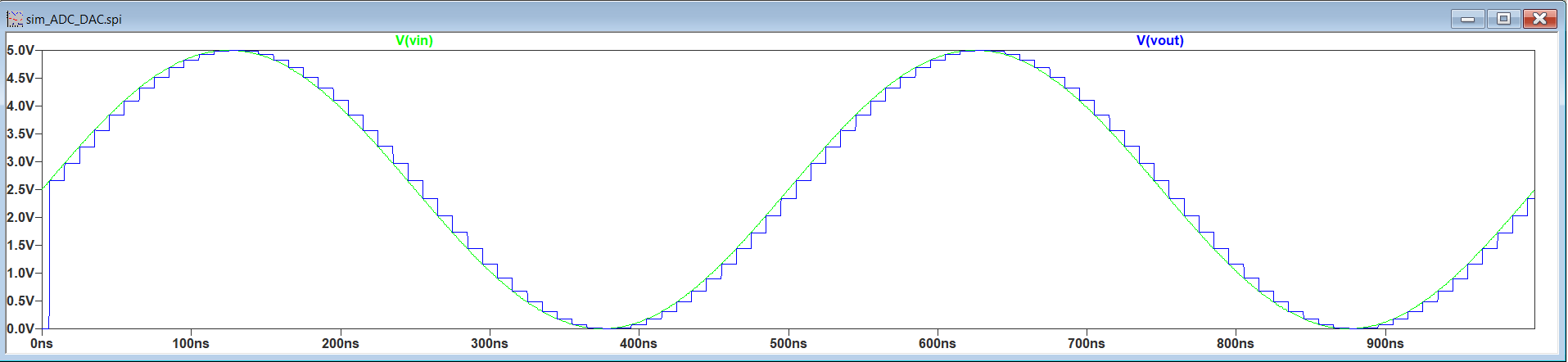

Figure 2 shows the simulation results from LTspice.

Figure 2: Simulation of ideal ADC/DAC.

|

|

|

| Item |

Quantity |

|

|

|

| LTspice Electric VLSI Ideal ADC/DAC Library |

1 1 1 |

|

|

|