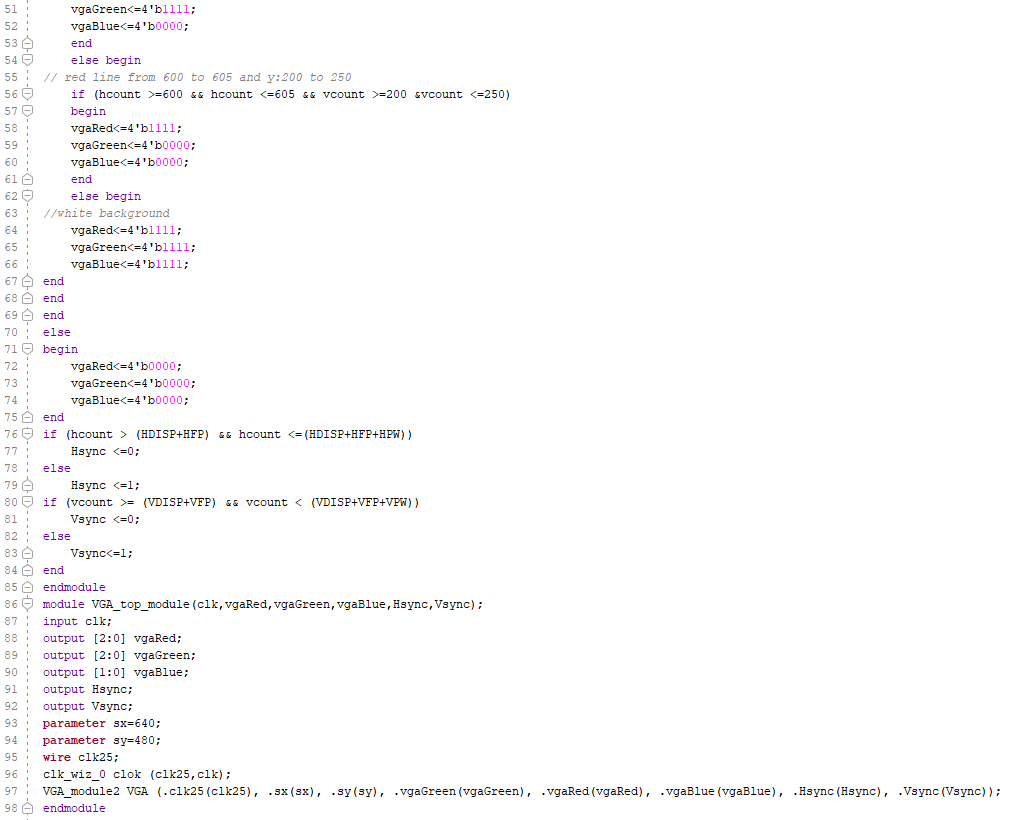

Task 1: In this task we created a white background as well as a green line of 4 pixels wide to be displayed by VGA from the BASYS 3 Board.

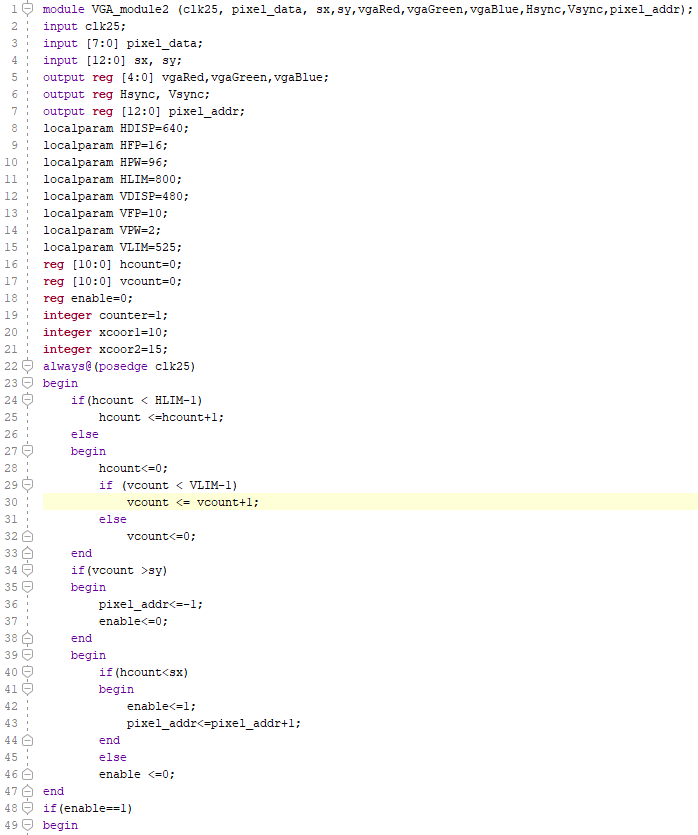

Task 2

Task 2: In this task we created a white background as well as a green line of 4 pixels wide and a smaller red line on the other side to be displayed by VGA from the BASYS 3 Board.

Task 2: In this task we created a white background as well as a green line of 4 pixels wide and a smaller red line on the other side to be displayed by VGA from the BASYS 3 Board.

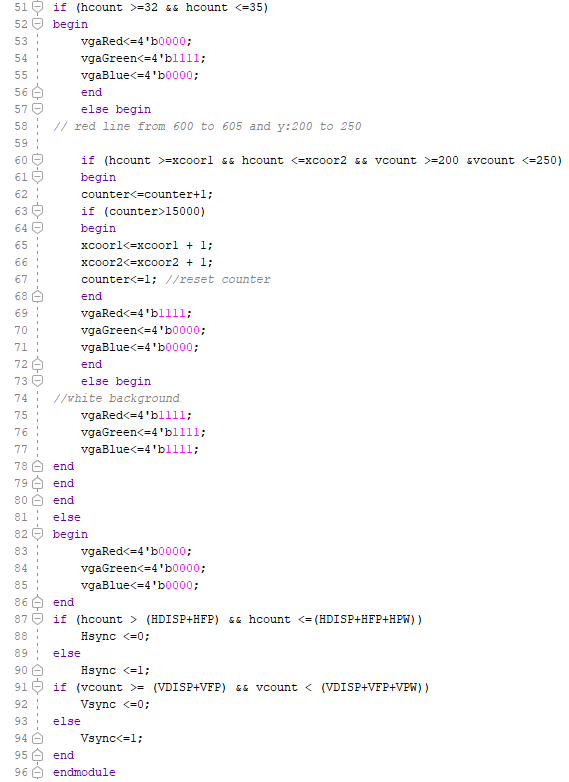

Task

3

Task 3: In this task we created a white background as well as a green line of 4 pixels wide and a smaller red line that moves one pixel to the right every second to be displayed by VGA from the BASYS 3 Board.

Task 3: In this task we created a white background as well as a green line of 4 pixels wide and a smaller red line that moves one pixel to the right every second to be displayed by VGA from the BASYS 3 Board.

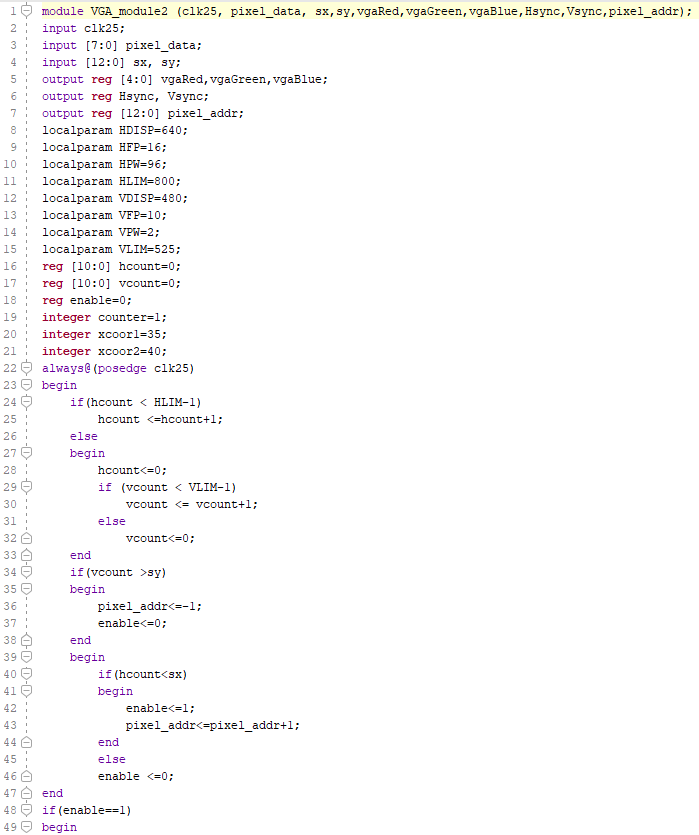

Task

4

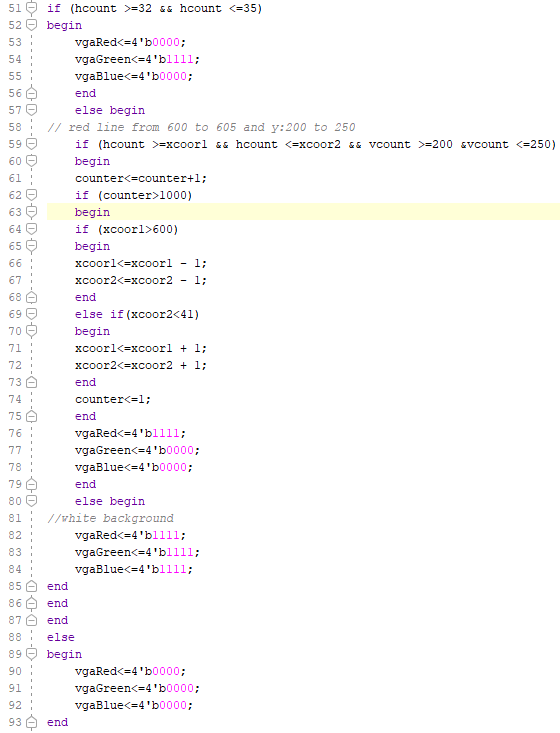

Task 4: In this task we created a white background as well as a green line of 4 pixels wide and a smaller red line that bounces from the green line and the other edge to be displayed by VGA from the BASYS 3 Board.

Task 4: In this task we created a white background as well as a green line of 4 pixels wide and a smaller red line that bounces from the green line and the other edge to be displayed by VGA from the BASYS 3 Board.