Figure 1. Creating and simulating an AND gate in vivado.

Task 2

Video 1. Volatile and non-volatile methods of programming an AND gate into the FPGA.

Video 3. Volatile and non-volatile methods of programming an XOR gate into the FPGA.

Video 1. Volatile and non-volatile methods of programming an AND gate into the FPGA.

Task

3

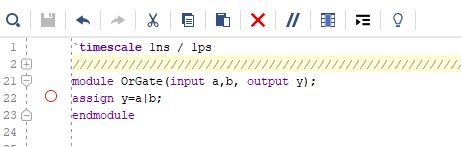

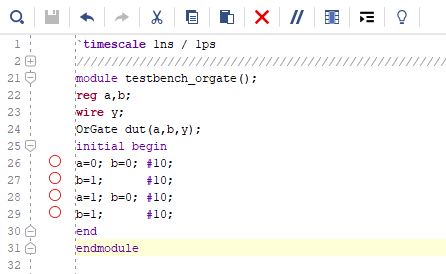

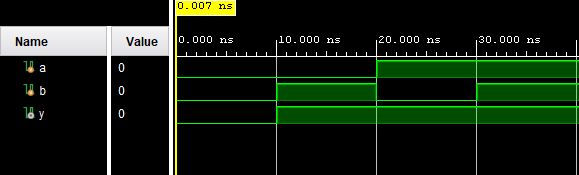

Figure 2. Creating and simulating an OR gate in vivado.

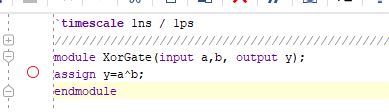

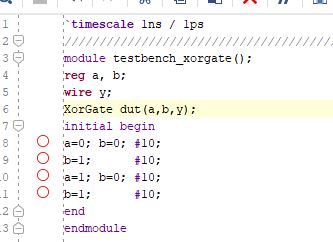

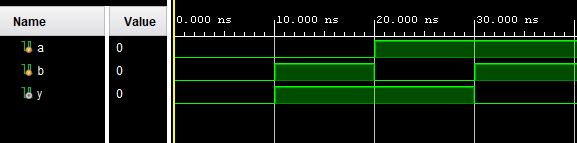

Figure 3. Creating and simulating an XOR gate in vivado.

Video 2. Volatile and

non-volatile methods of programming an OR gate into the FPGA.Figure 2. Creating and simulating an OR gate in vivado.

Figure 3. Creating and simulating an XOR gate in vivado.

Video 3. Volatile and non-volatile methods of programming an XOR gate into the FPGA.