Task 1. Code and simulation of an SR Latch done in Vivado.

Task 1.1. Code and simulation of an SR Flip-Flop done in Vivado.

Task 1.2. Code and simulation of a D Flip-Flop done in Vivado.

Task 2

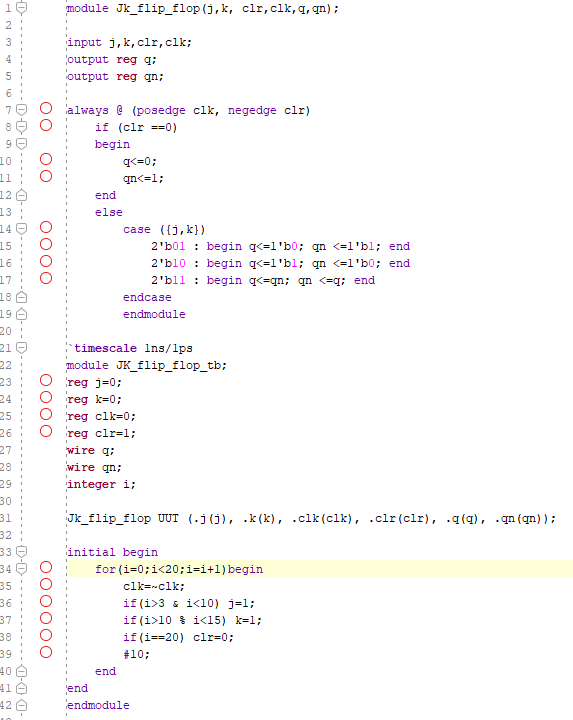

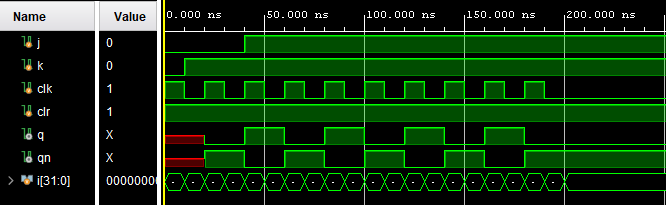

Task 2. Code and simulation of a JK Flip-Flop done in Vivado.

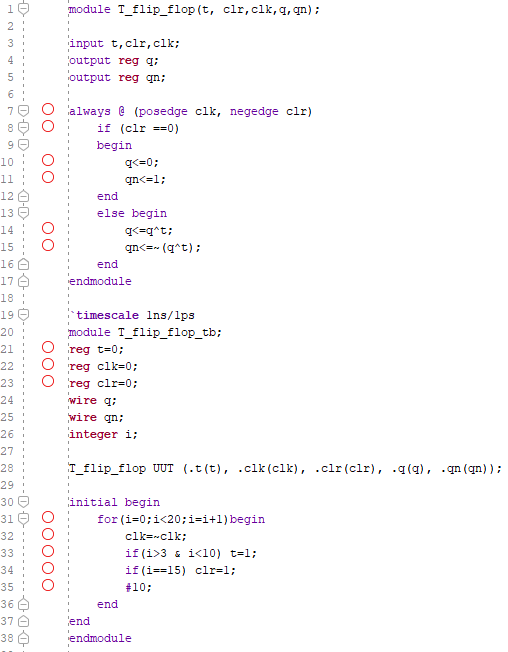

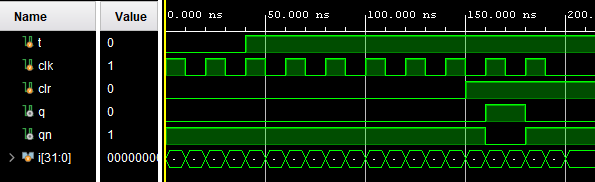

Task 2.2. Code and simulation of a T Flip-Flop done in Vivado.

Task 2. Code and simulation of a JK Flip-Flop done in Vivado.

Task 2.2. Code and simulation of a T Flip-Flop done in Vivado.

Task 3

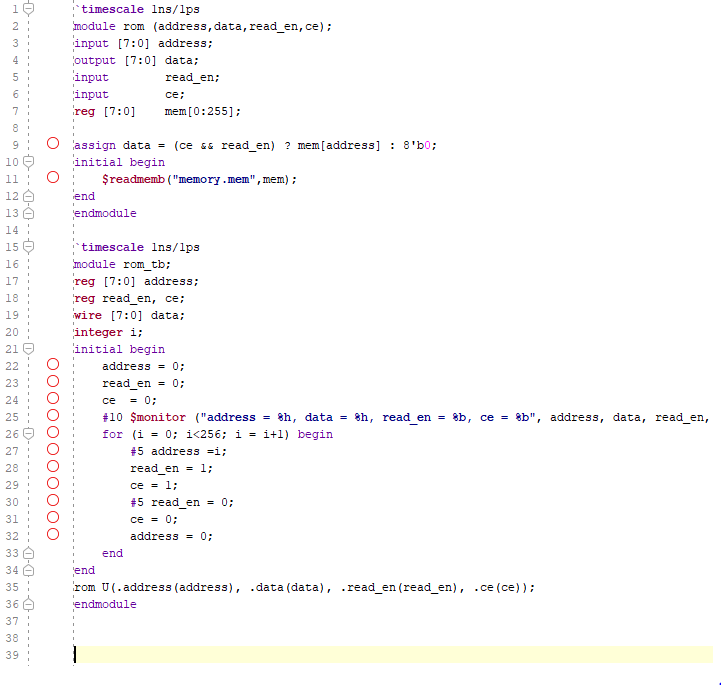

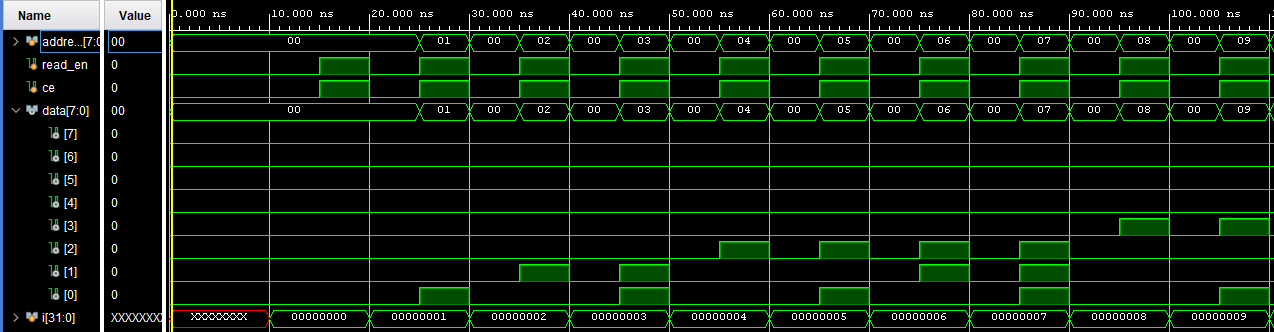

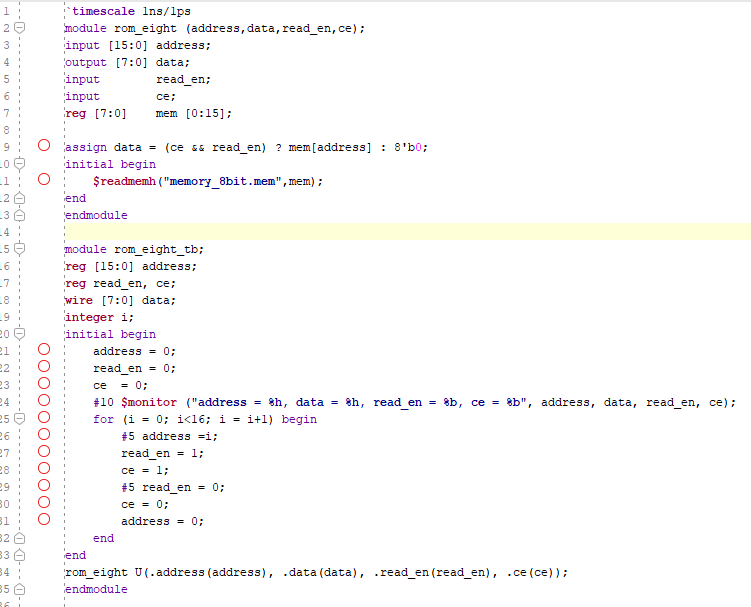

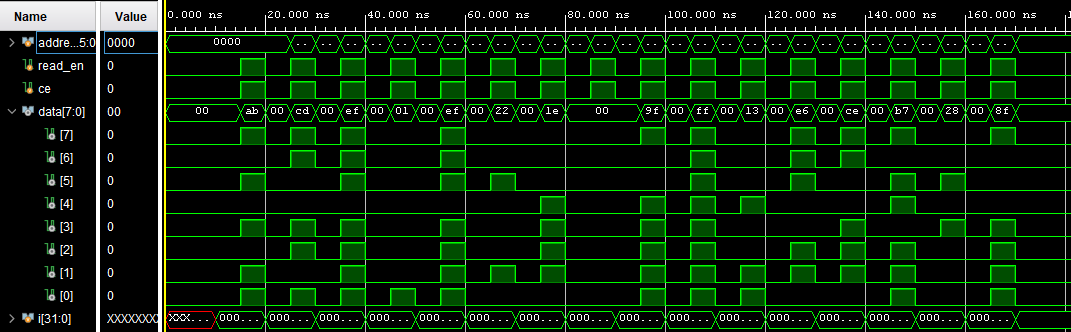

Task 3.1. Code and simulation of a ROM file reading 8-bit binary numbers done in Vivado.

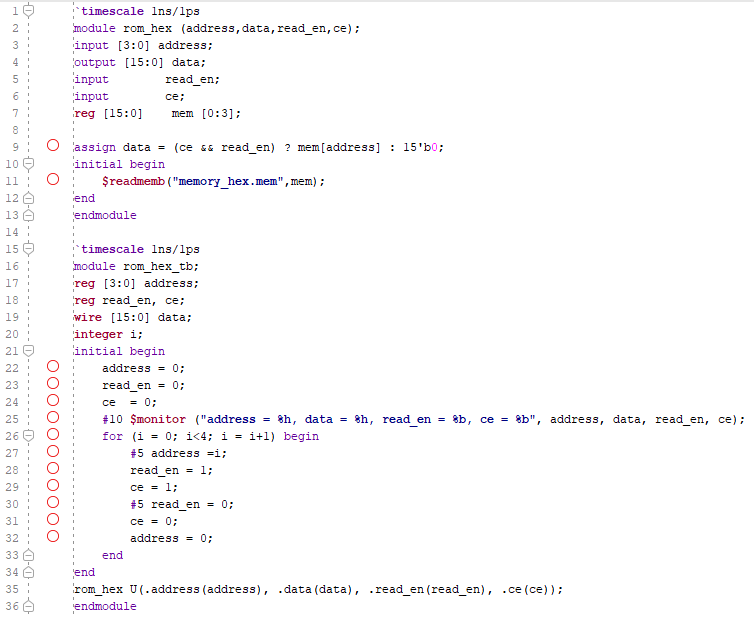

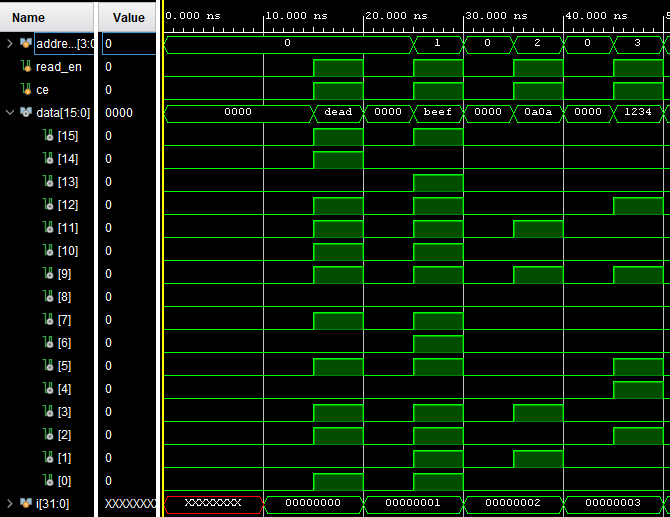

Task 3.2. Code and simulation of a ROM file reading hex data done in Vivado.

Task 3.3. Code and simulation of a ROM file reading 8-bit data done in Vivado.

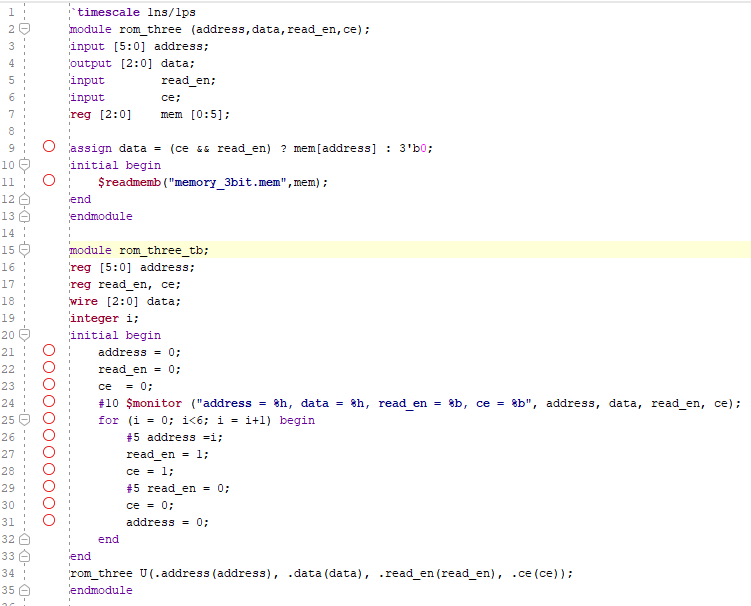

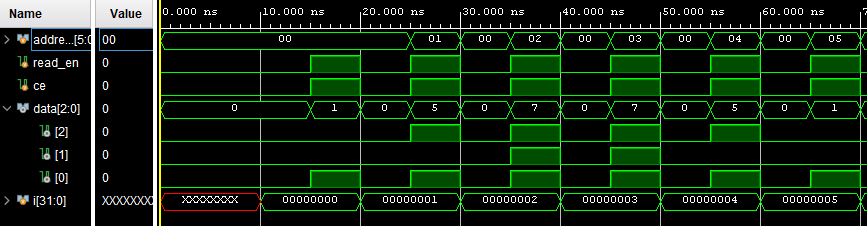

Task 3.4. Code and simulation of a ROM file reading 3-bit data done in Vivado.

Task 3.1. Code and simulation of a ROM file reading 8-bit binary numbers done in Vivado.

Task 3.2. Code and simulation of a ROM file reading hex data done in Vivado.

Task 3.3. Code and simulation of a ROM file reading 8-bit data done in Vivado.

Task 3.4. Code and simulation of a ROM file reading 3-bit data done in Vivado.