Figure 1. Code and simulation showing functionality of a Half Adder in Vivado.

Figure 2. Code and simulation showing functionality of a Full Adder in Vivado.

Task 2

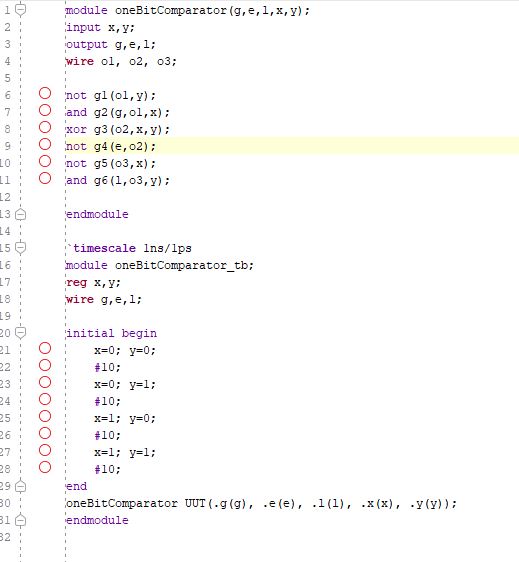

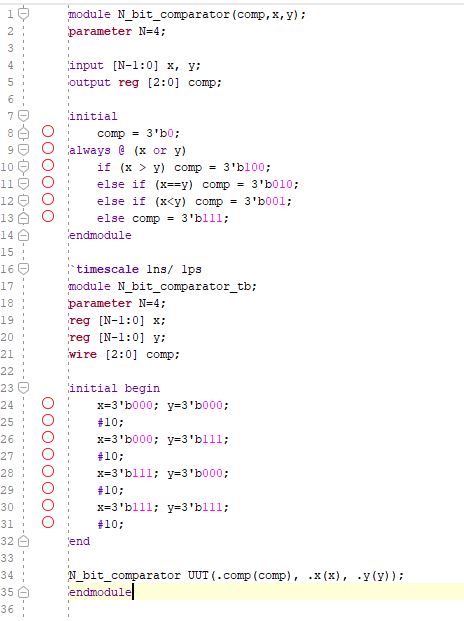

Figure 3. Code and simulation after adding a testbench to a 1-bit comparator in section 3.

Figure 3. Code and simulation after adding a testbench to a 1-bit comparator in section 3.

Task 3

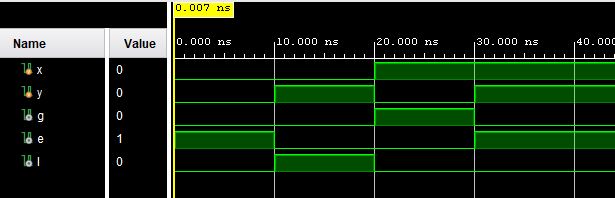

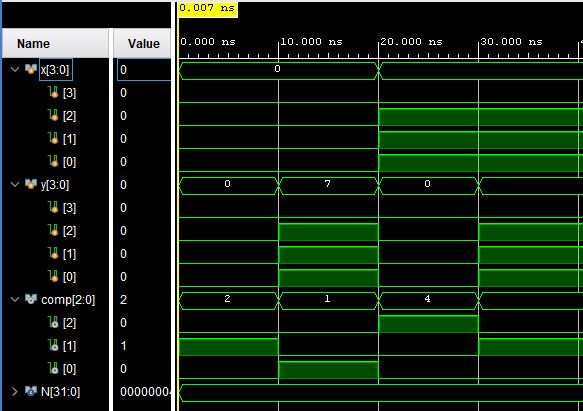

Figure 3. Code and simulation after adding a testbench to a 4-bit comparator in section 3.

Figure 3. Code and simulation after adding a testbench to a 4-bit comparator in section 3.

Task

4

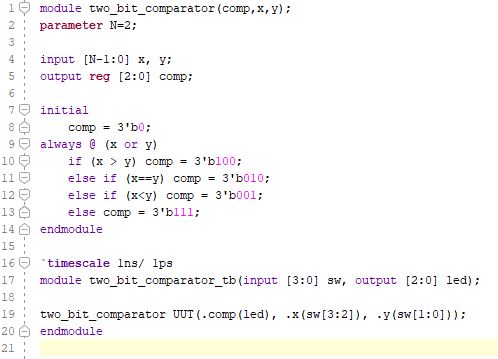

Task 4. Code and Video showing functionality of a 2-bit comparator on the Basys 3 board.

Task 4. Code and Video showing functionality of a 2-bit comparator on the Basys 3 board.

Task 5

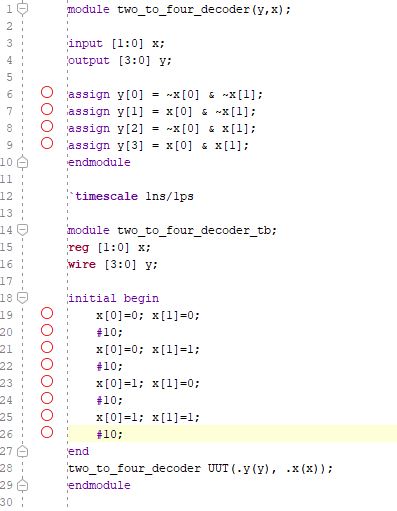

Figure 5. Code and simulation after adding a testbench to a 2-4 decoder in section 4.

Figure 5. Code and simulation after adding a testbench to a 2-4 decoder in section 4.

Task 6

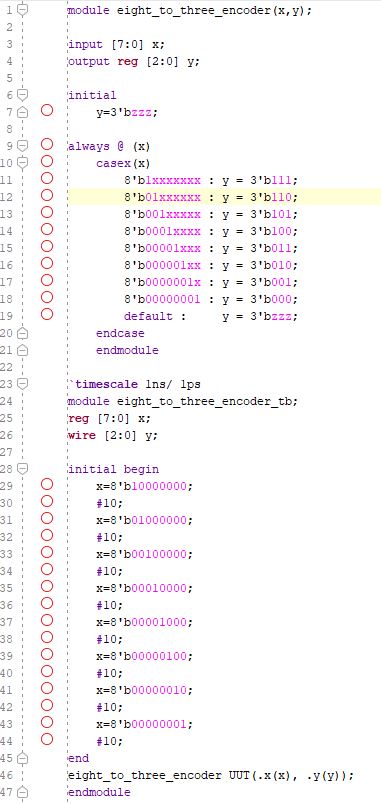

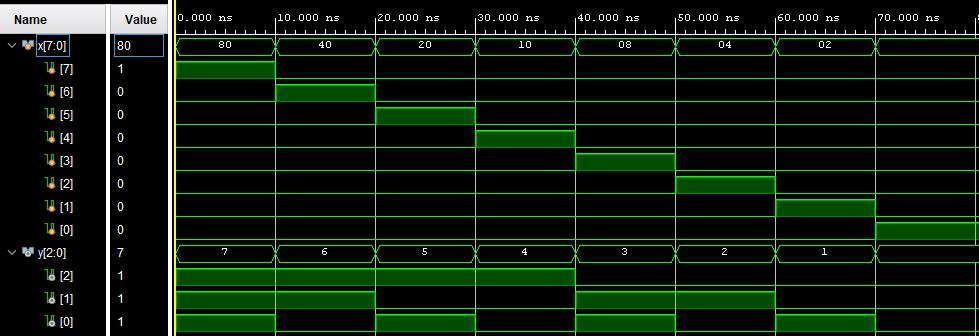

Figure 6. Code and simulation to verify logic after adding a testbench to an 8x3 encoder in section 5.

Figure 6. Code and simulation to verify logic after adding a testbench to an 8x3 encoder in section 5.

Task 7

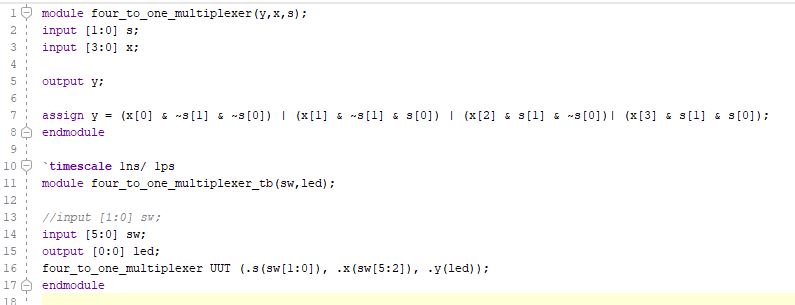

Task 7. Code and Video showing functionality of a 4-to-1 multiplexer on the Basys 3 board.

Task 7. Code and Video showing functionality of a 4-to-1 multiplexer on the Basys 3 board.

Task

9

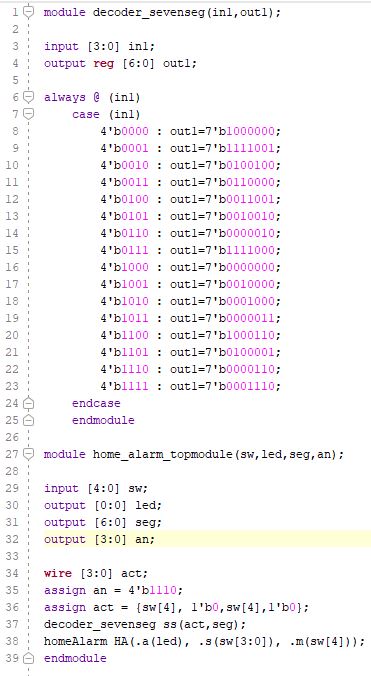

Task 9. Code and Video showing functionality of an improved home alarm system with 7 segment display to show A when Armed on the Basys 3 board.

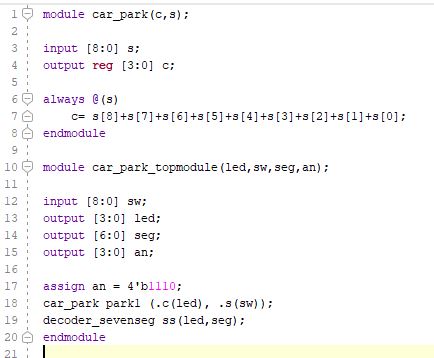

Task 9.2. Code and Video showing functionality of an improved car count system with 7 segment display to show number of cars in carport on the Basys 3 board.

Task 9. Code and Video showing functionality of an improved home alarm system with 7 segment display to show A when Armed on the Basys 3 board.

Task 9.2. Code and Video showing functionality of an improved car count system with 7 segment display to show number of cars in carport on the Basys 3 board.