CE 433 Basics

Name: Max Krauss

Email:

mtkrauss@fortlewis.edu

GVIM and Vivado Basics

Intro:

For our first assignment, we will learn how to write code in GVIM and

then use that code to run simulations in Vivado by completing the

following tasks.

Materials: GVIM, Vivado, and a personal computer

Methods and Results:

1.

Use gvim and Vivado to simulate the examples in sections 2.1, 2.2, and

2.3. Post snapshots of gvim windows and vivado simulation results in

your report. You must create testbenches for your simulations. (20

points)

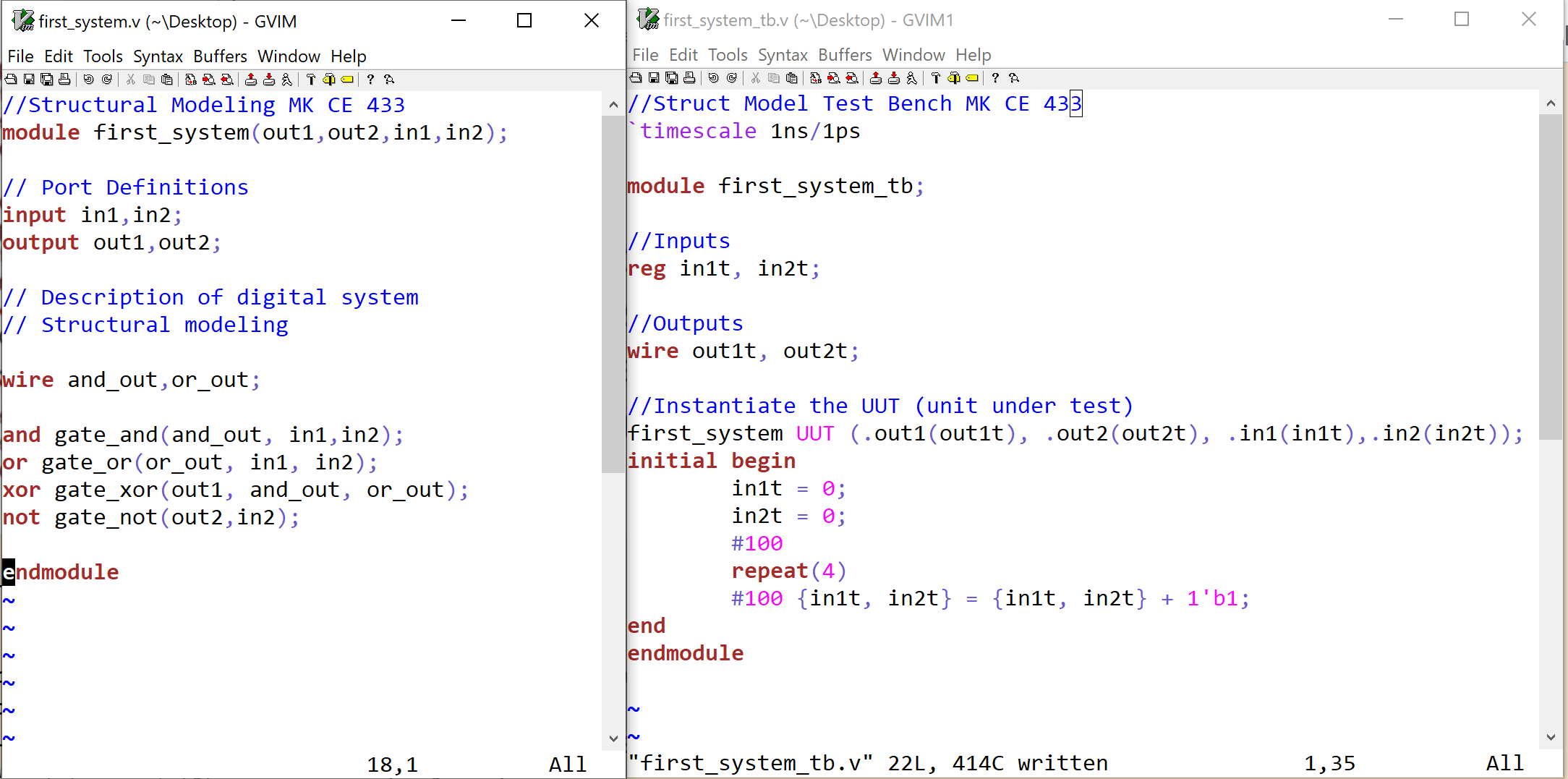

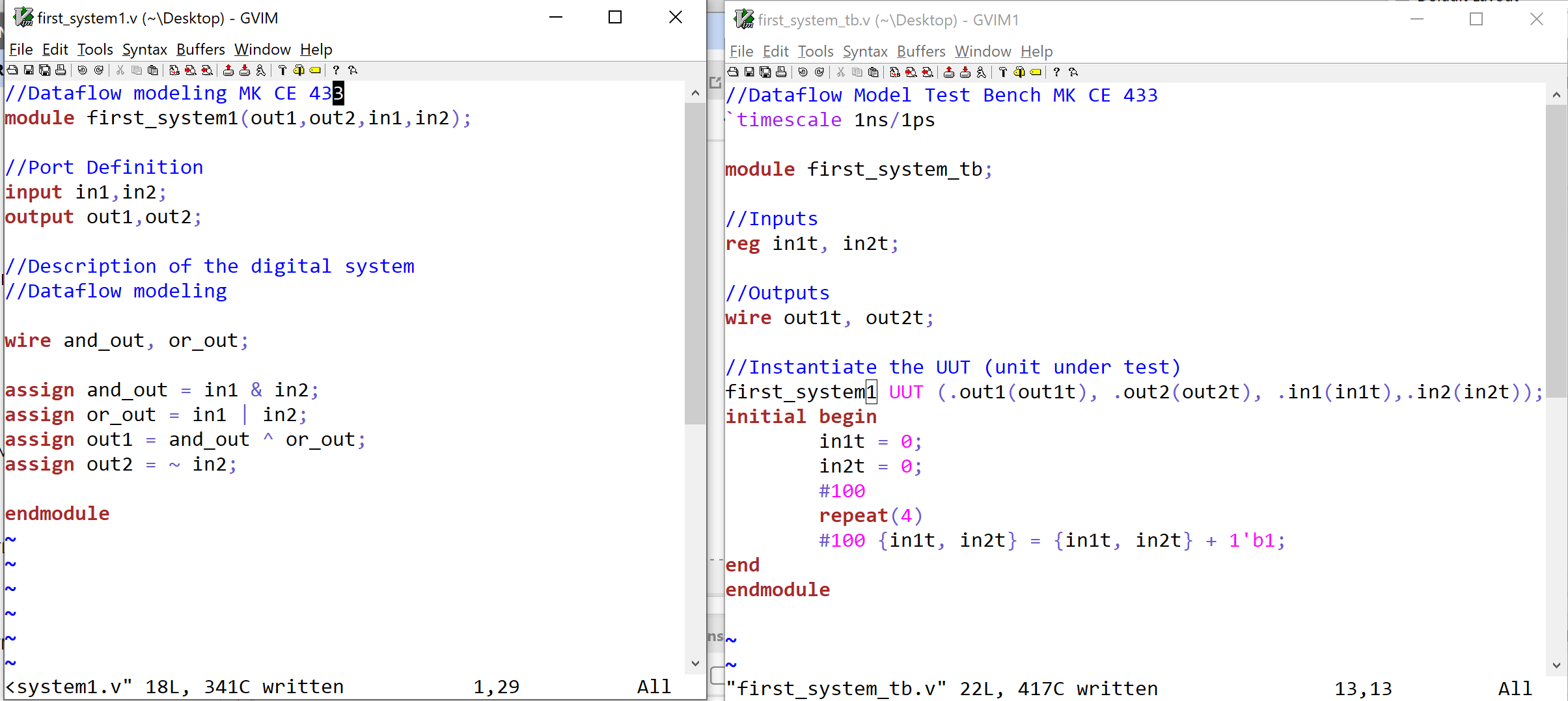

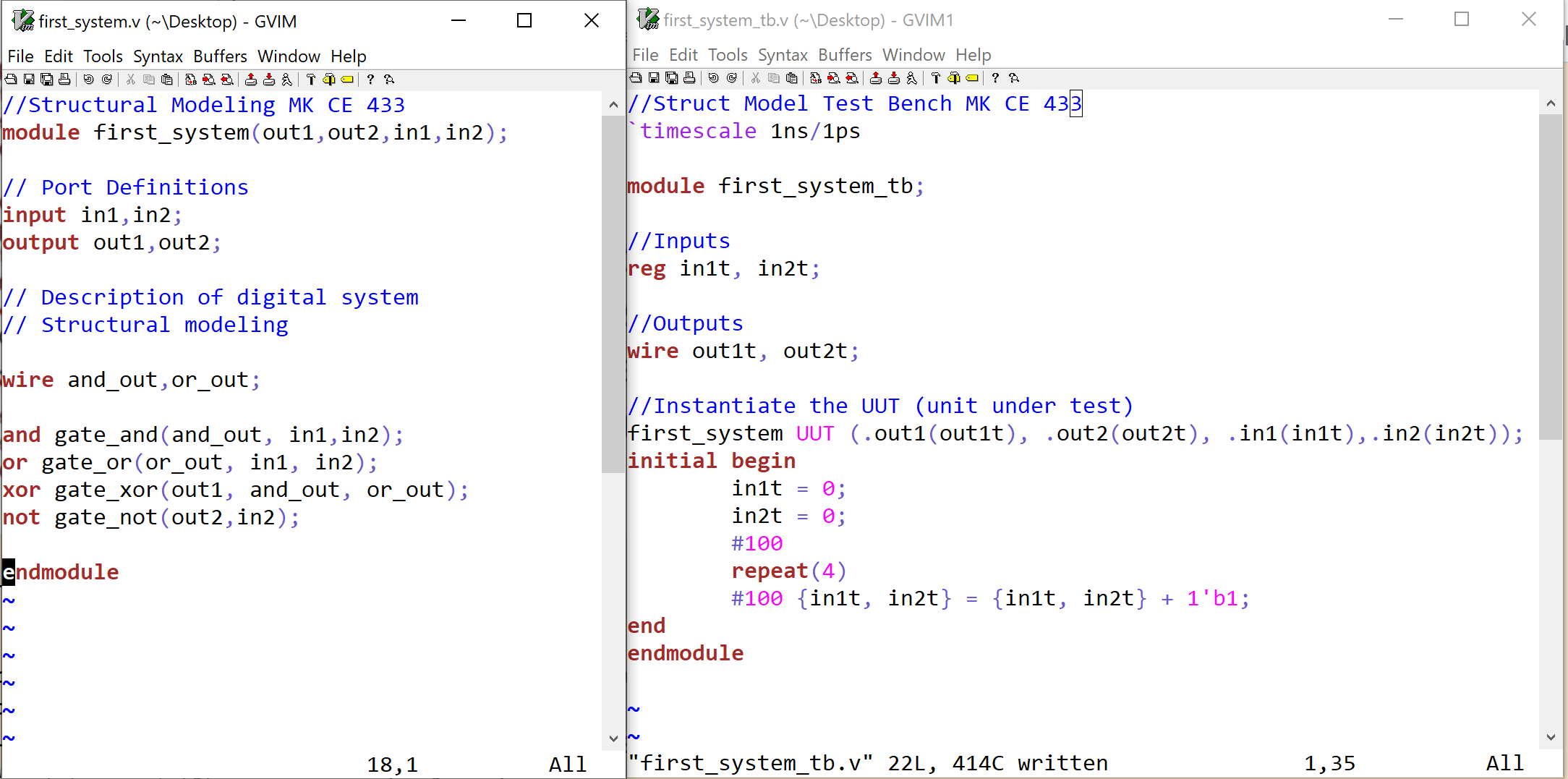

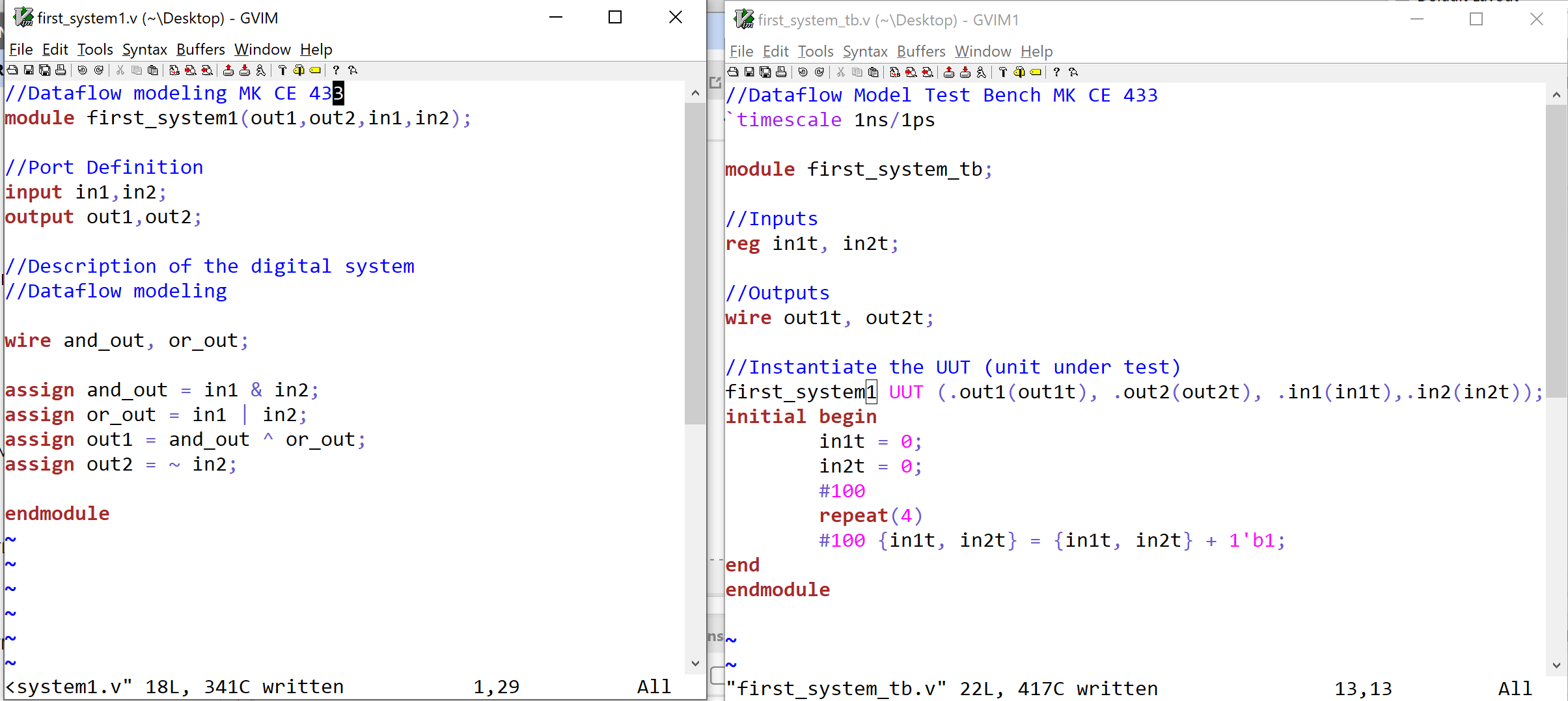

Figure 1 : GVIM Code for 2.1

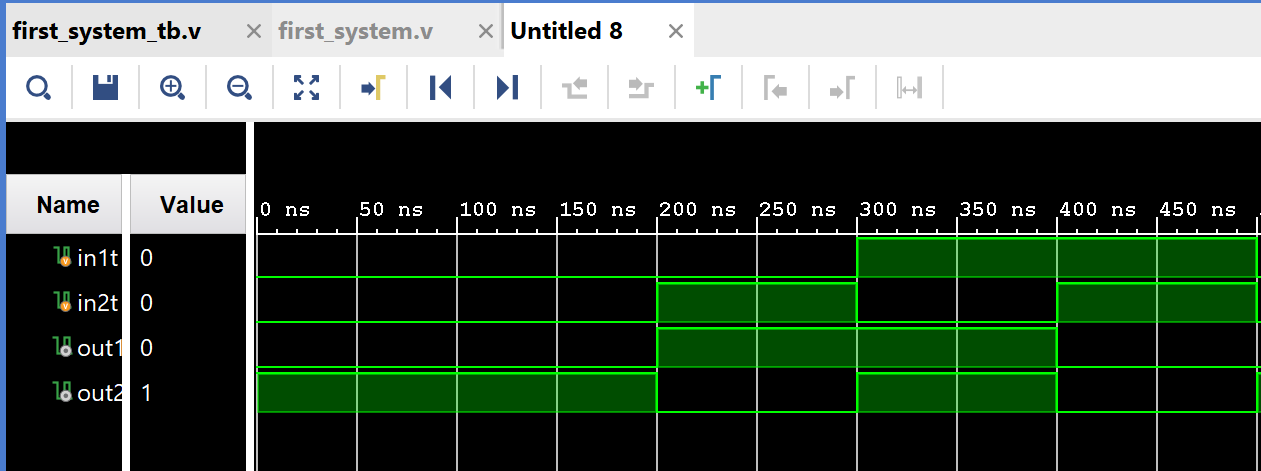

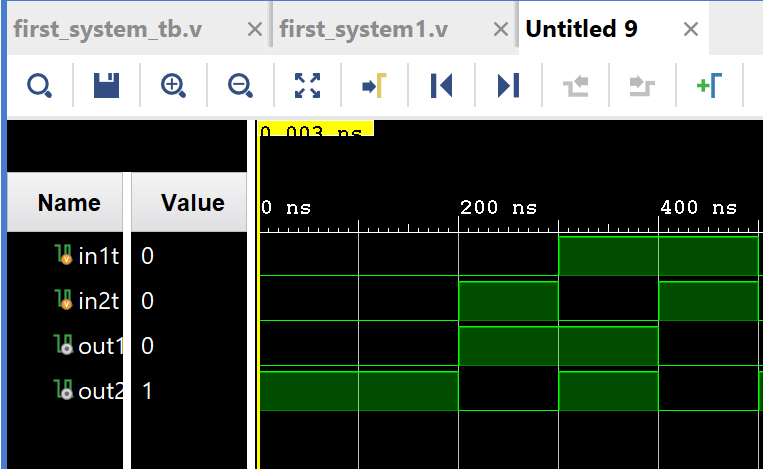

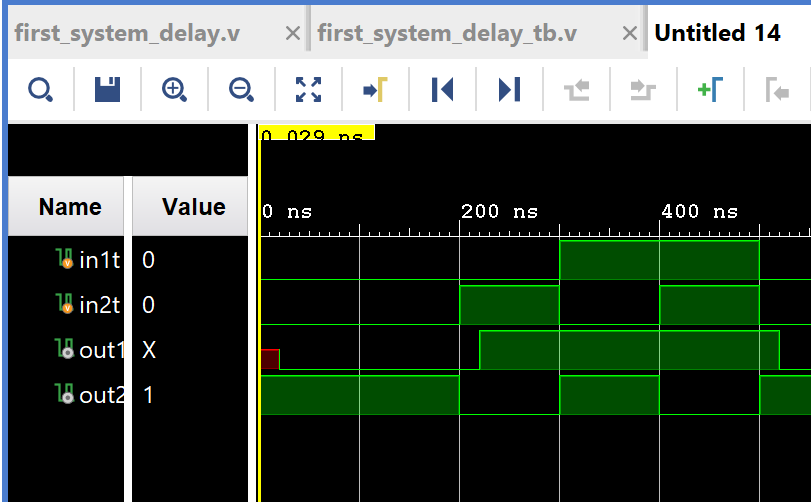

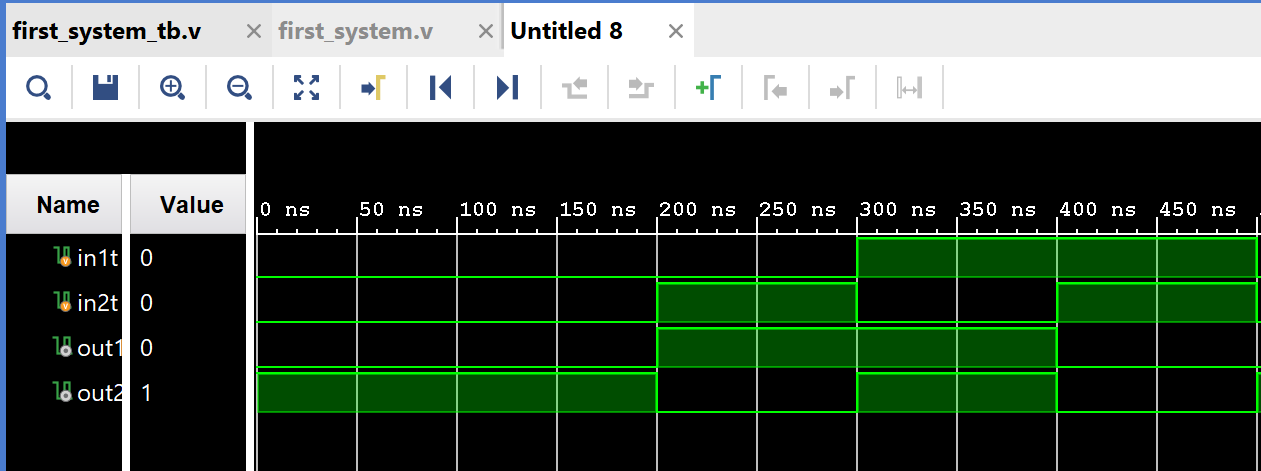

Figure 1.2: Vivado simulation for 2.1

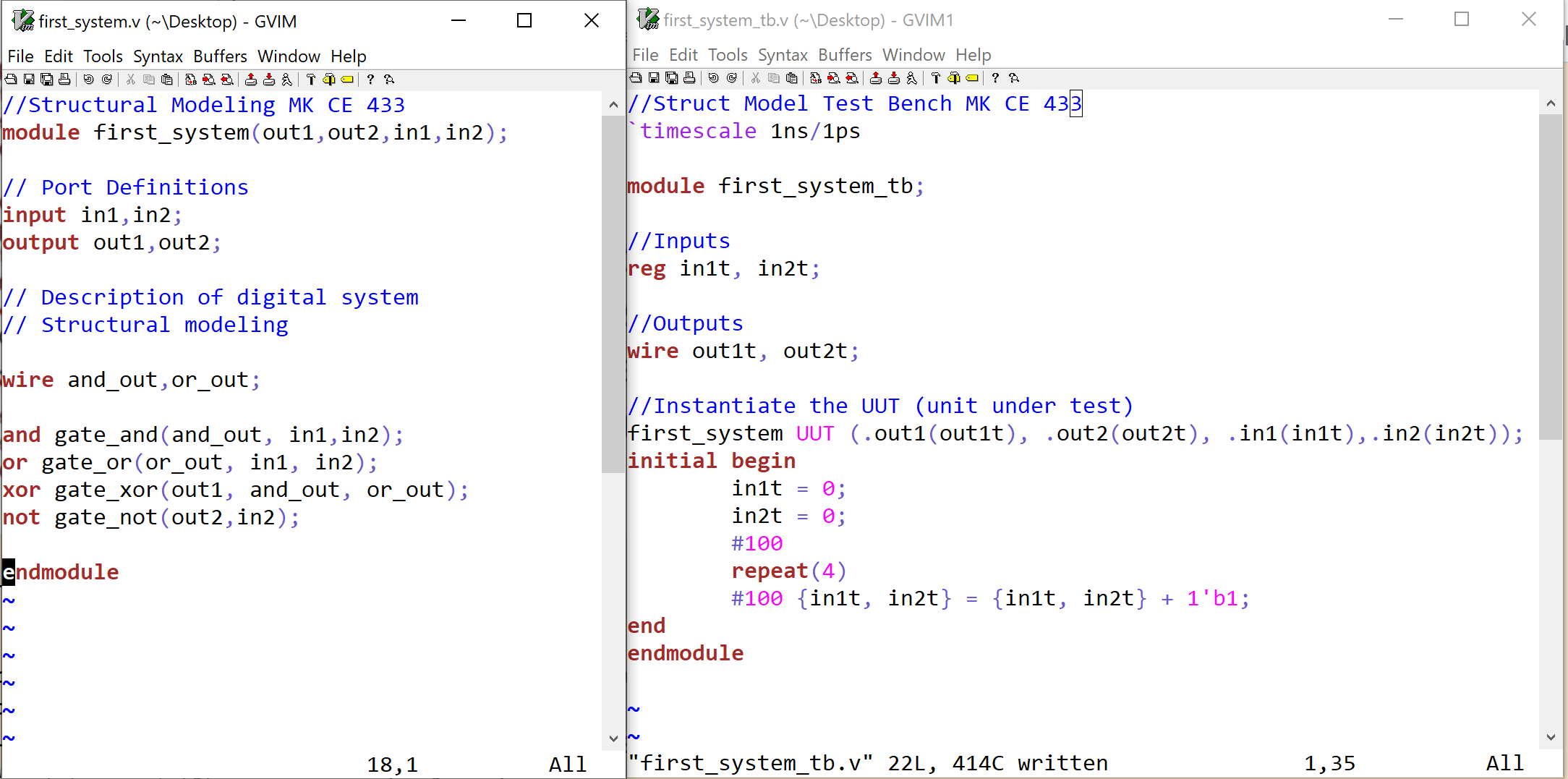

Figure 1.3: GVIM Code for 2.2

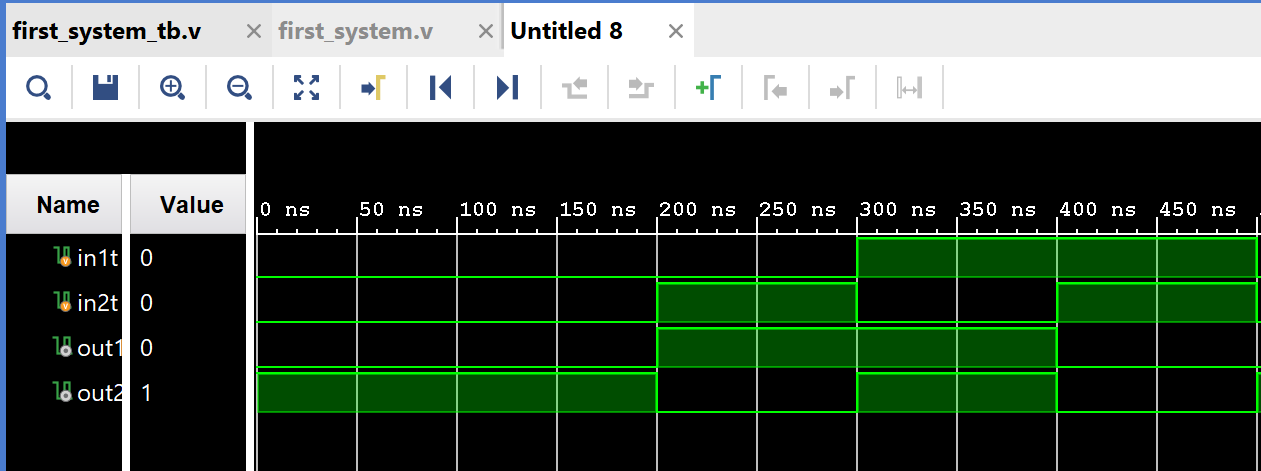

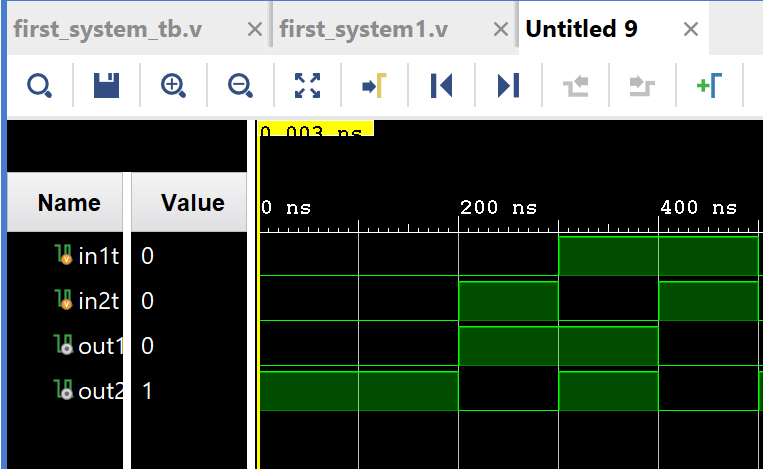

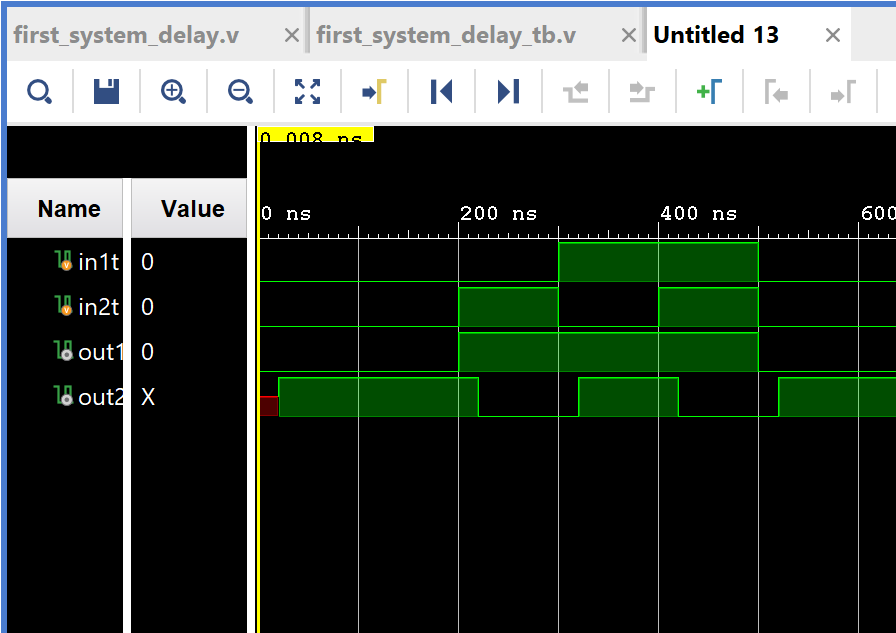

Figure 1.4: Vivado simulation for 2.2

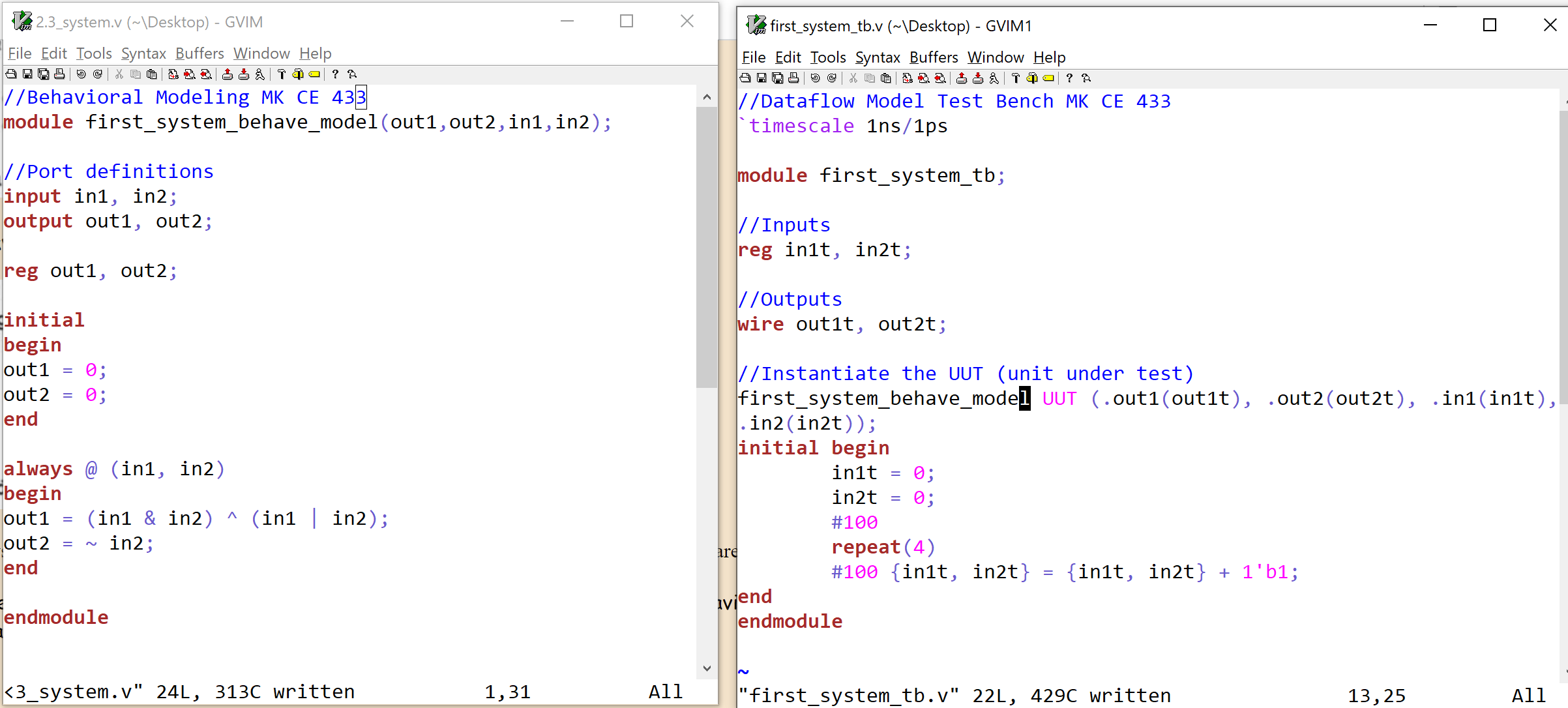

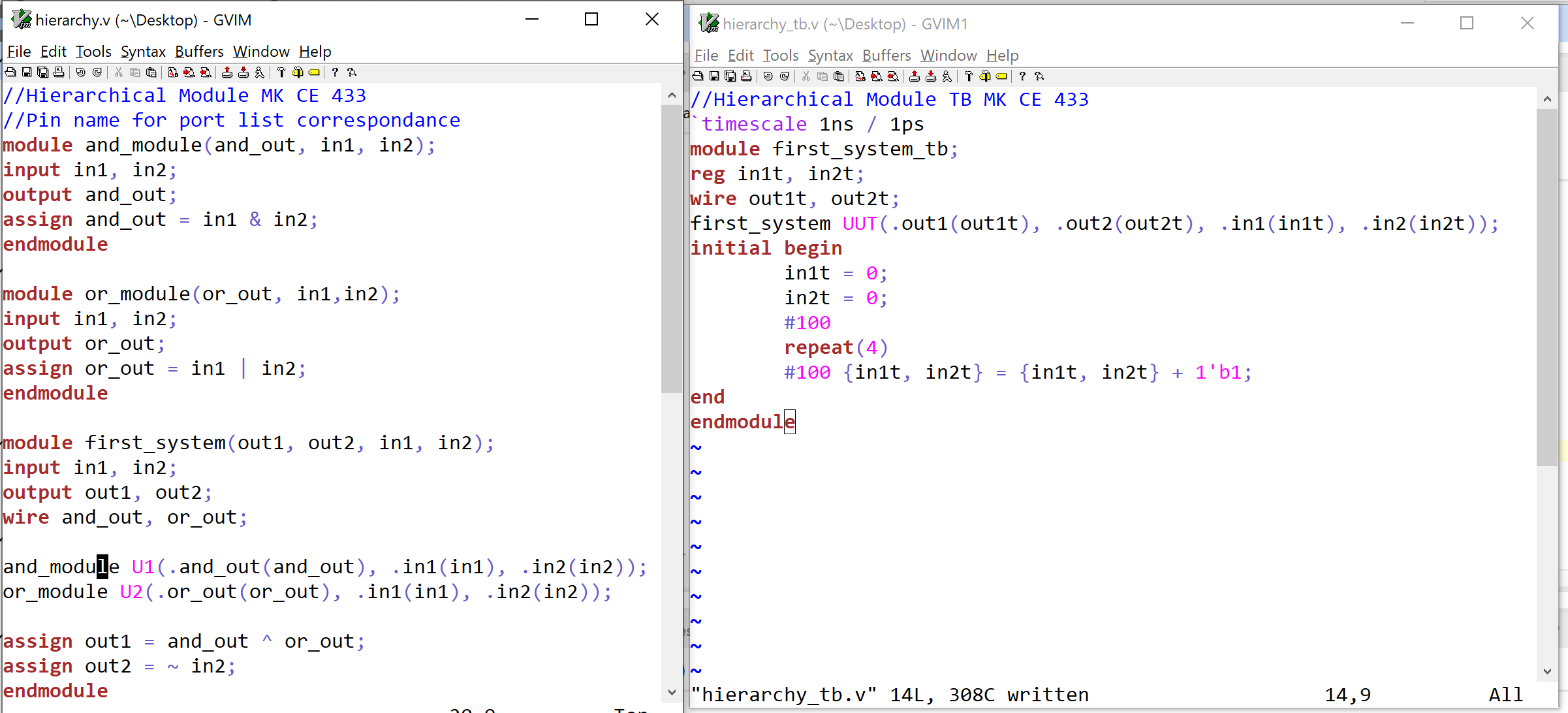

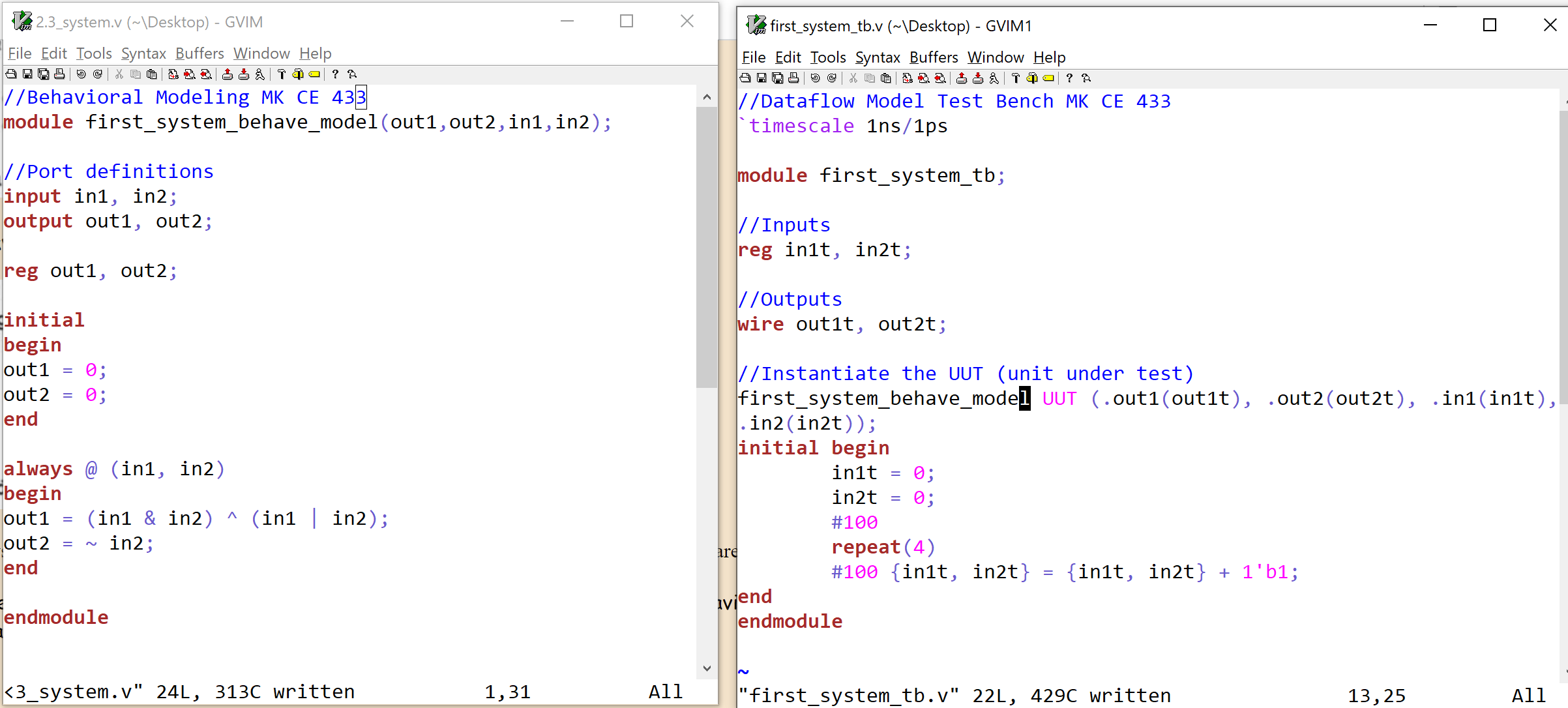

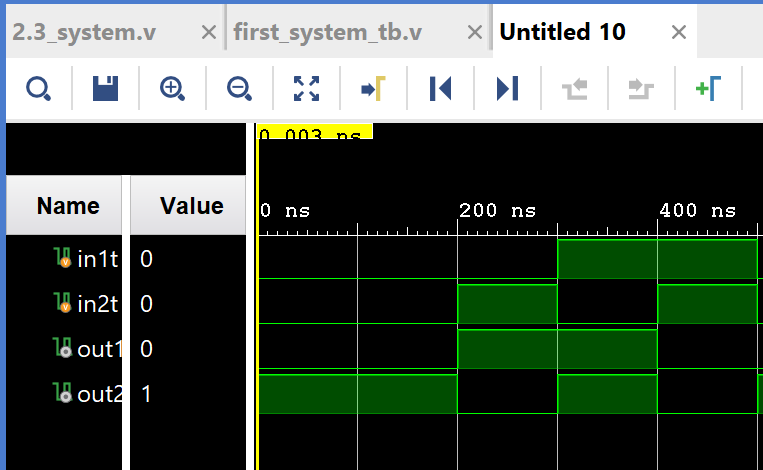

Figure 1.5: GVIM code for 2.3

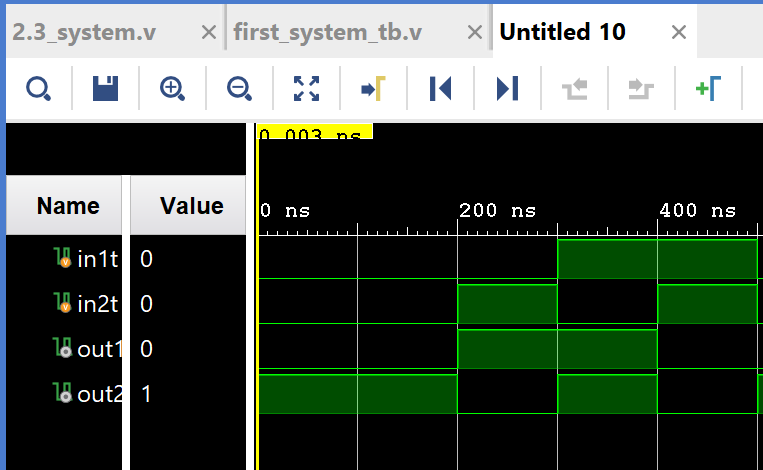

Figure 1.6: Vivado simulation for 2.3

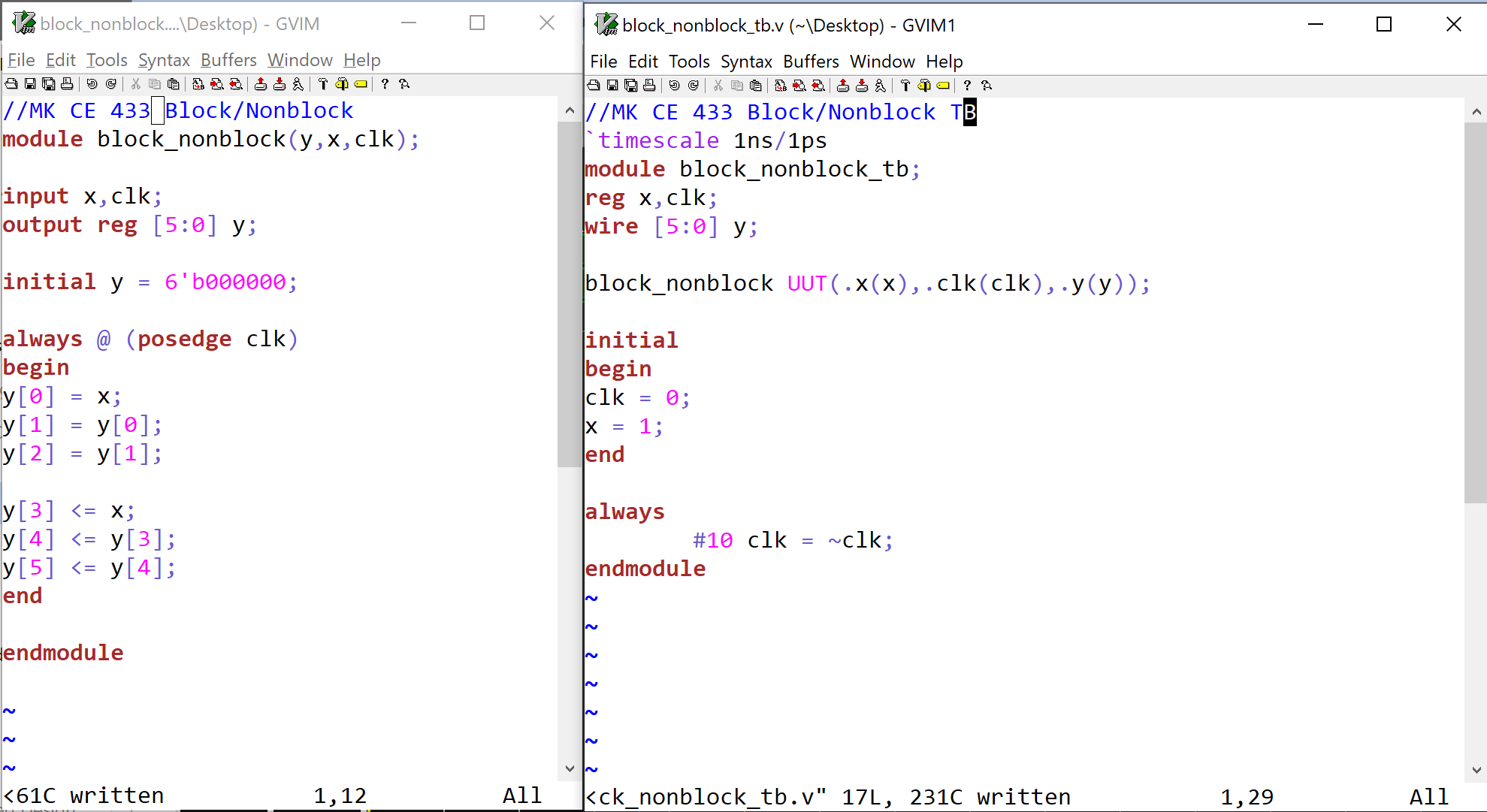

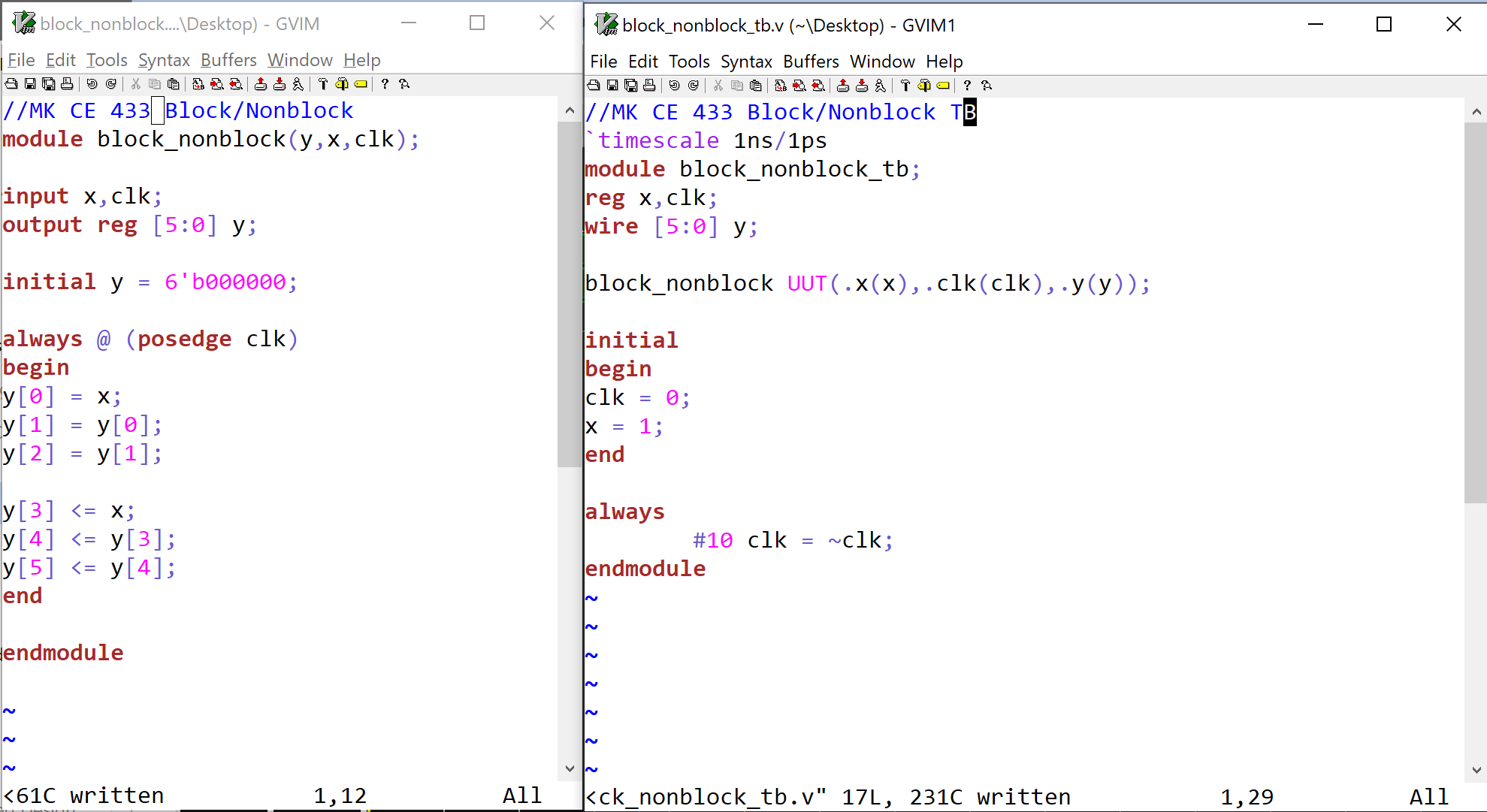

2. Run a simulation to show the difference of blocking and non-blocking assignment in the example in section 2.4. (20 points)

Figure 2: GVIM code for 2.4

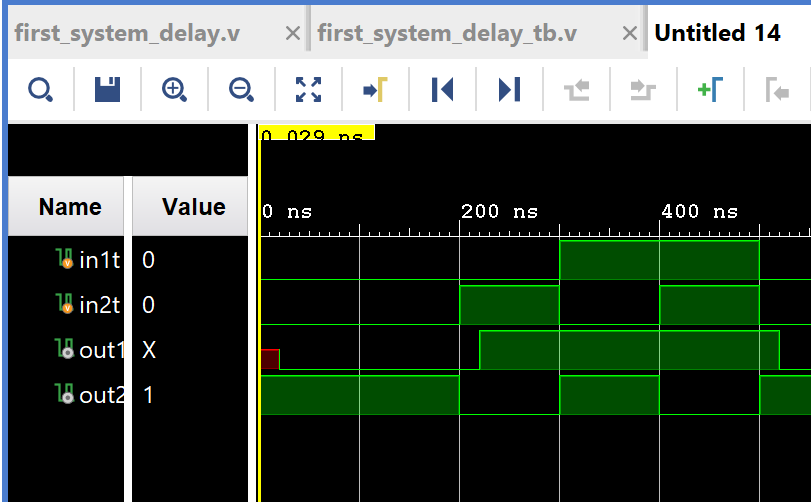

Figure 2.1: Vivado simulation for 2.4

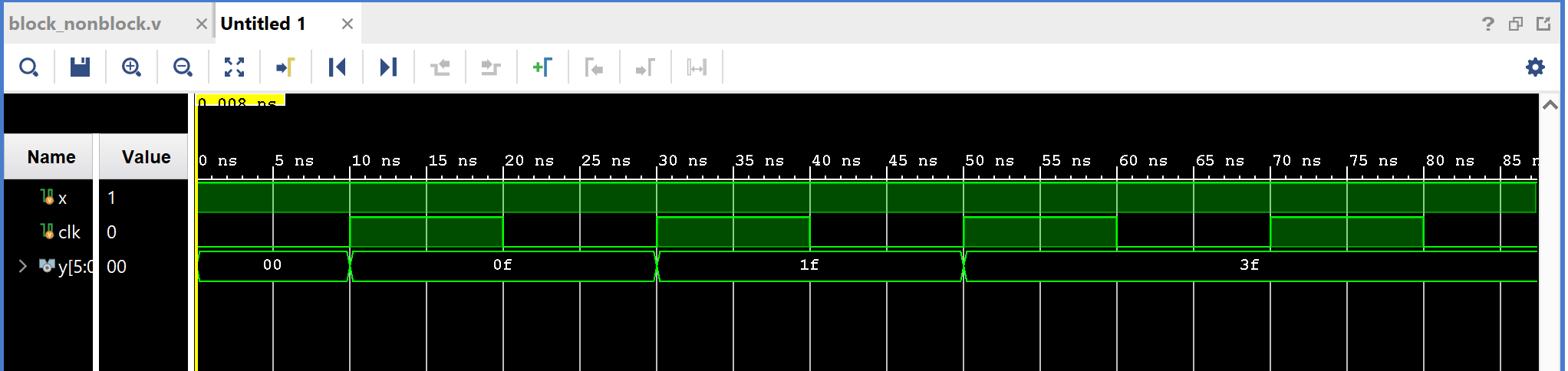

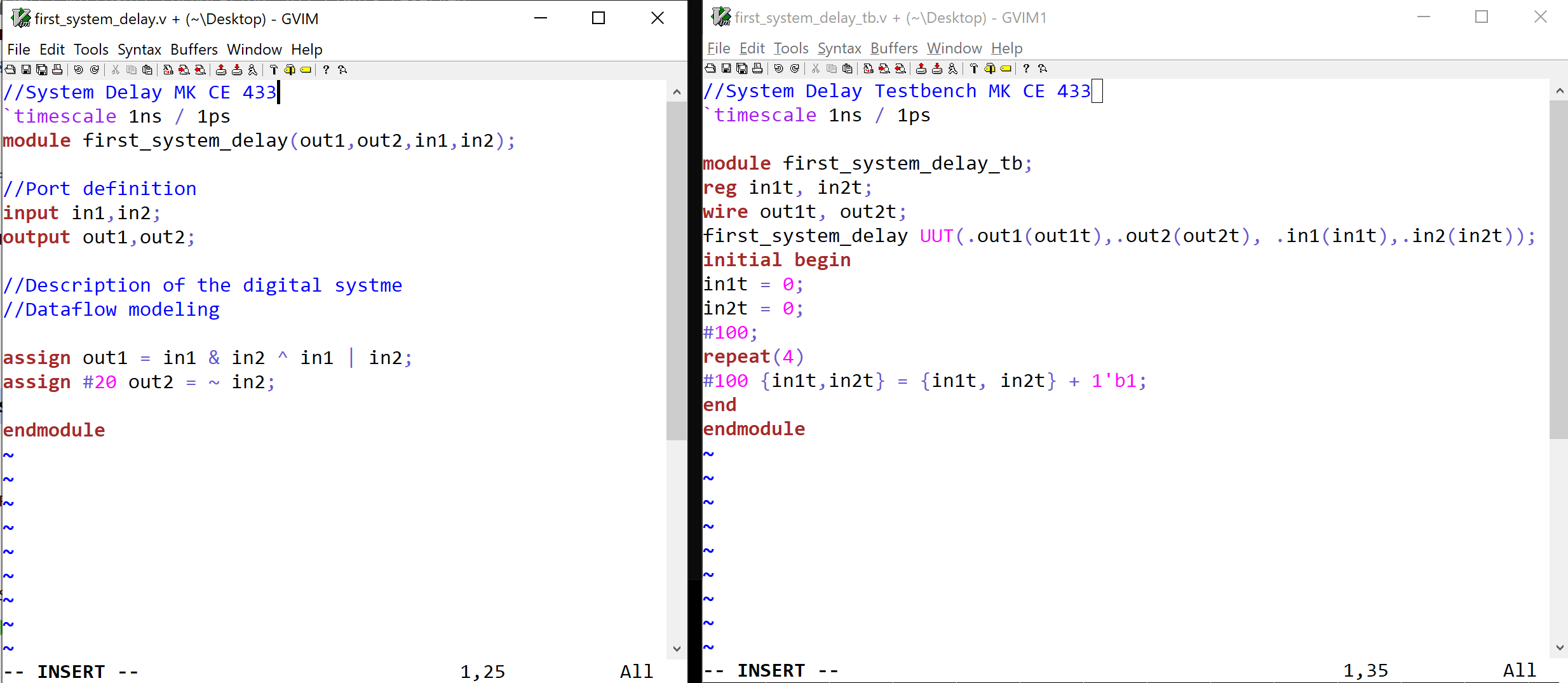

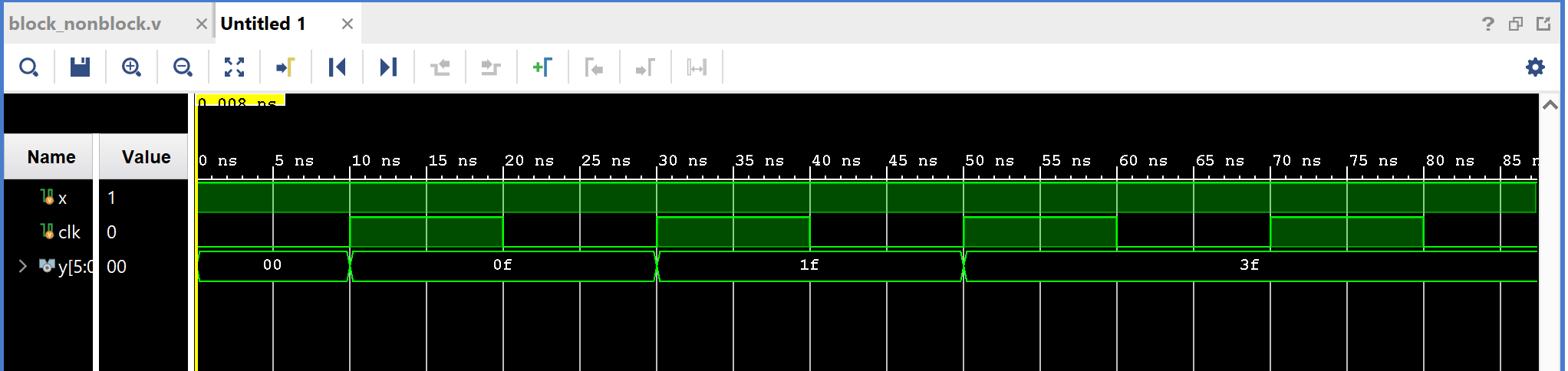

3. Repeat the simulation example in section 2.5. (20 points)

Figure 3: GVIM code for 2.5

Figure 2.3: Vivado simulation for 2.5

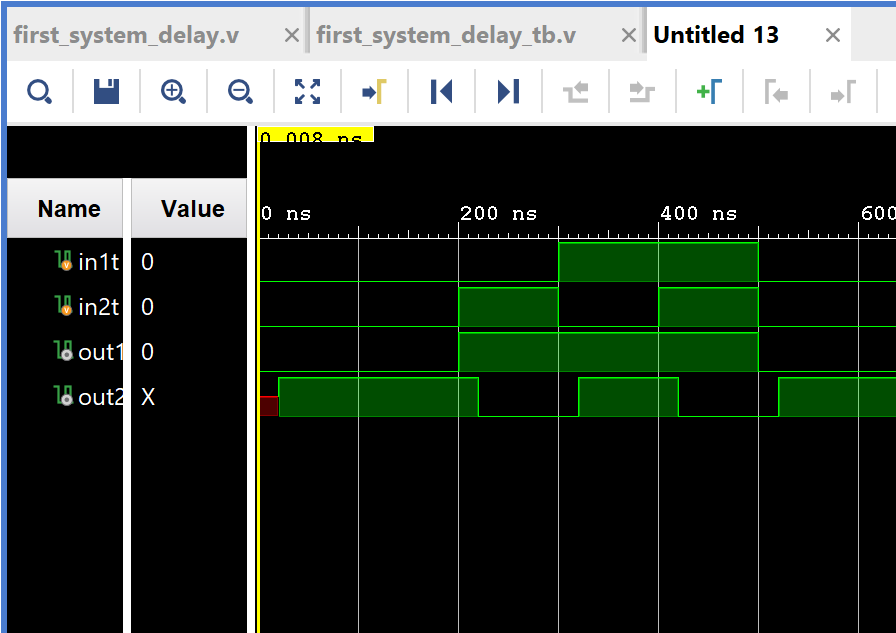

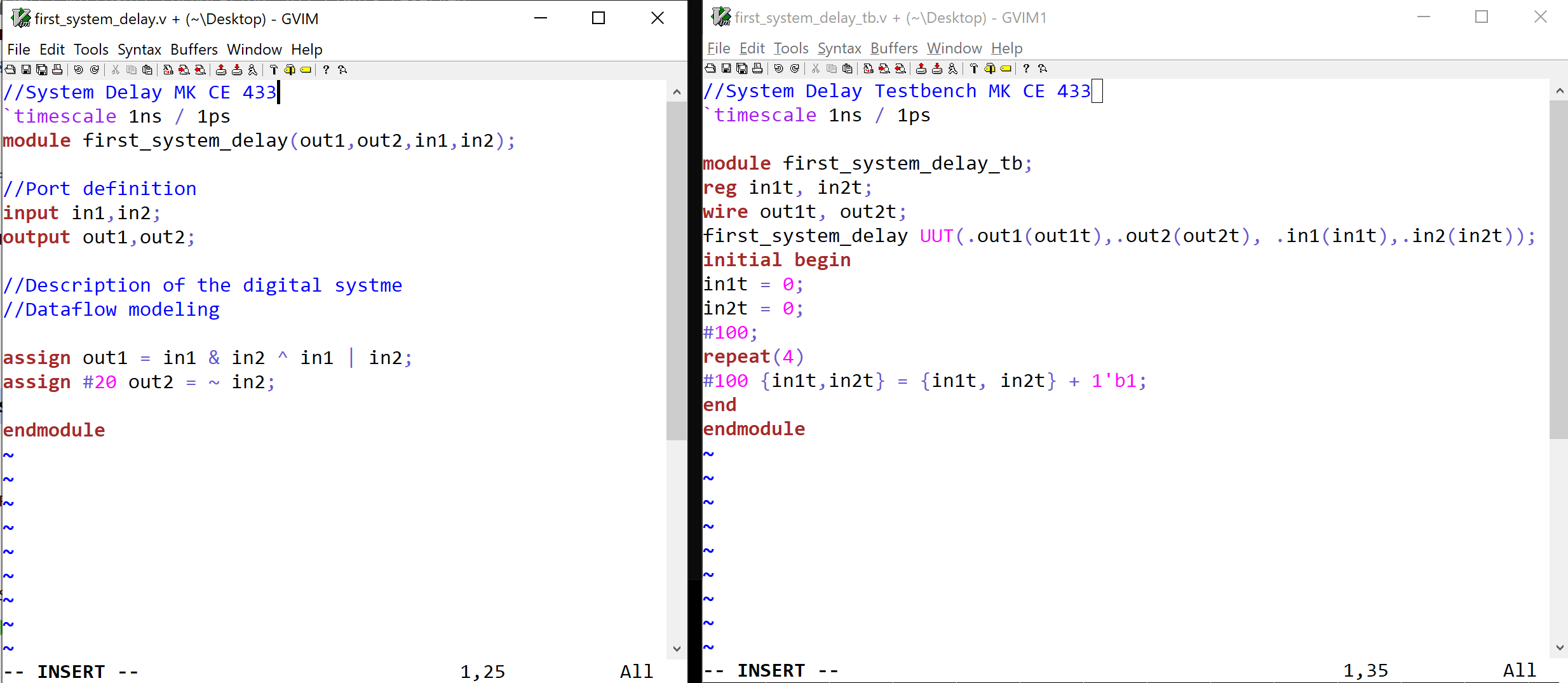

4. For the example in section 2.5, move the 20 ns delay from Line 25 to Line 24 and run the simulation. (20 points)

Figure 4: Vivado simulation for the modified 2.5

5.

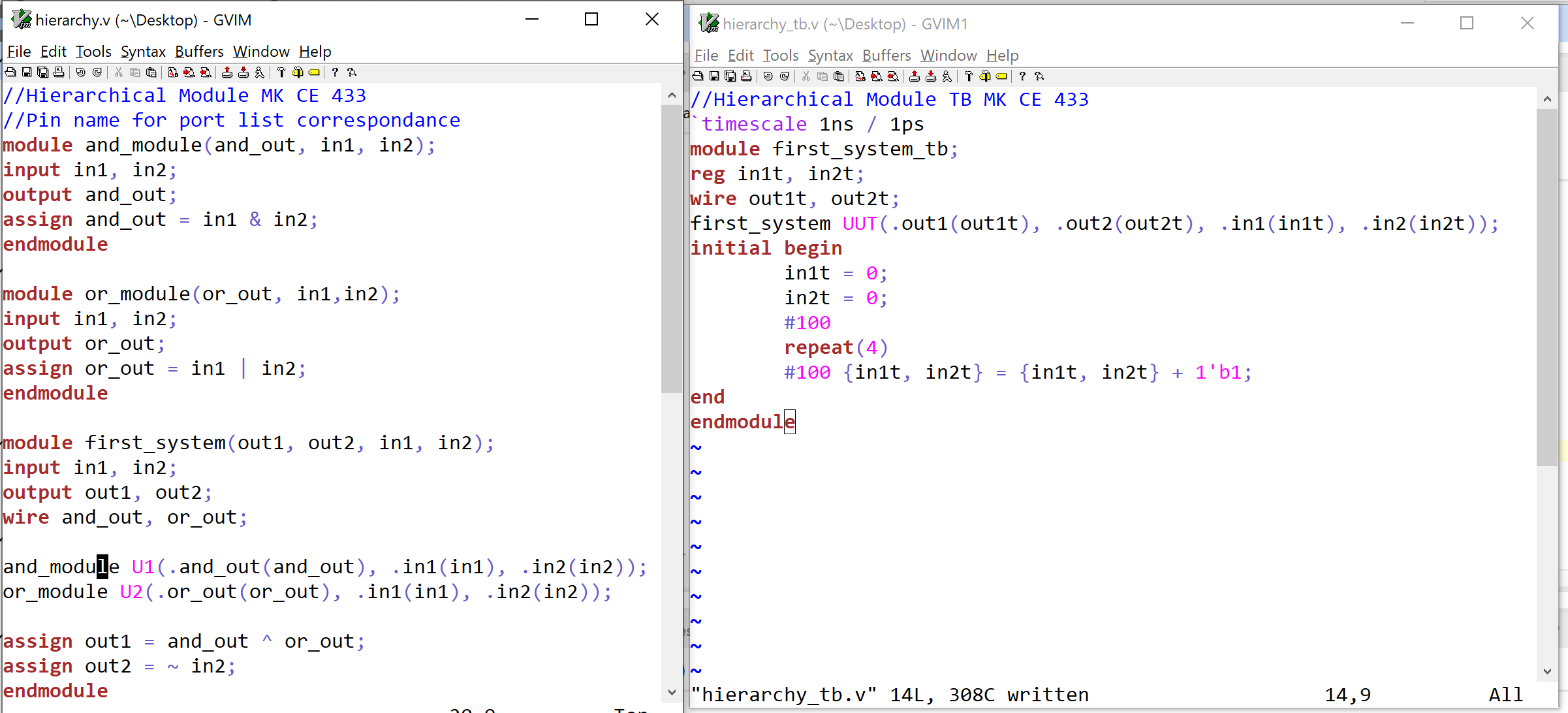

Use gvim and vivado, repeat the example in section 2.6. Post the gvim

windows and the vivado simulation windows for credit. (20 points)

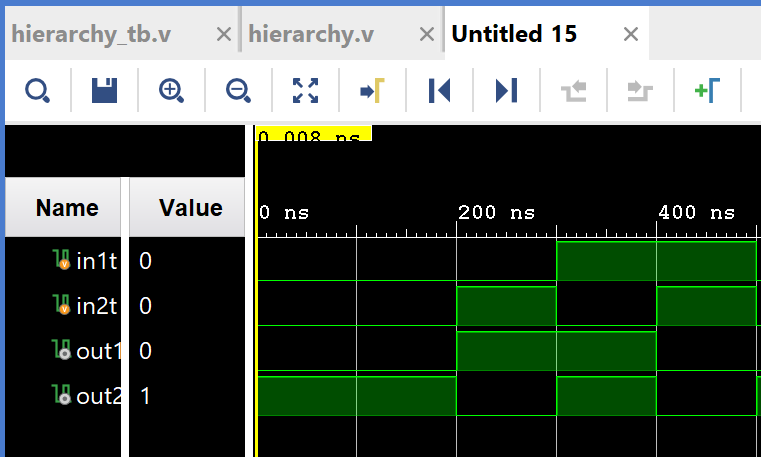

Figure 5: GVIM code for 2.6

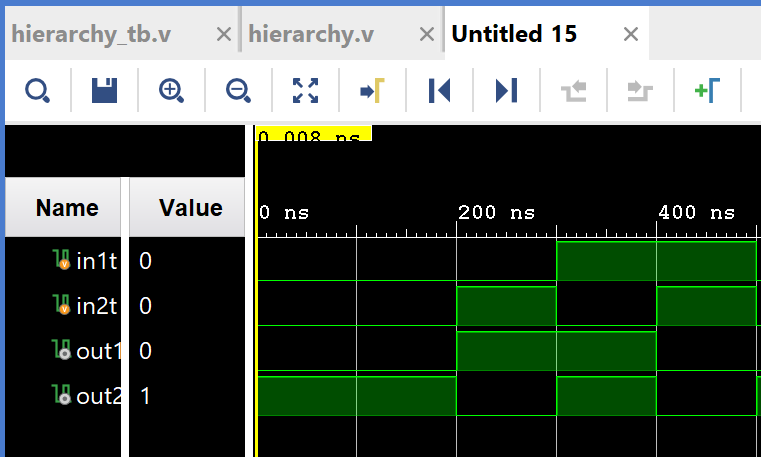

Figure 5.1: Vivado simulation for 2.6

Discussion:

Learning GVIM is very crucial

as a computer engineer since it is widely used in the industry. The

application of Vivado helps us visualize how certain methods of coding

apply in the real world. Vivado along with Verilog can be used to

program FPGA's which can then be used in the field for various

applications. Observation of Vivado simulations allows for the user to

grasp what is actually happening inside of digital systems and opens up

the topic for a deeper understanding of FPGA's.