8-bit SAR ADC Final Project

Jesse Duran

Spring 2021

ENGR 338

Introduction:

In the project we were tasked with creating an 8-bit Sucessive

Aproximation Register (SAR) Analog to Digital Converter (ADC) using

LTSpice. For this project we used 50nm technology, developed by Dr.

Baker, which operates at 1V. While not fabricateable, it is good for

simulation.The SAR was based off of Coumbia University's design [1] and

has consists of D-FlipFlops (DFF) which are made of 3input NAND gates.

The DFF used are the same as Texax Instuments (TI). Within the SAR is a

sequencer which handels the incoming bits from a comparitor and a shift

register which stores the states.

Results:

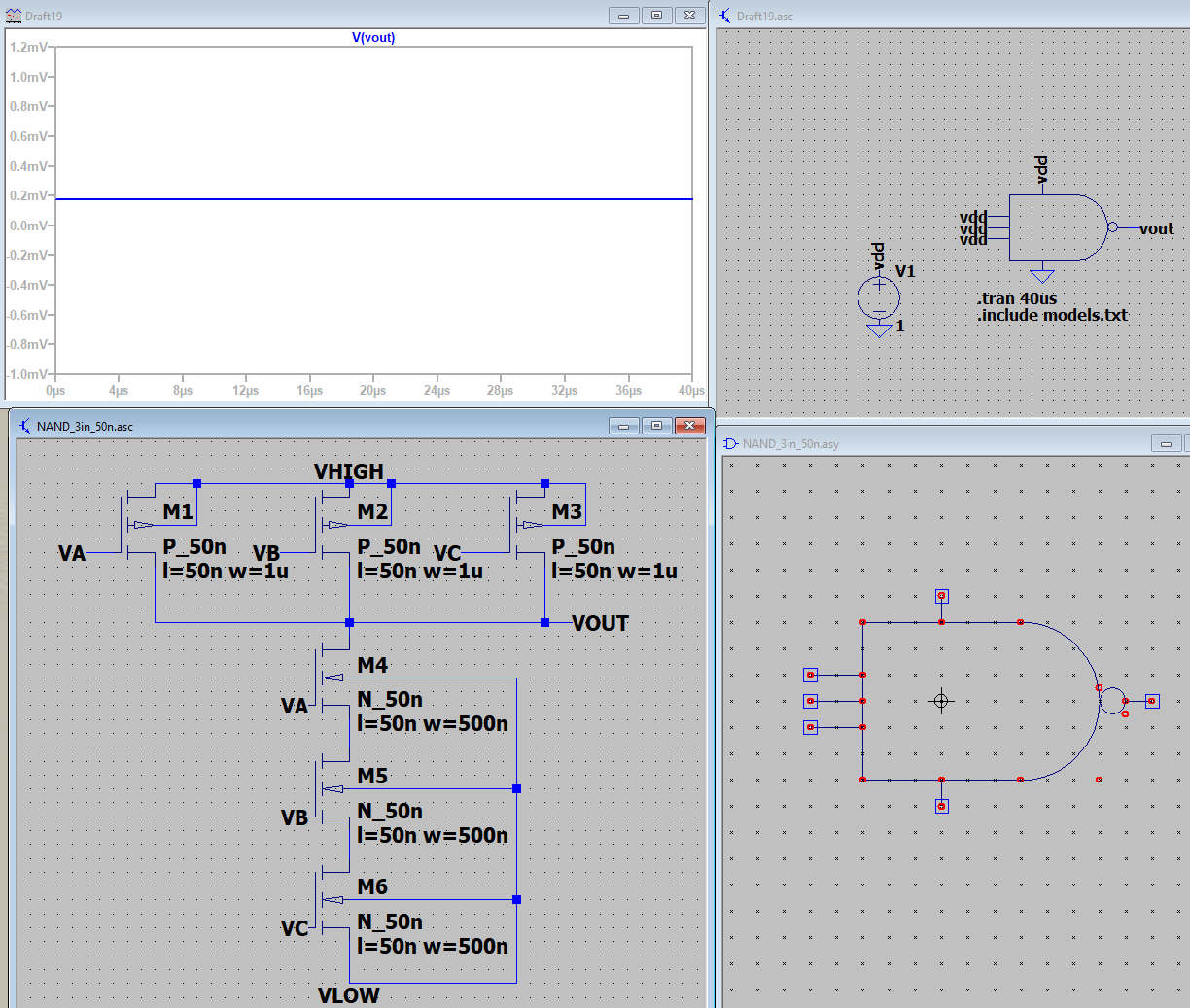

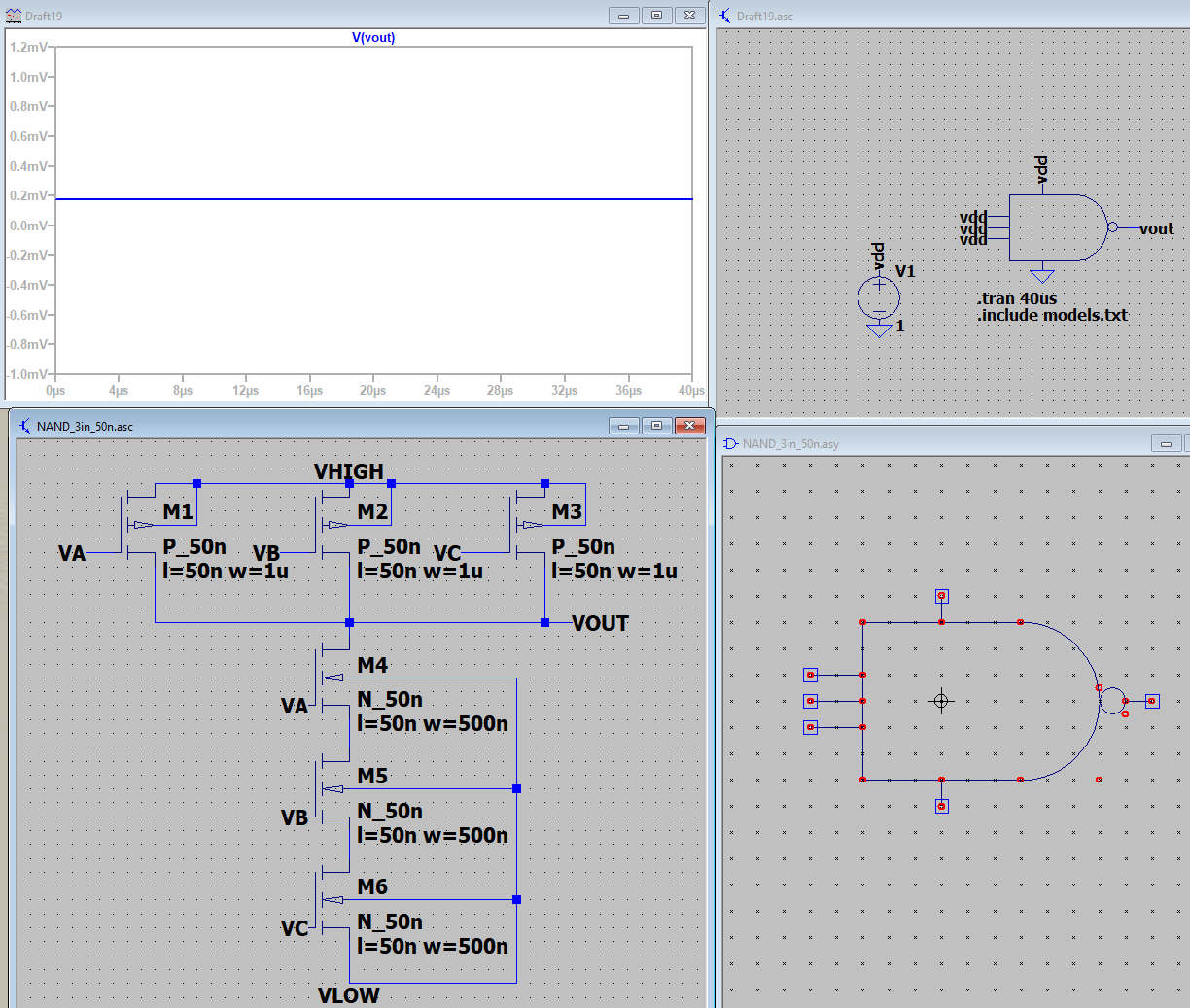

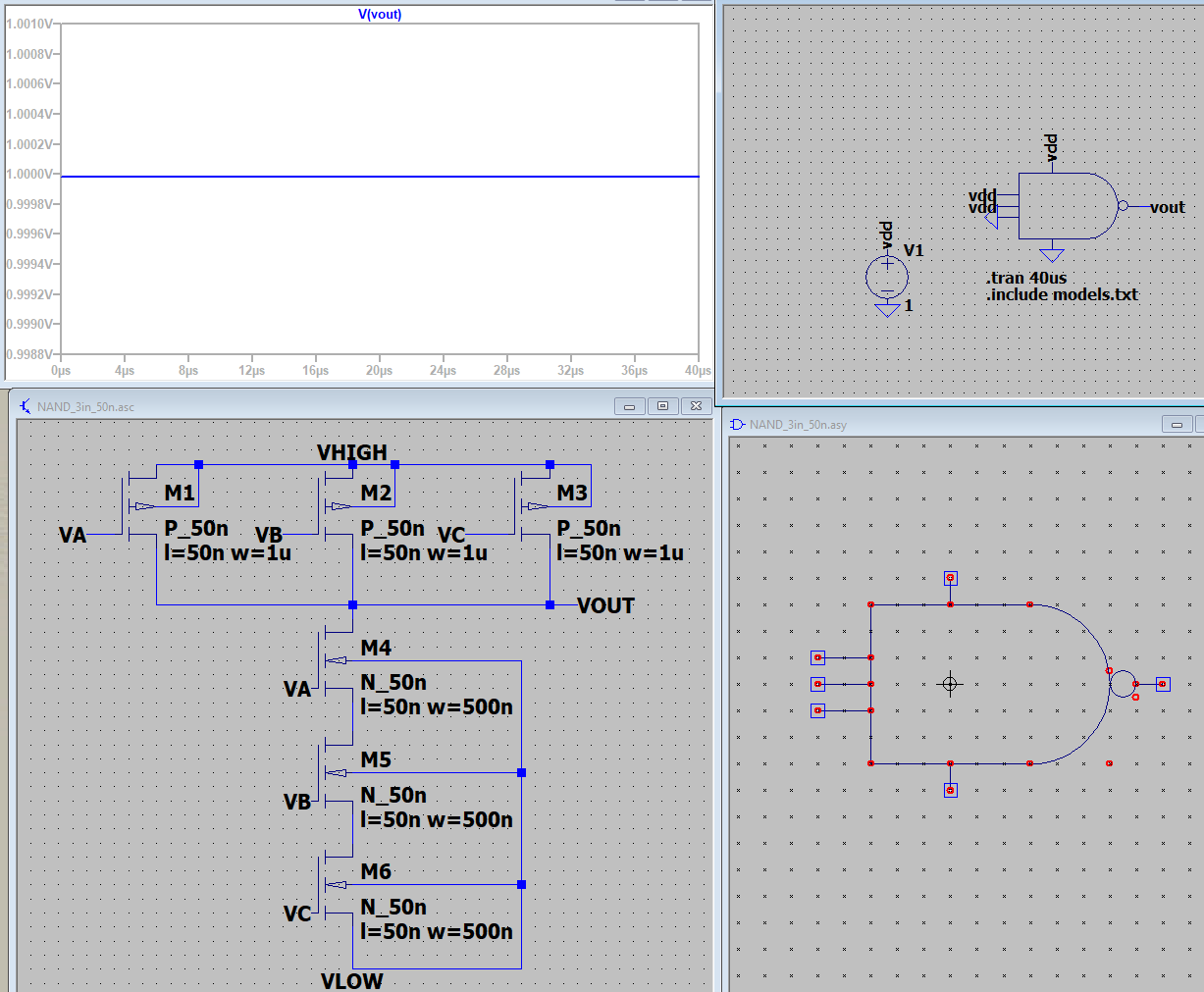

Task 1: 3 input NAND gate

Figure 1. Schematic and simulation of 3input NAND gate using 50n

technology

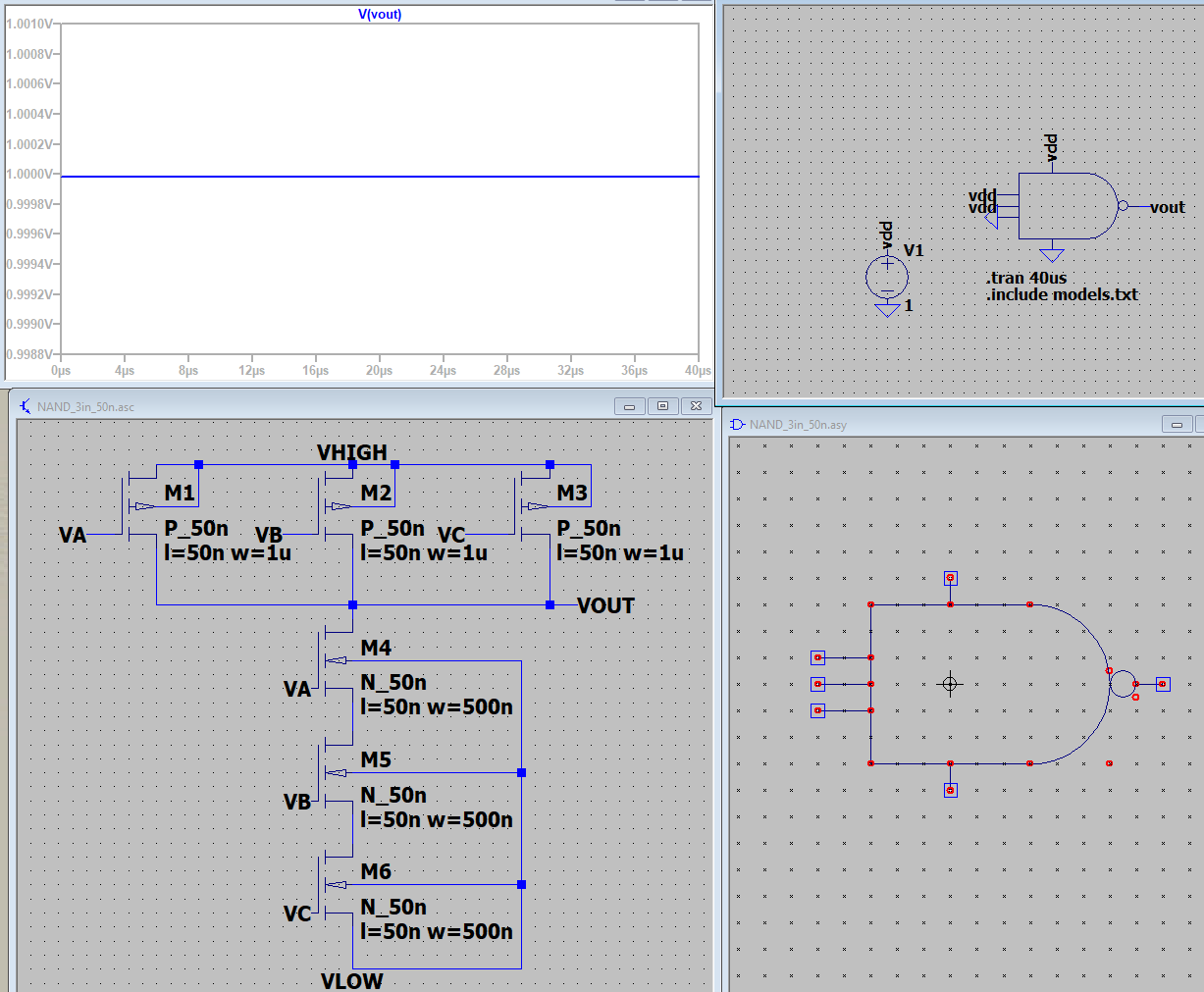

Figure 3. Schematic and simulation of 3input NAND gate using 50n

technology

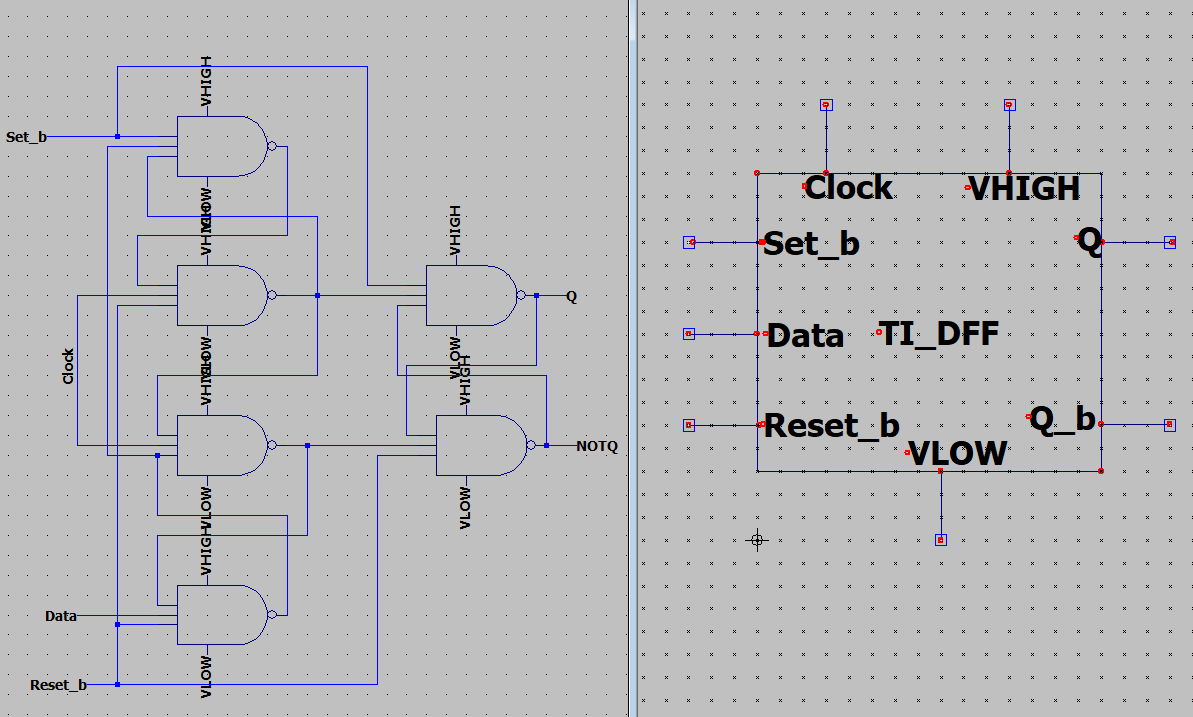

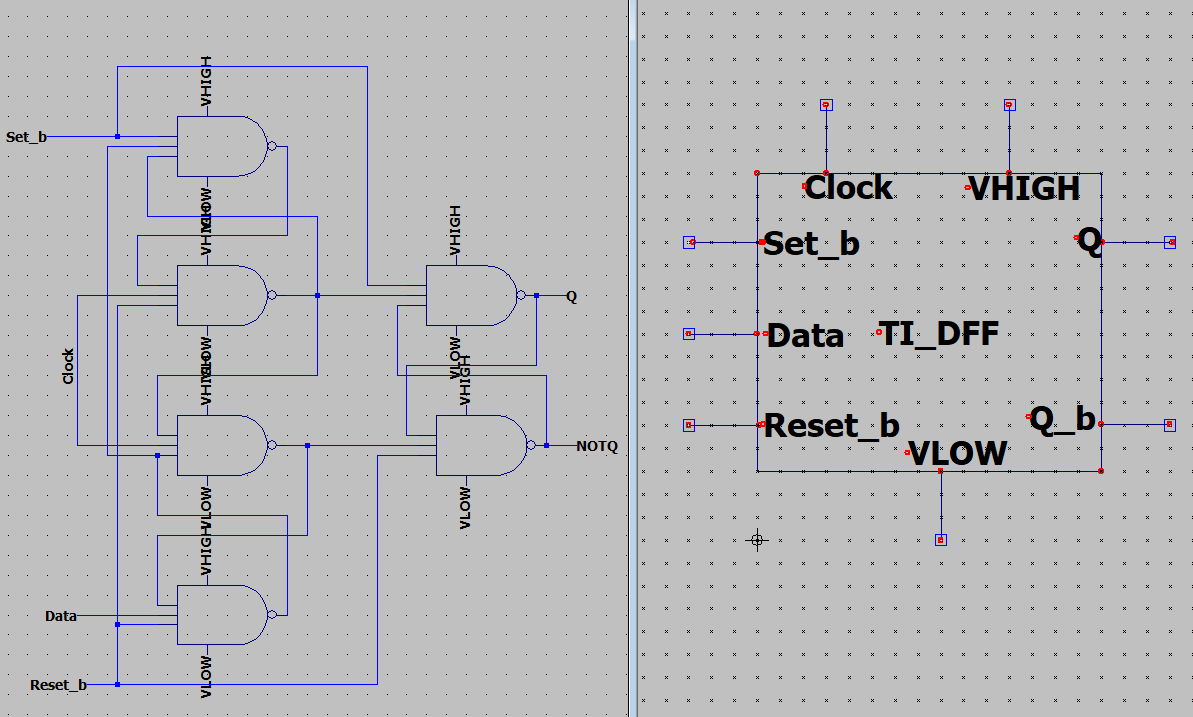

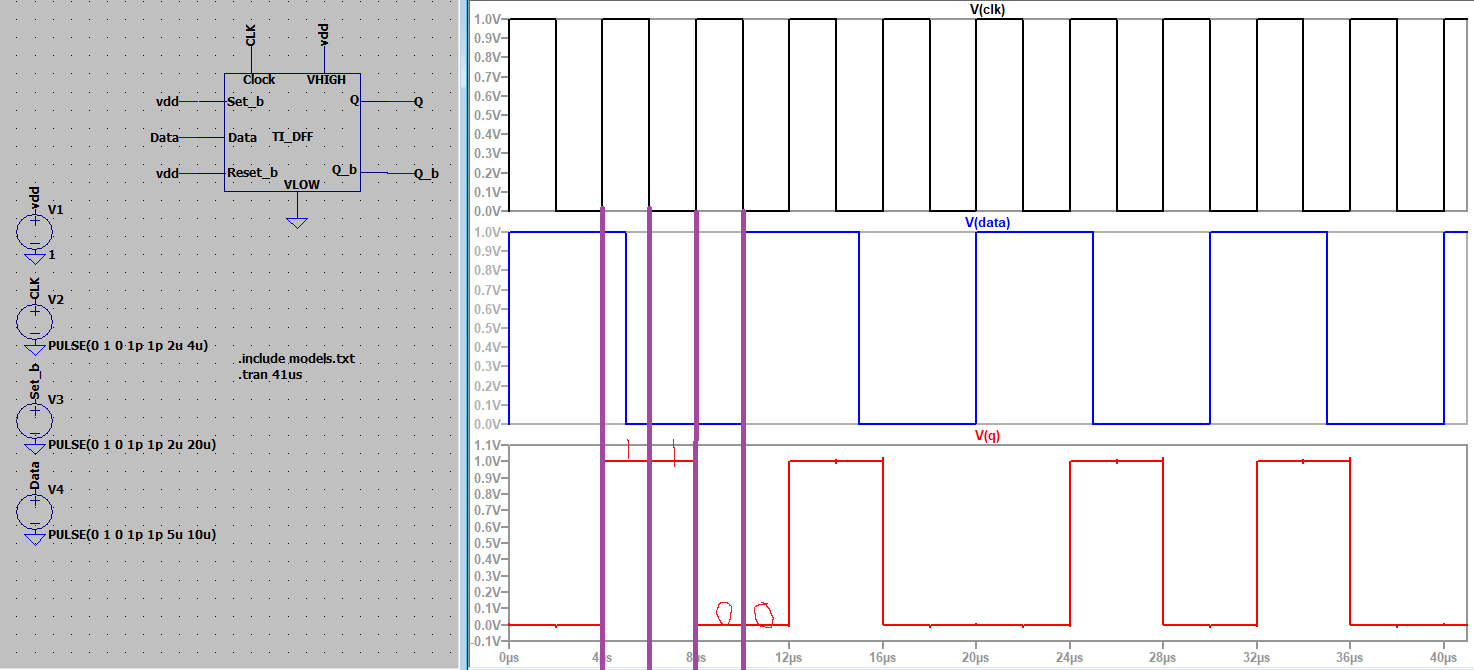

Task 2: TI DFF

Figure 3. Schematic and Symbol of TI DFF

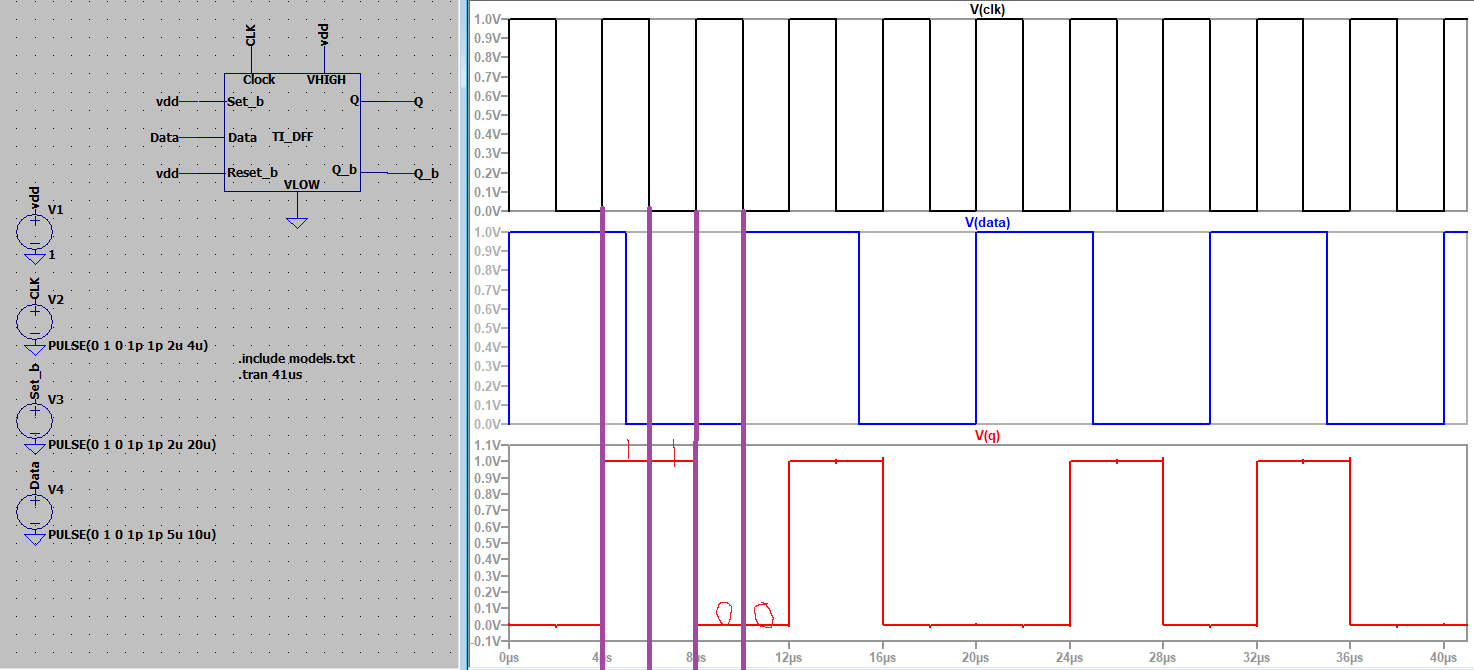

Figure 4. Simulation of clocked DFF.

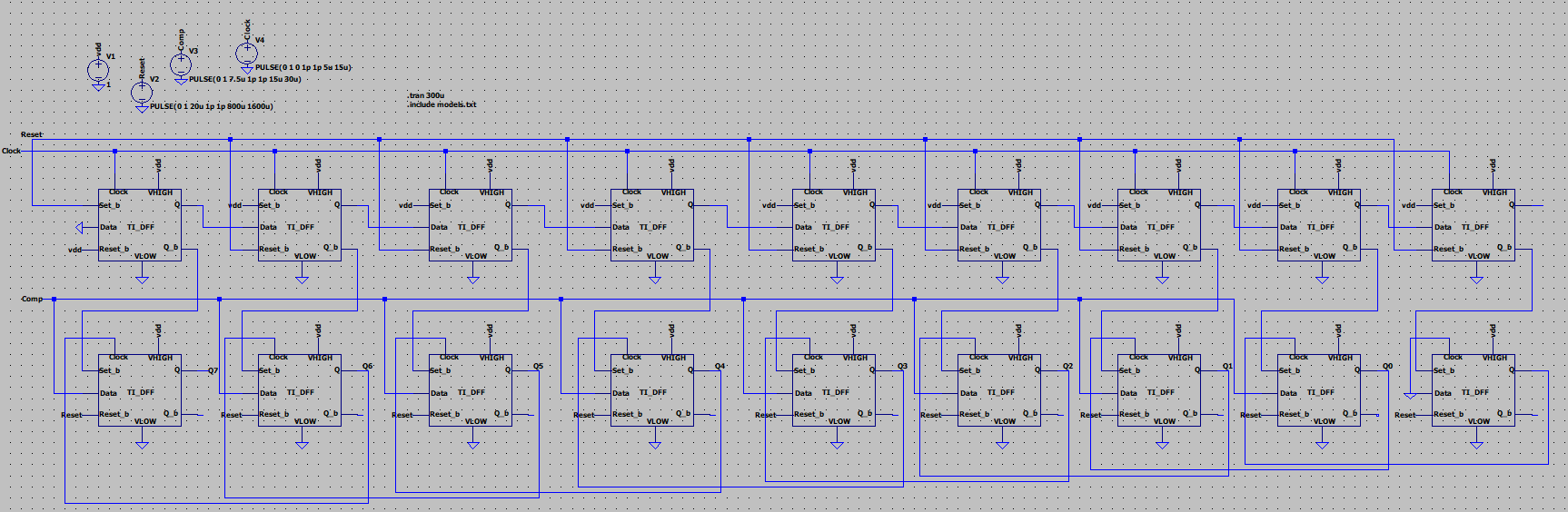

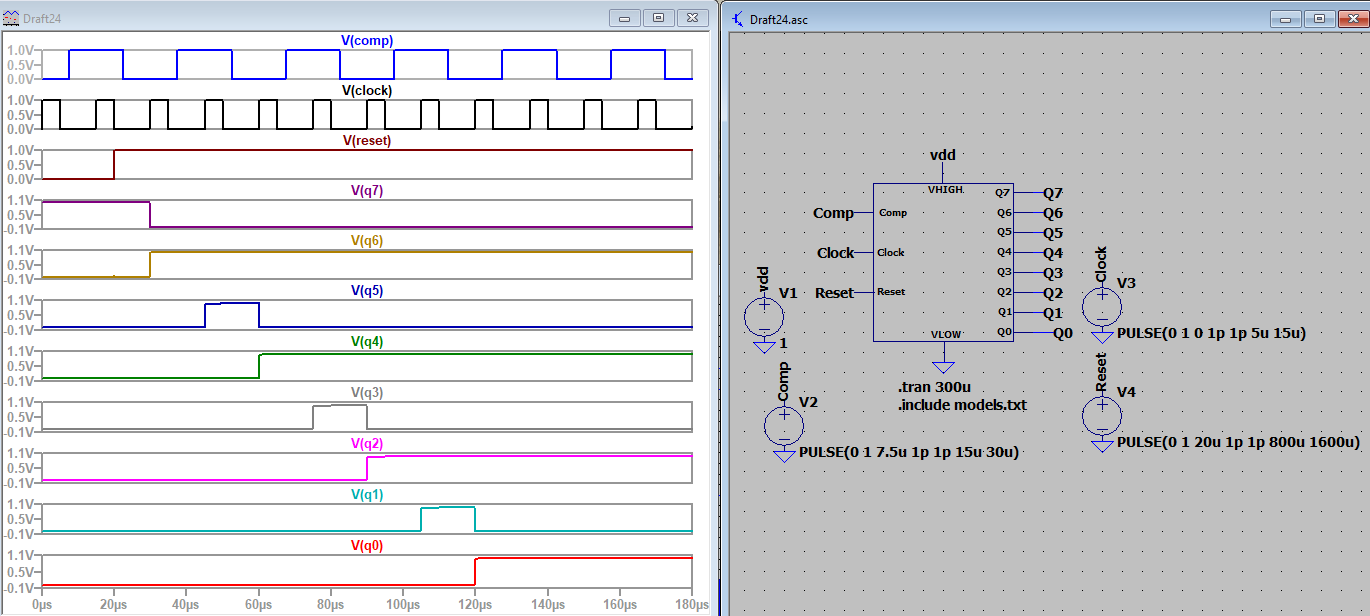

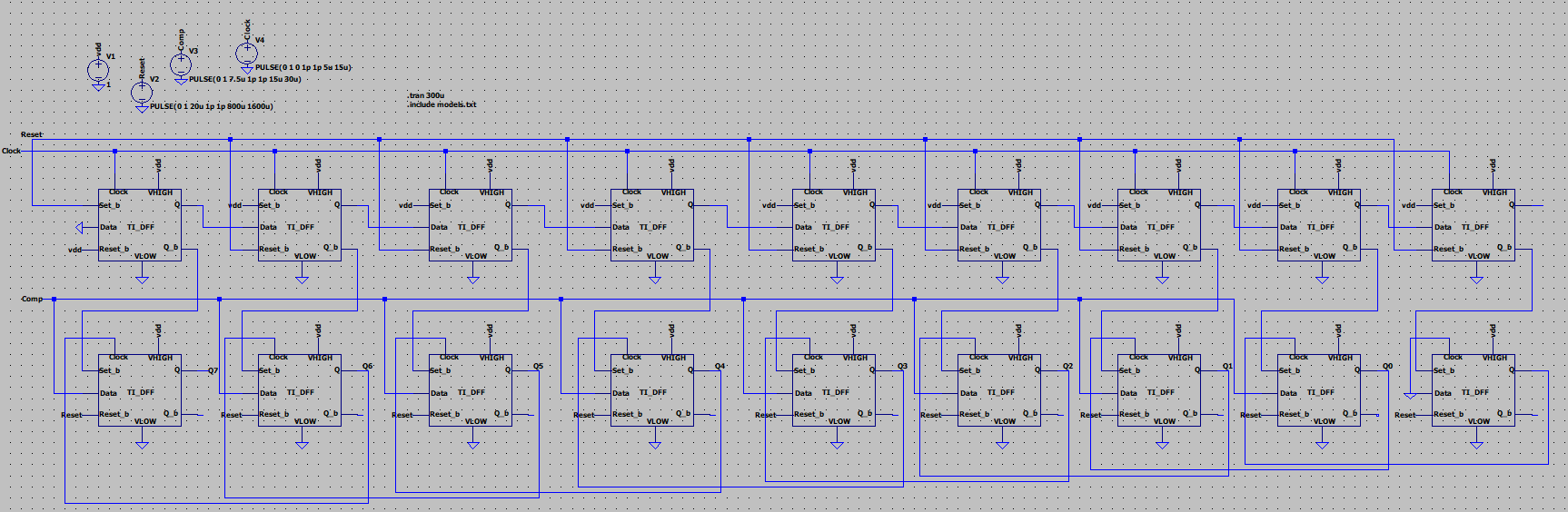

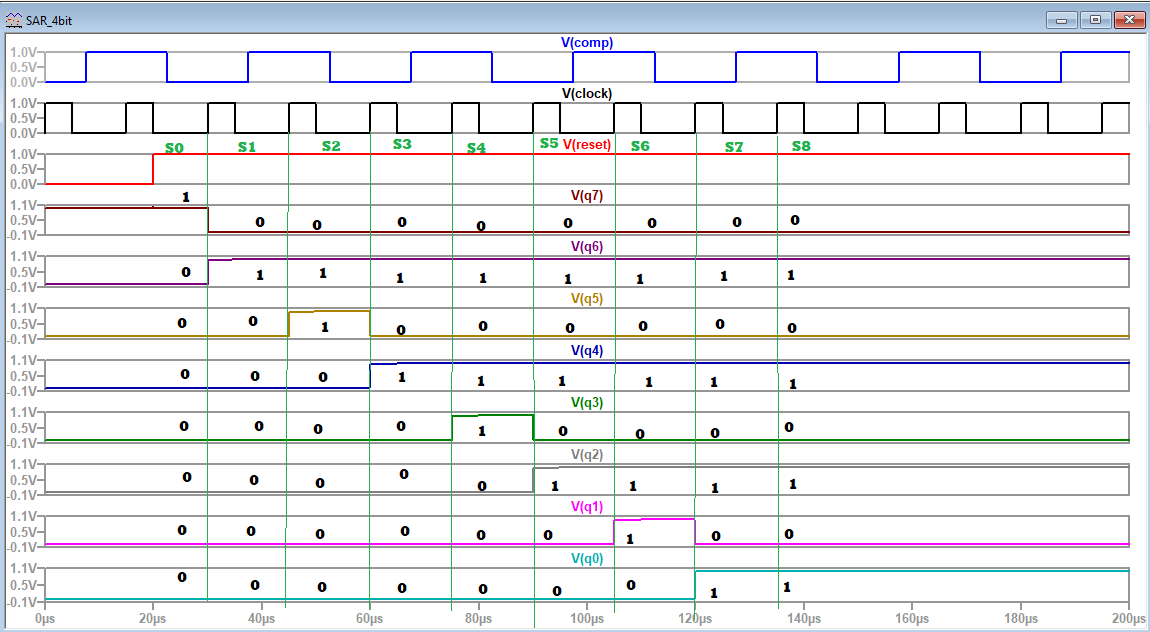

Task 3: 8-bit SAR

Figure 5. Schematic of 8-bit SAR.

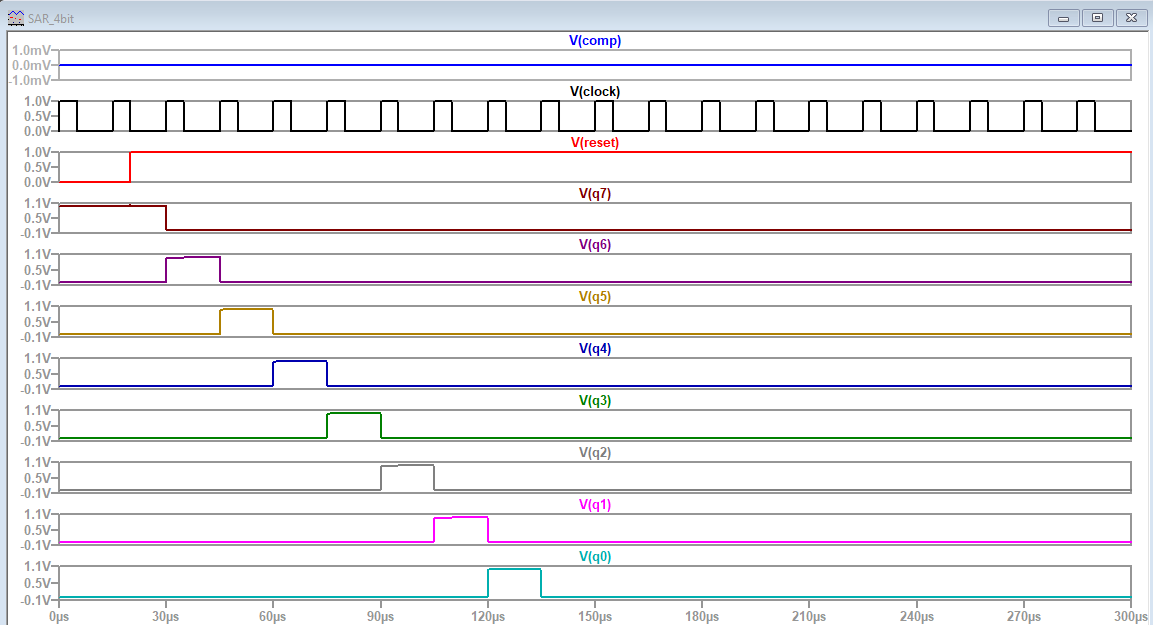

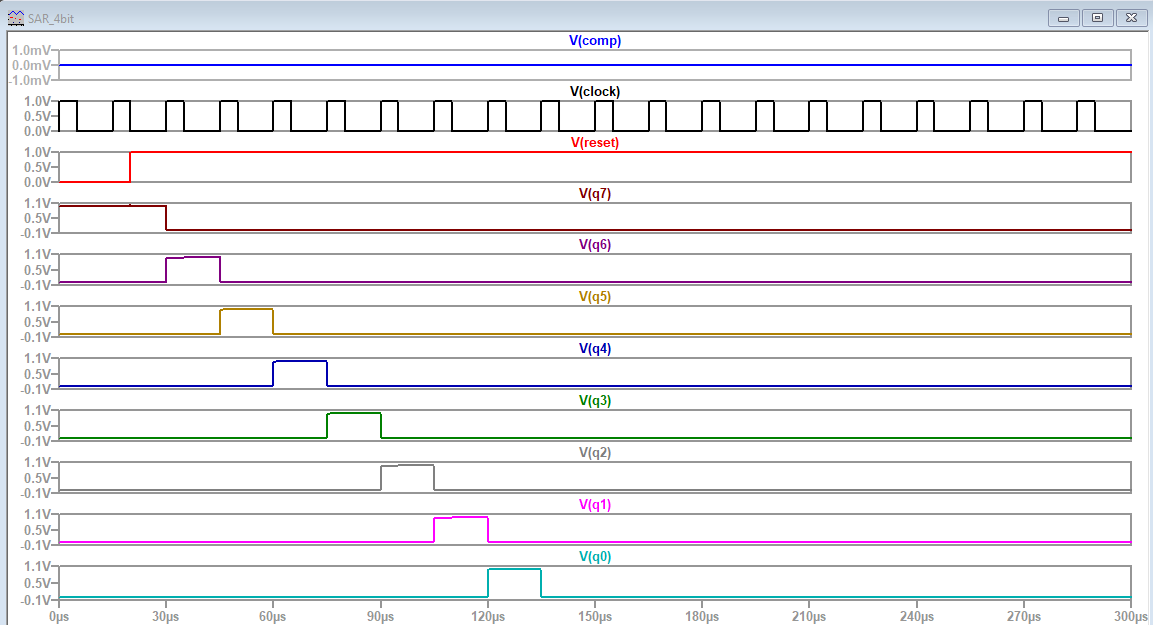

Figure 6. Simulation of SAR with COMP set to zero. This shows that the

shift register is working properly.

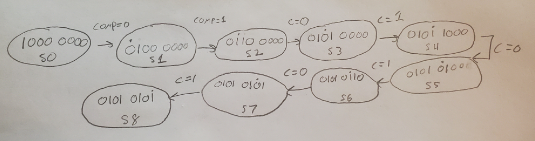

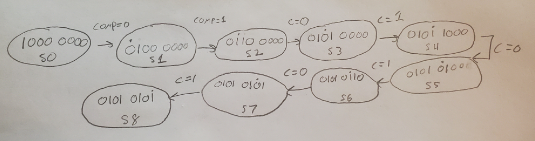

Figure 7. Hand state machine of figure 5. Used to verify functionality of

SAR.

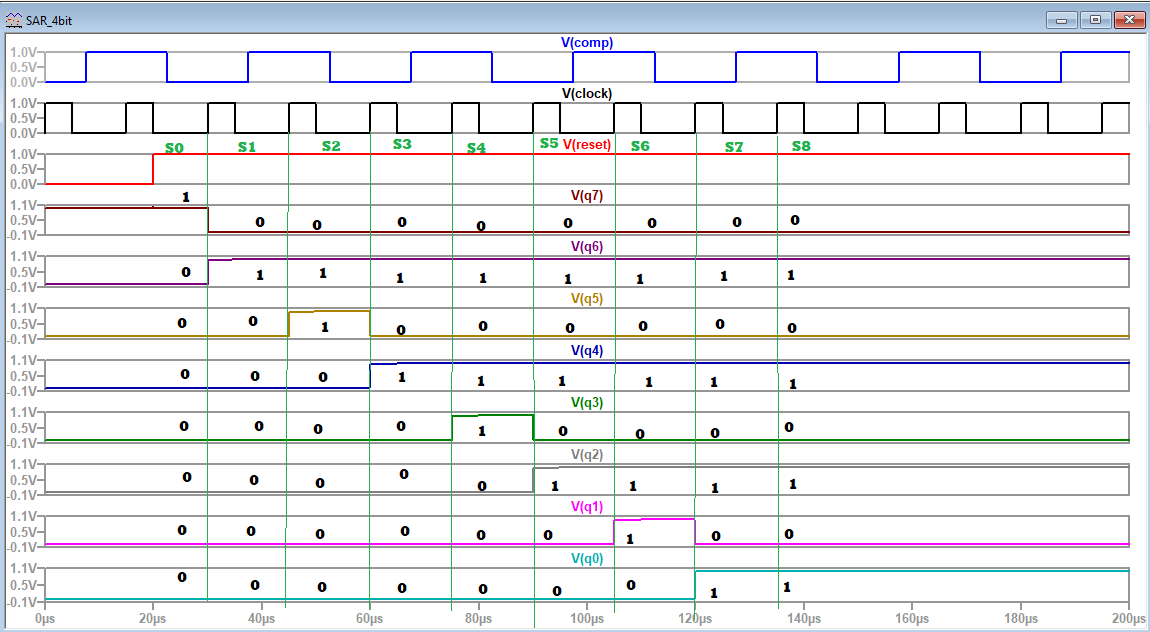

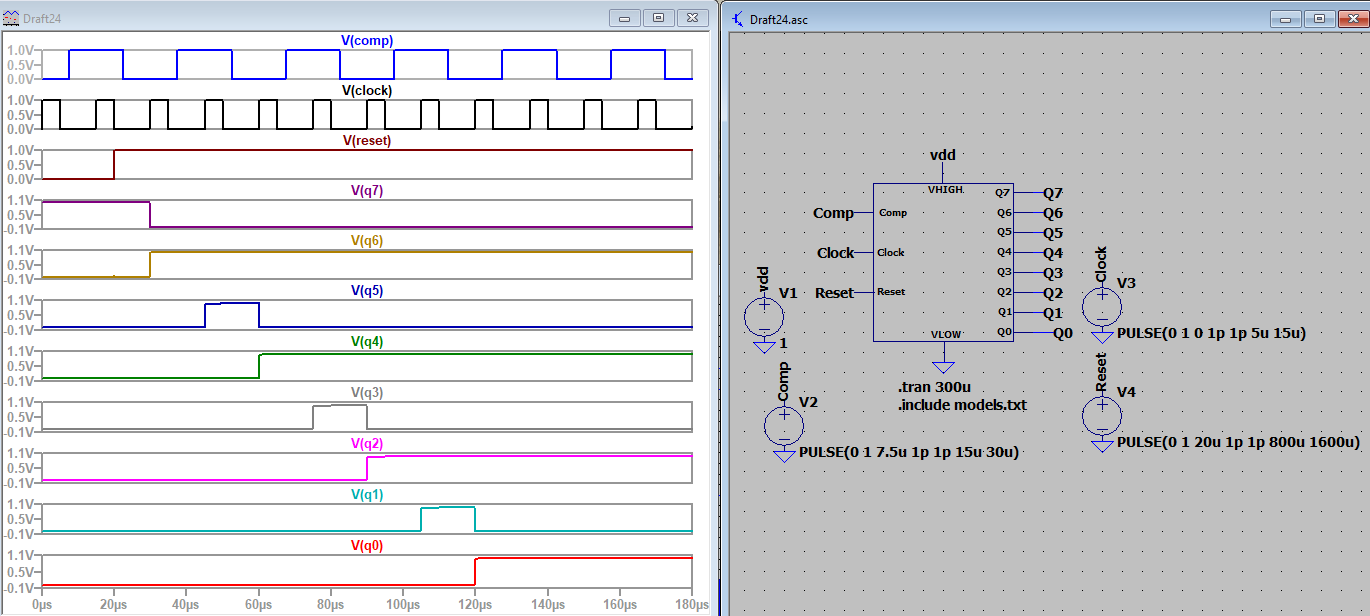

Figure 8. SAR Simulation of figure 5. Output at each state matches

figure 7. Functionality verified

Figure 9. SAR 8-bit symbol created and verified. Outputs match that of

figure 8.

Discussion

This project was fun to tackle as it startes from gate level and

travels thorugh levels of abstraction. Starting from the NAND gate,

simulation was great for catching problems before they arose. Using a

hand state machine for the SAR was useful for verifying functionality.

Doing a layout of this SAR would be taxing, but I'm sure it would be

rewarding 2 times over.

References

[1] https://www.ee.columbia.edu/%7Ekinget/EE6350_S16/03_ADC_Dhruv_Gurkaran_Shikhar/index.html