Lab 3 R-2R Ladder V2 DAC

Jesse Duran

Spring 2021

ENGR 338

Introduction:

During this lab we expanded on our previous R-2R DAC by completeing the

layout. We were shown the benefit of creating subcells for reuse.

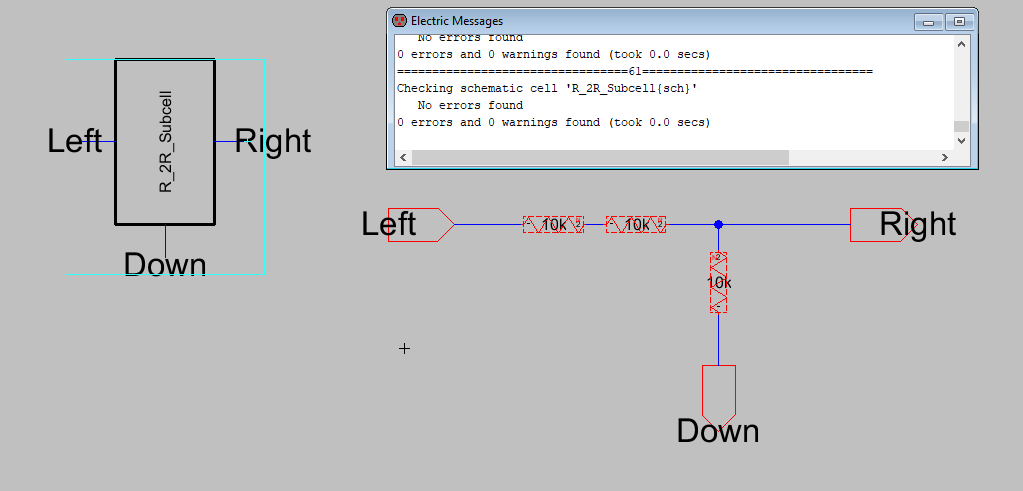

Task 1

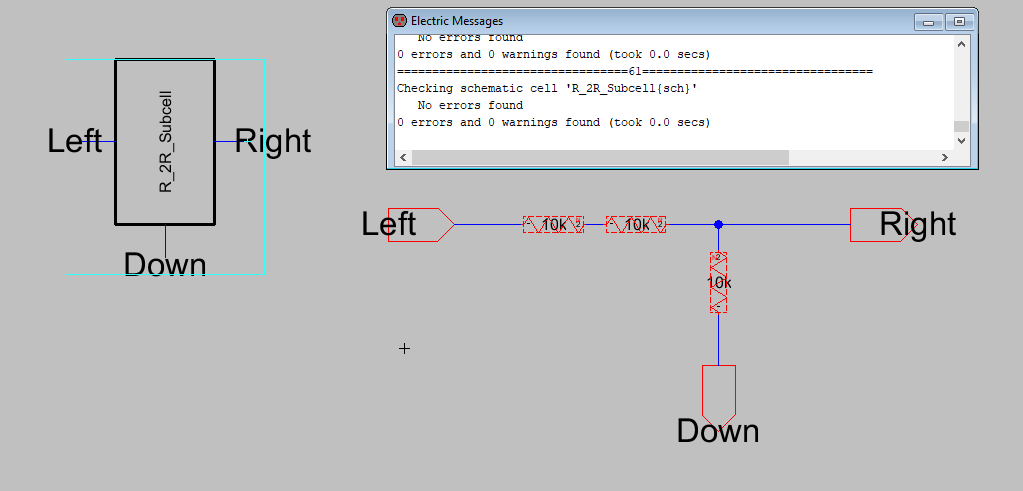

Figure 1. R_2R_Subcell DRC clean. This is the base component to be used to construct the remainder of our ladder.

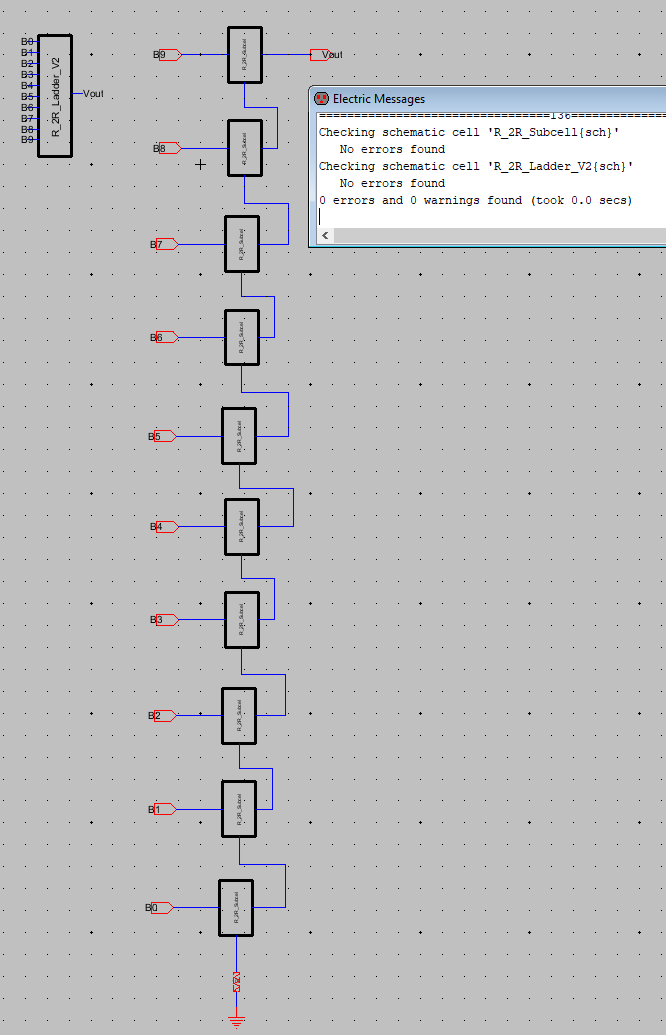

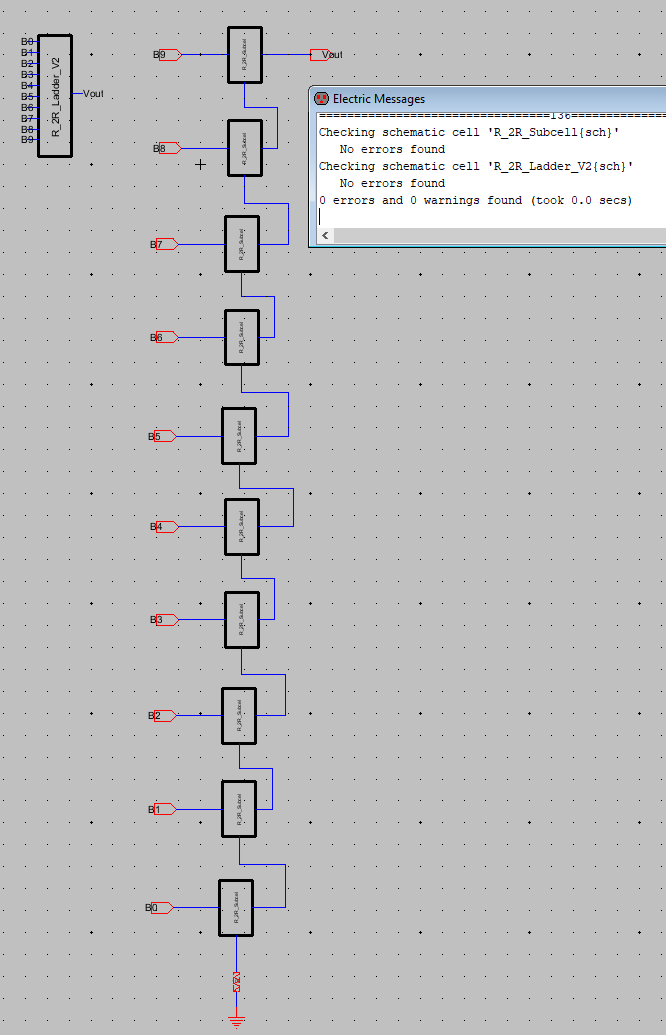

Figure 2. Final schematic of R_2R_ladder_V2. DRC clean. This is composed of our subcells.

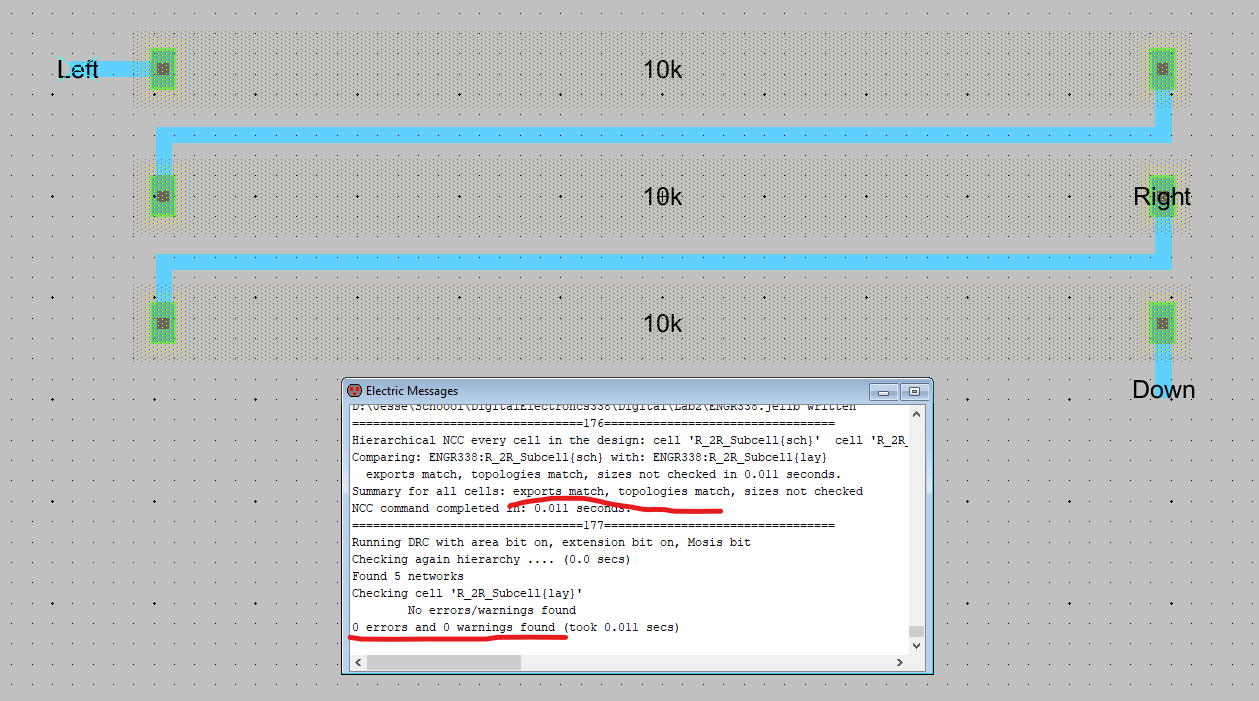

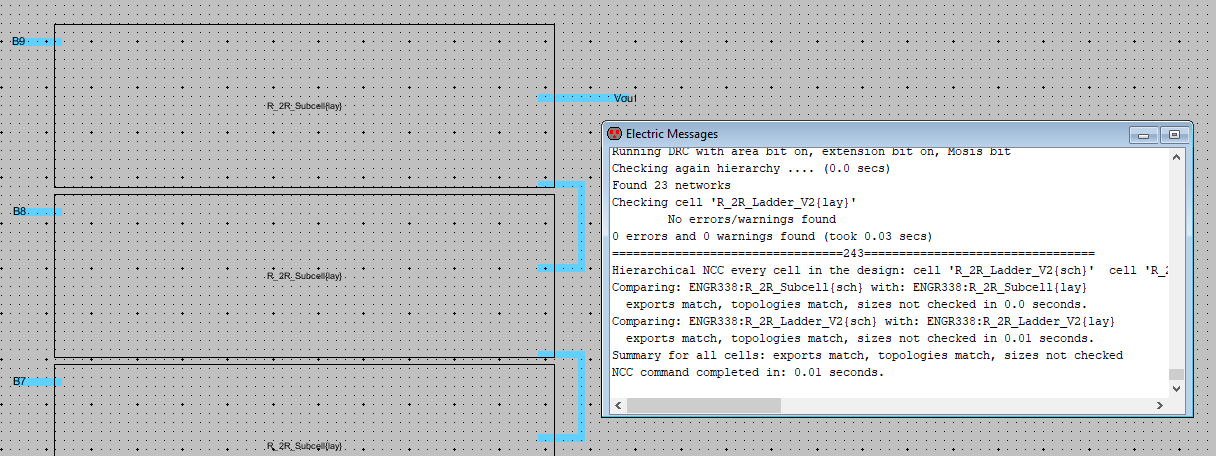

Task 2

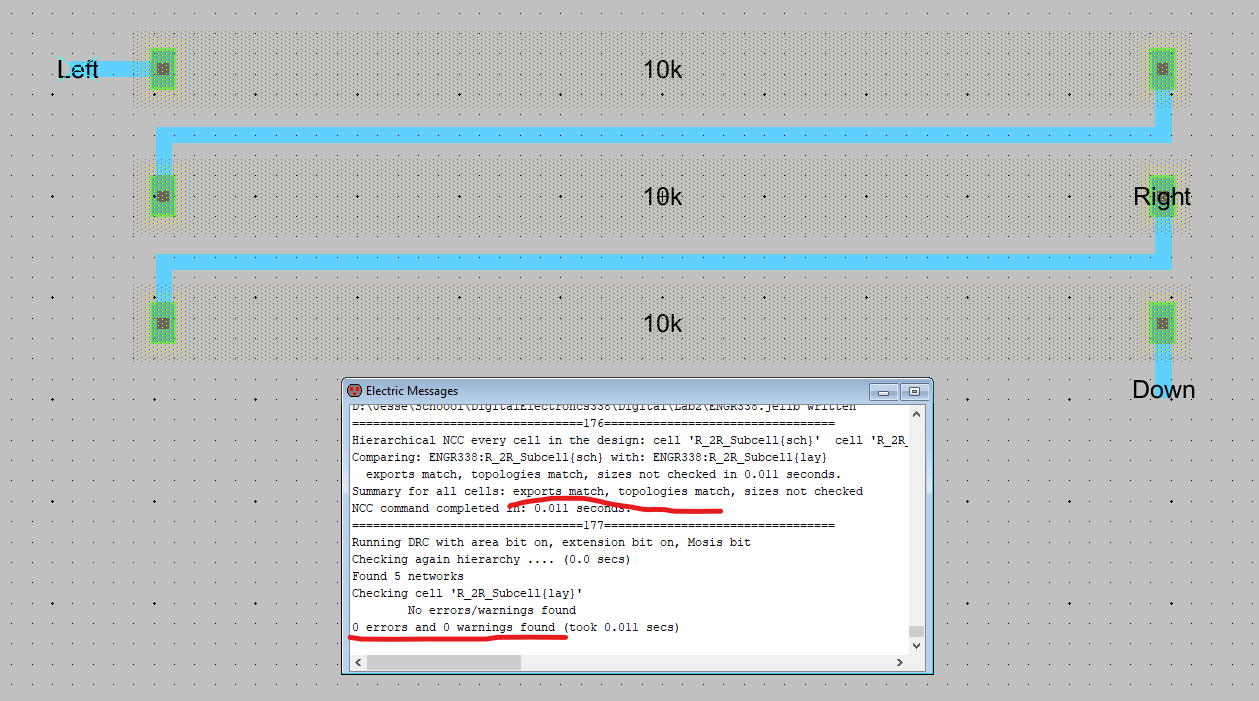

Figure 3. R_2R_ladder_Subcell layout completed. Same circuit as our

schematic using NMOS resistors. DRC and NCC clean. NCC checks that the

schemaic and layout connections match.

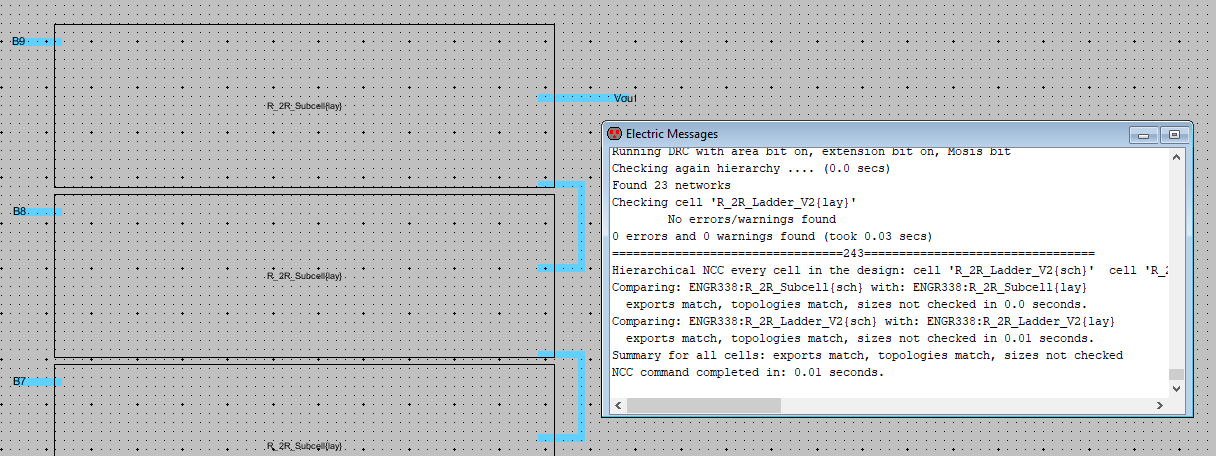

Figure 4. Complete R_2R_Ladder_V2. Composed of the subceslls, the

entire ladder is connected like our schematic. DRC and NCC clean

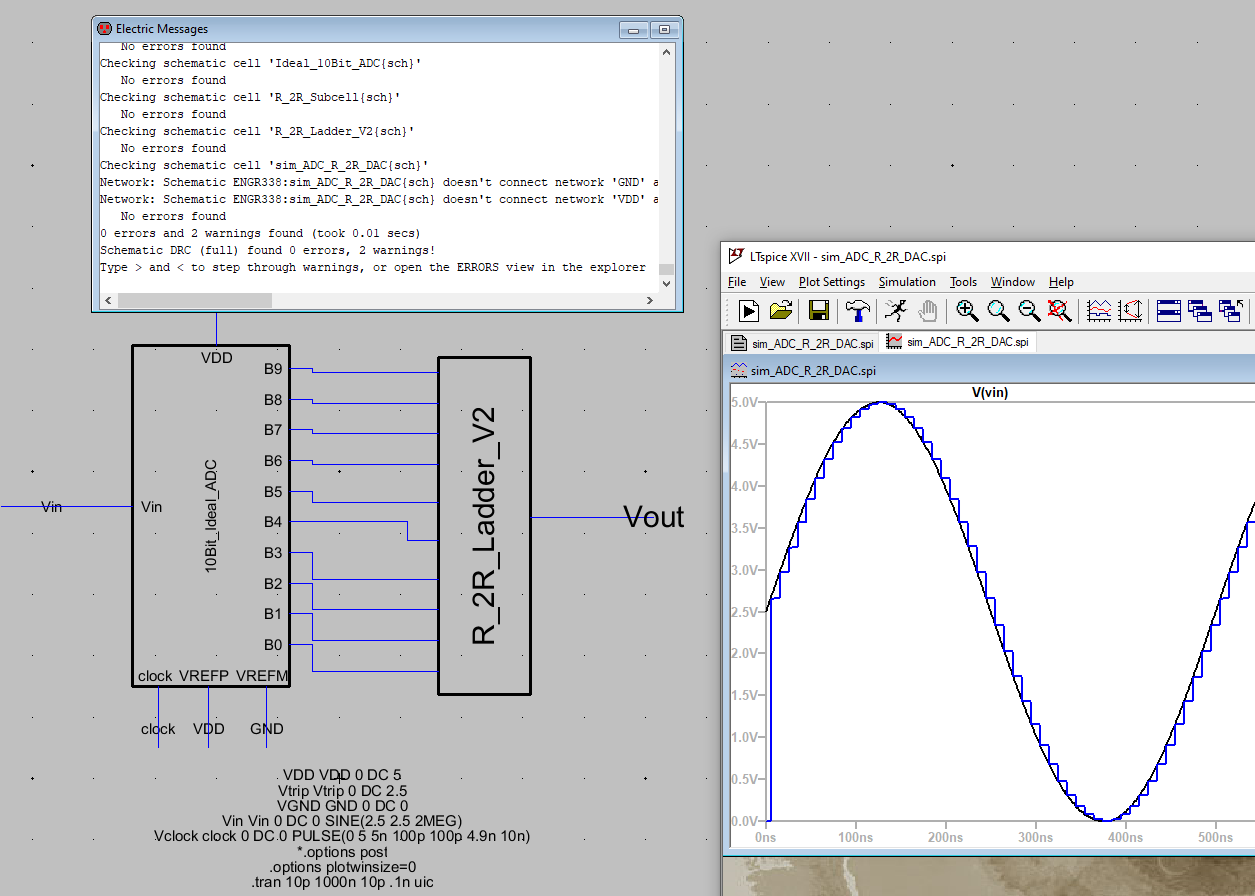

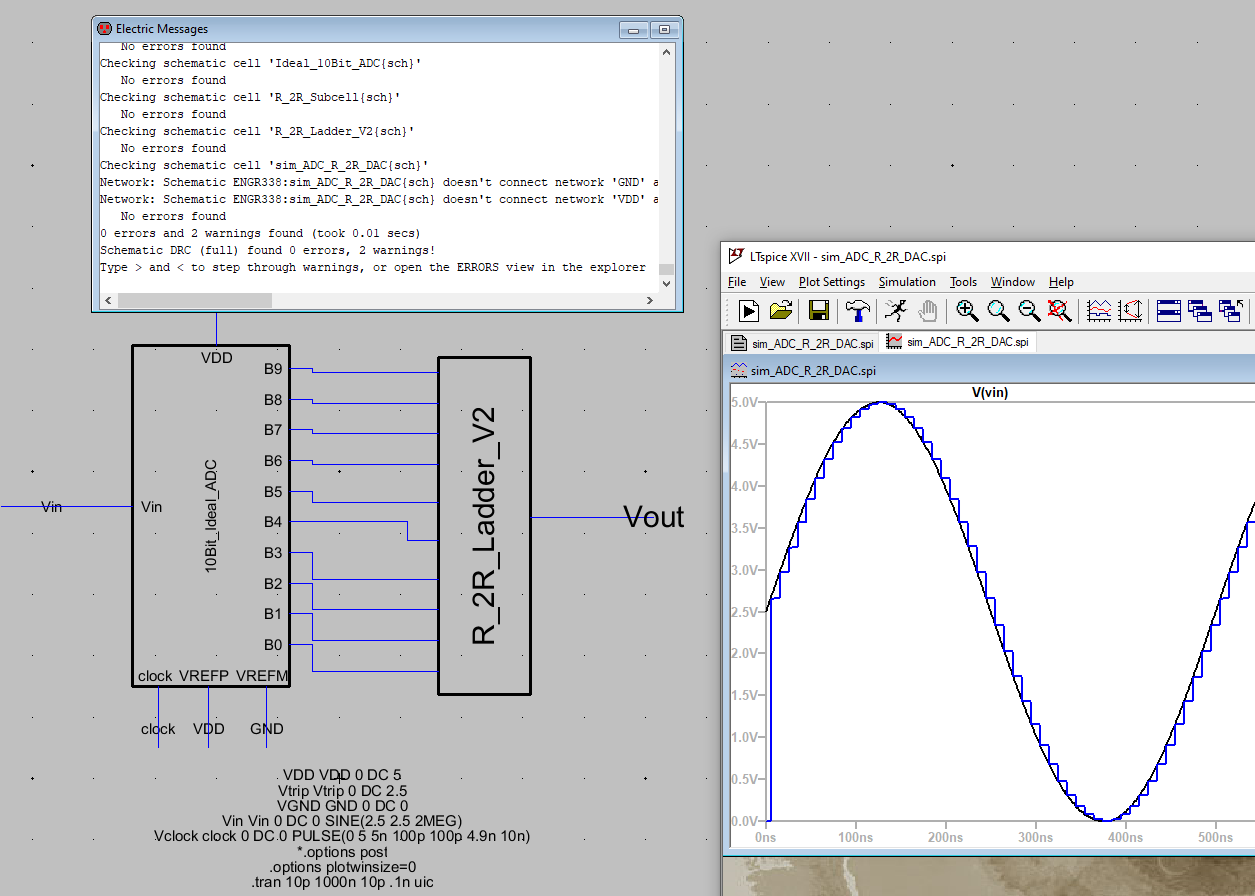

Figure 5. Using the simulation file from Lab 2 we replaced the

R_2R_Ladder with the V2. The spice simulation is as expected. Final DRC

and NCC clean.

Discussion

This lab brought in another level of complexity in the creation of a

R_2R_ladder in the form of the layouts using NMOS. The use of subcells

in the larger component is good to know in order to speed up work and

minmize redundancy.