Lab 1 Superposition, LTSpice, Thevenin's Equivilant Circuit Review

Jesse Duran

Spring 2021

ENGR 338

Introduction:

The purpose of this lab was to re-familiarize us with curcuit analysis

and simulation techniques along with Spice simulation and coding. These

skills will be useful for design considerations in the subsiquent labs.

Task 1:

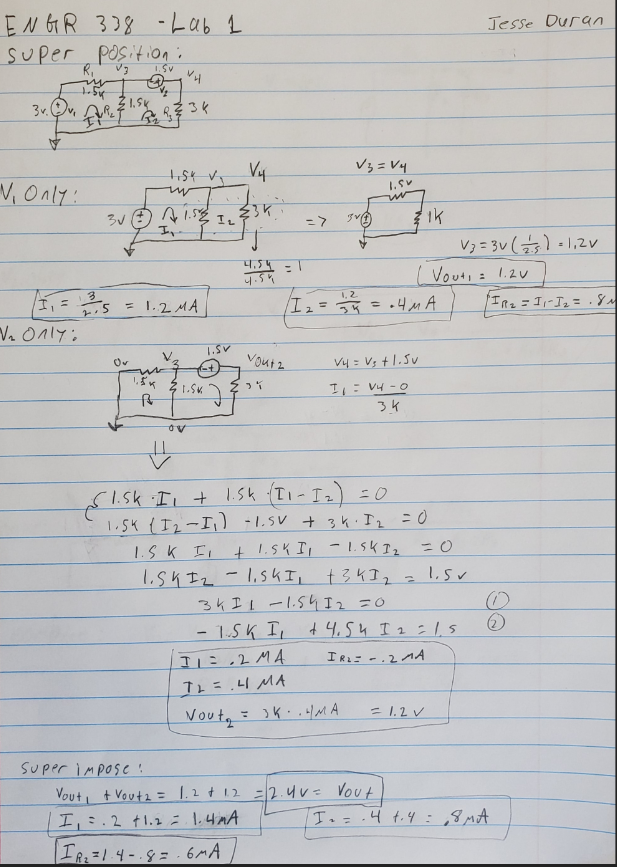

Find all currents and voltages using super position.

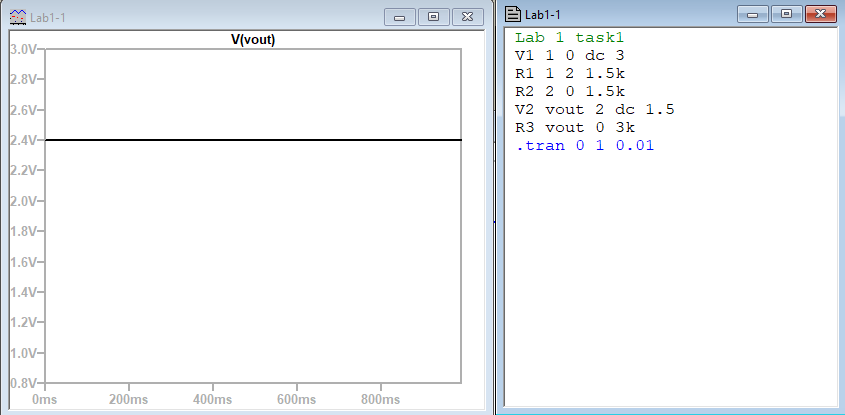

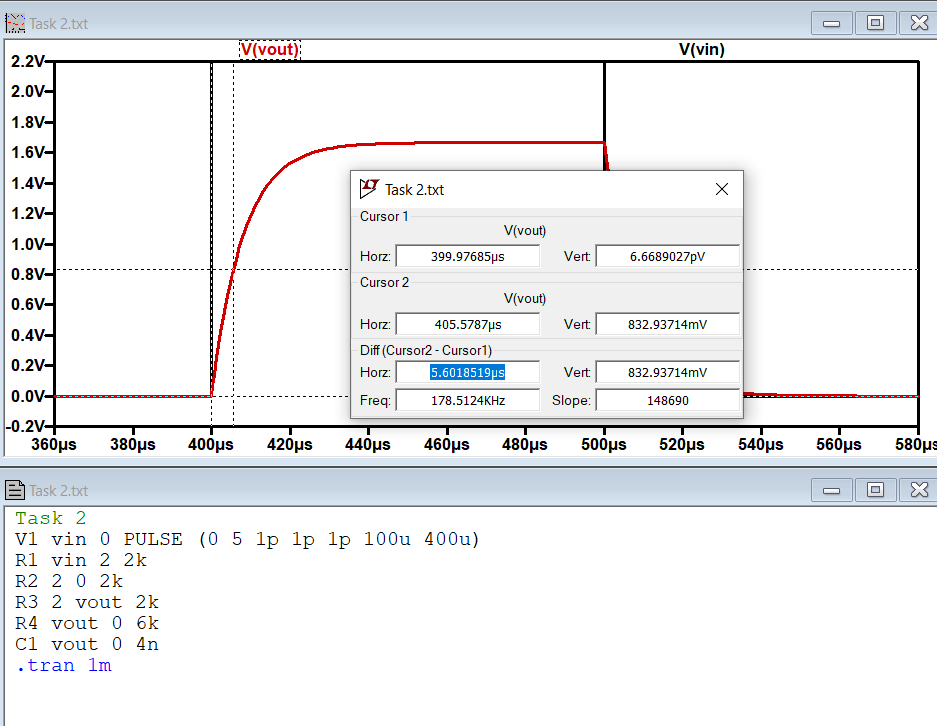

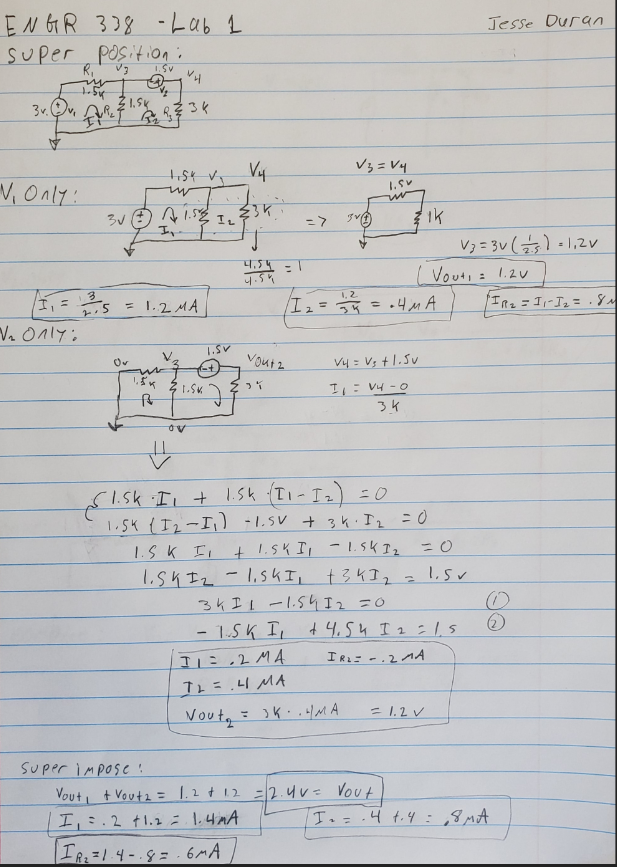

Figure 1. Task 1 hand work

I started out with voltage source 1. First I simplified the circuit to

find Vout1 to be 1.2V. Second I used Ohm's law to find the current

across R3, .8mA. Next from the reduced circuit, ohms law was used to

find the current through R1 to be 1.2mA. Lastly I found the current

across R2 by subracting I2 from I1 to find. .4mA.

V2 only. Removing V1 from the circuit left us with two meshes. Using

mesh current method an simplifying the equations I found I1 to be .2mA,

I2 to be .4mA. IR2 to be -.2mA. Vout was found to be 1.2V

After superimposing the V1only and V2only, Vout was found to be 2.4V, IR1 = 1.4mA, IR3 = .8mA, and IR2 = .6mA

|

V1 Only

|

V2 Only

|

Superimposed

|

Vout

|

1.2V

|

1.2V

|

2.4V

|

I R1

|

1.2 mA

|

.2mA

|

1.4mA

|

IR2

|

.8mA

|

-.2mA

|

.6mA

|

IR3

|

.4mA

|

.4mA

|

.8mA

|

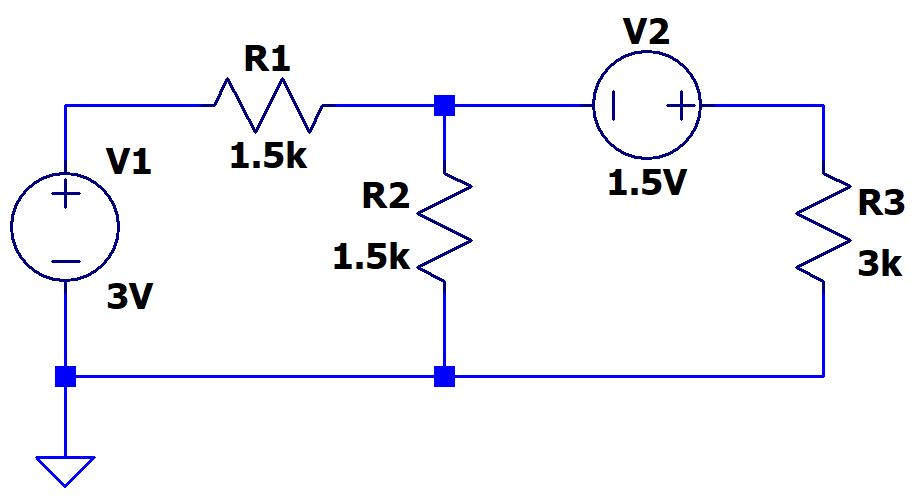

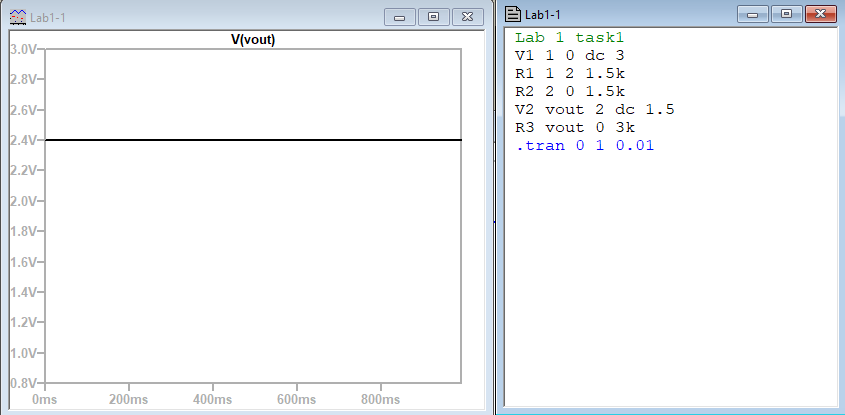

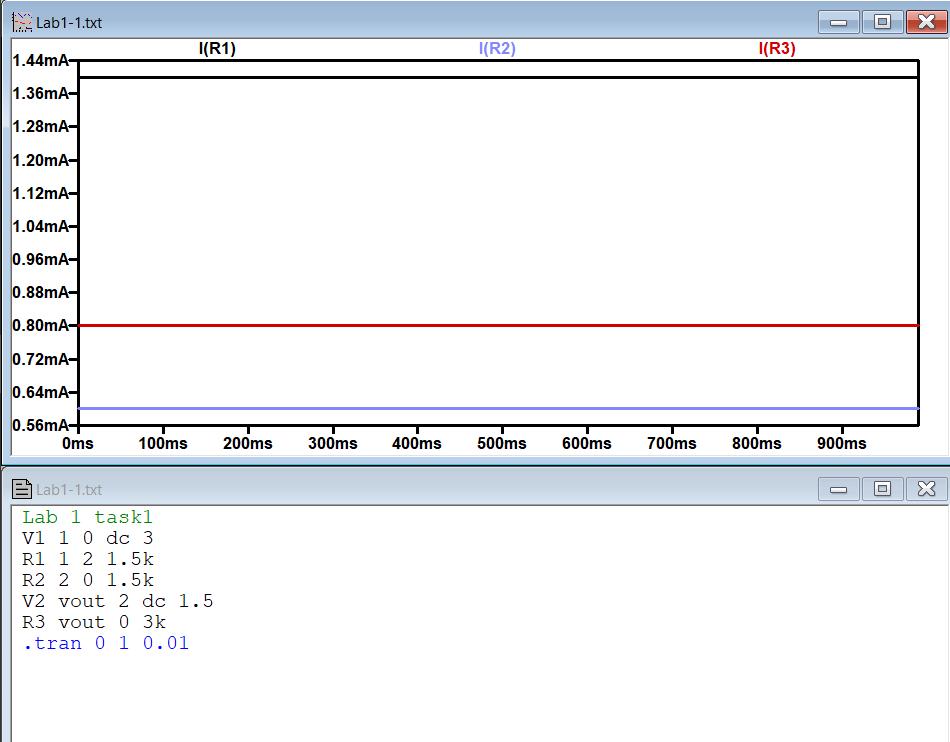

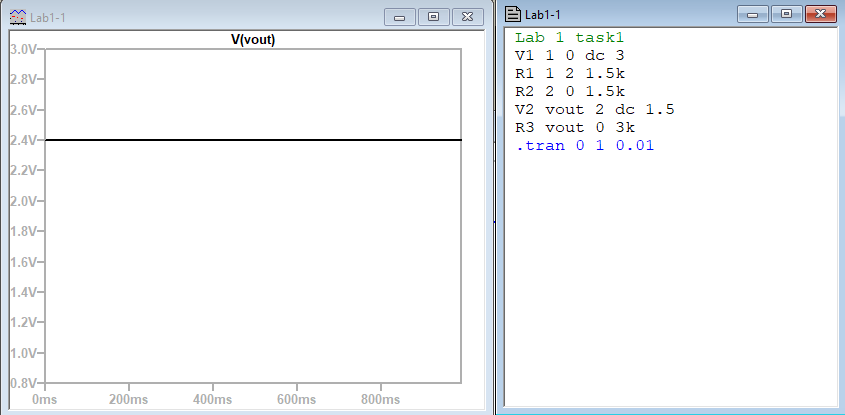

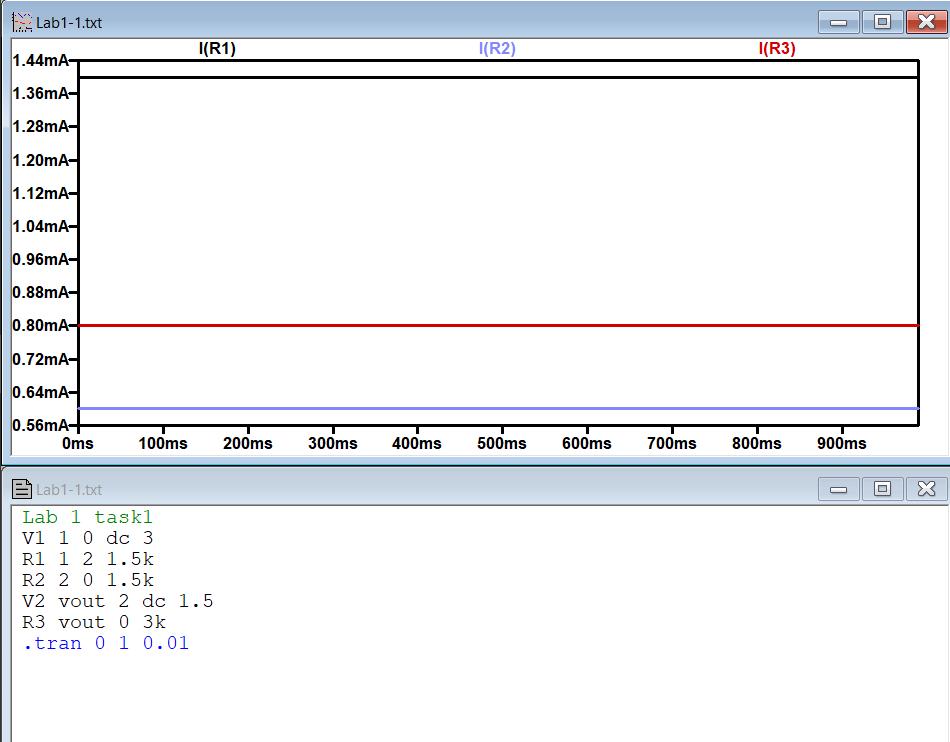

Simulation verification

Figure 2. Spice Code for circuit 1 and Vout verified.

Figure 3. Currents across R1, R2, R3 verifed.

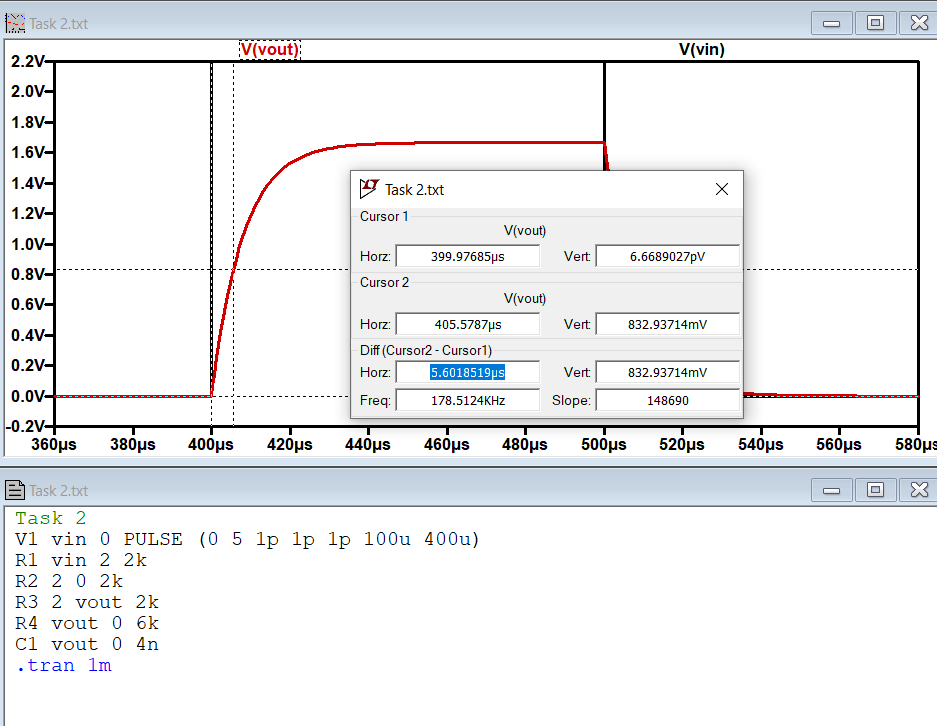

Task 2

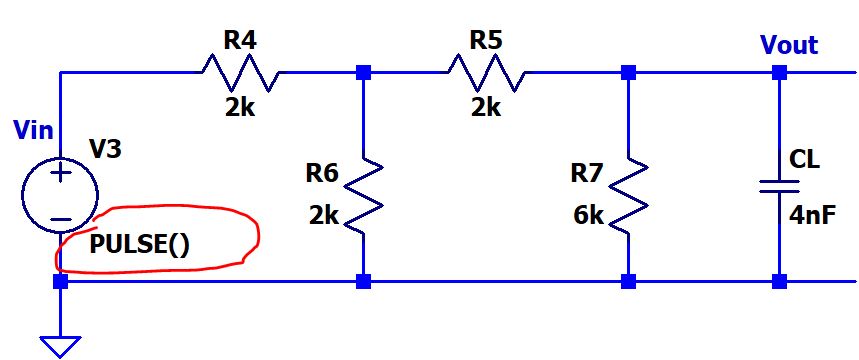

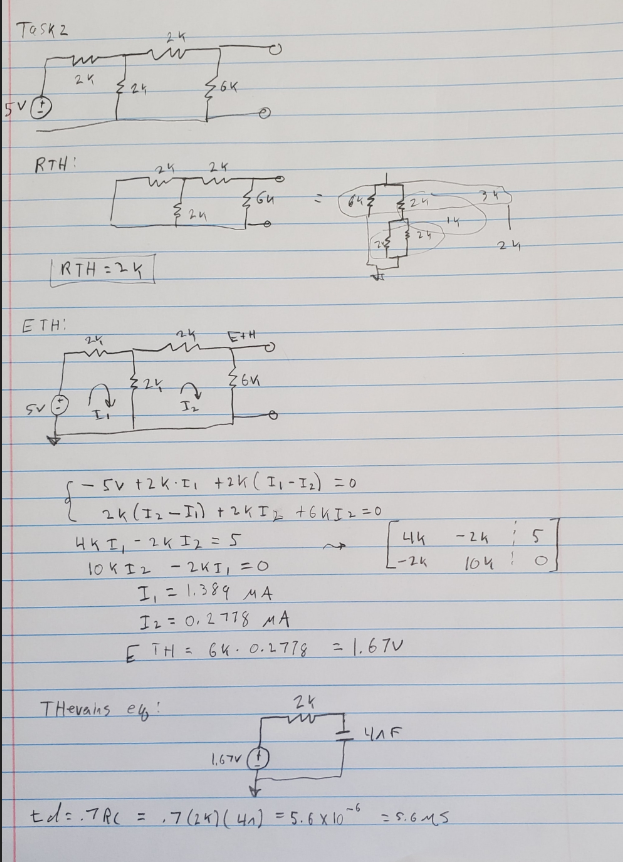

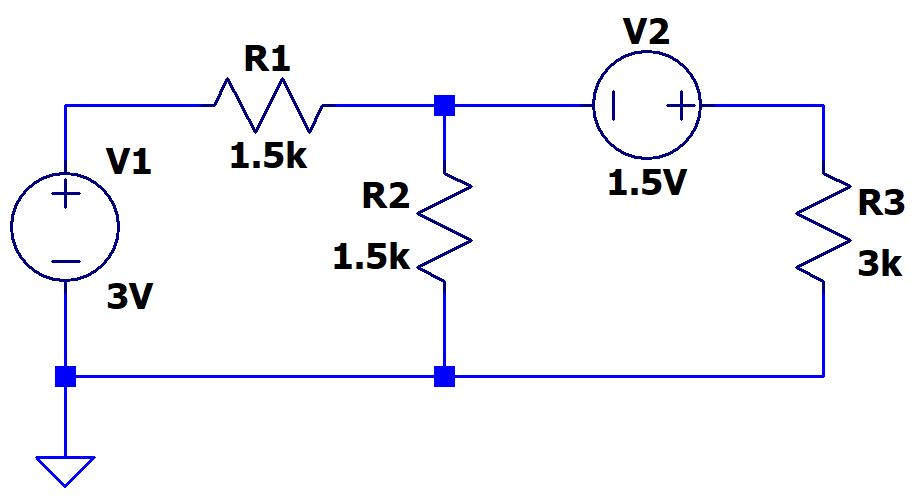

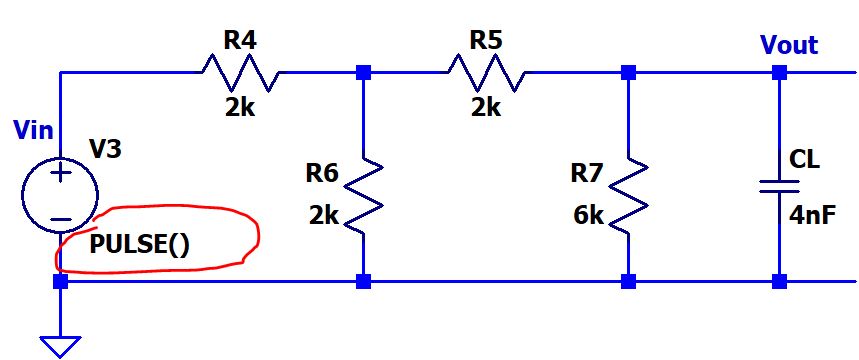

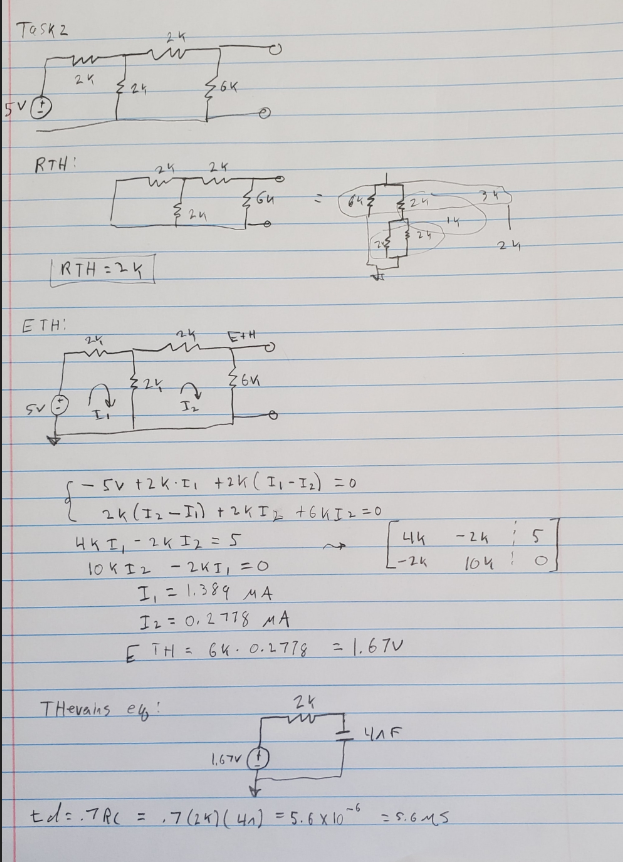

We were tasked with reducing the following circuit to a thevenins equivilant and find the time delay of the circuit.

Figure4. RTH was found to be 2k. ETH was found to be 1.67V. Time delay found to be 5.6us

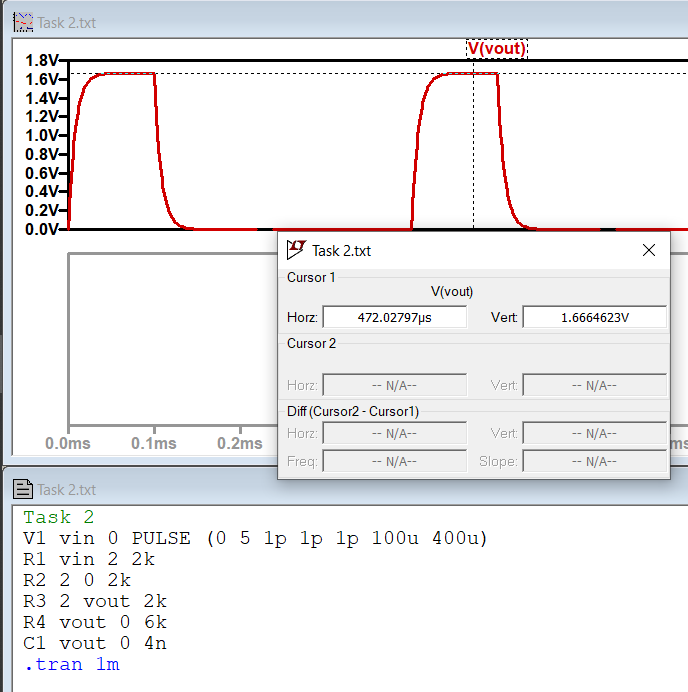

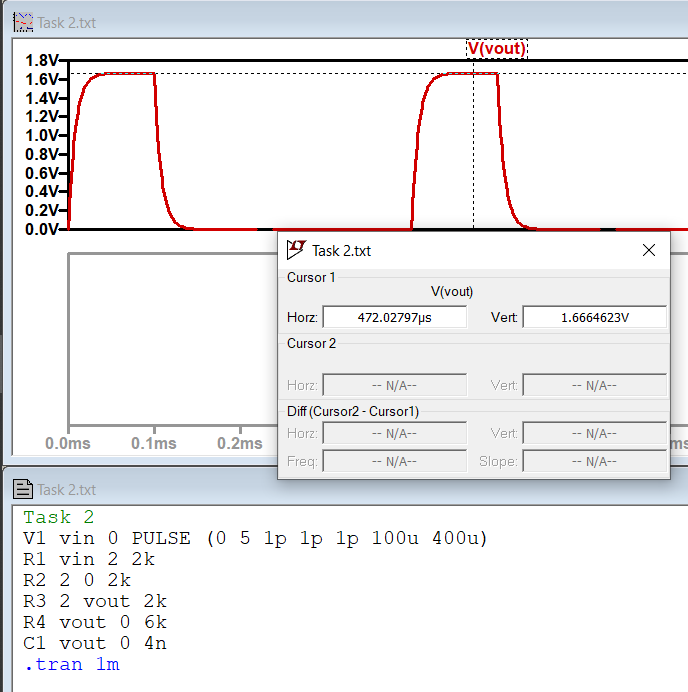

Figure 5. Spice code of circuit 2. ETH Verified.

Figure7. Time delay verified.

Discussion

This lab allowed for review of preivous circuit analysis techniques.

LTSpice is a powerful simulation tool and using a netlist makes one

understand the circuit configuration.