Task 1:

In this task we started by building and simulating the 8-bit MUX.

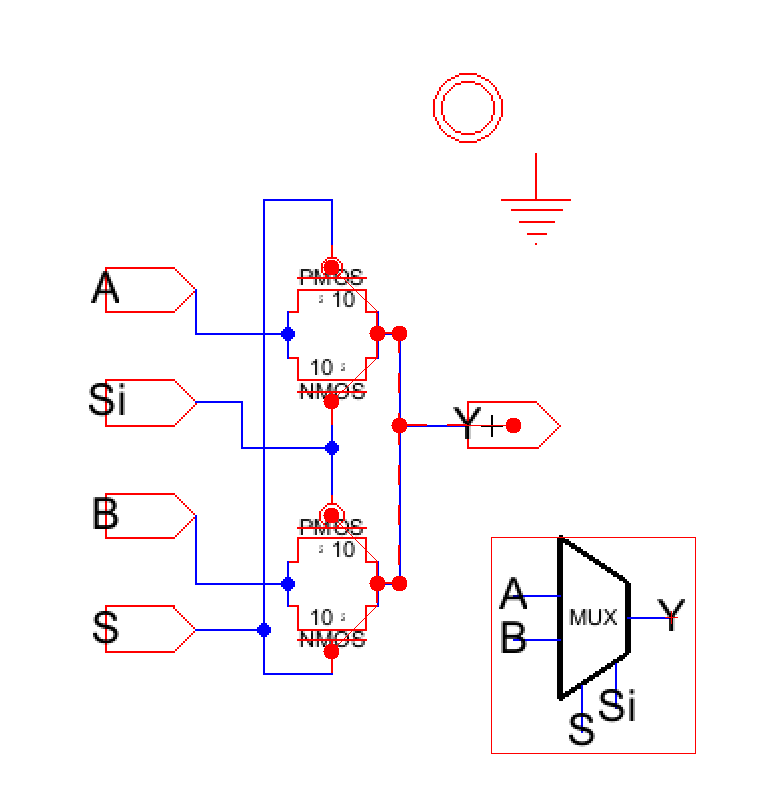

Figure 1: The schematic of the MUX is built in Electric VLSI and it's output is displayed in LT Spice.

Figure 2: The schematic is then tested in LT Spice to verify functionality.

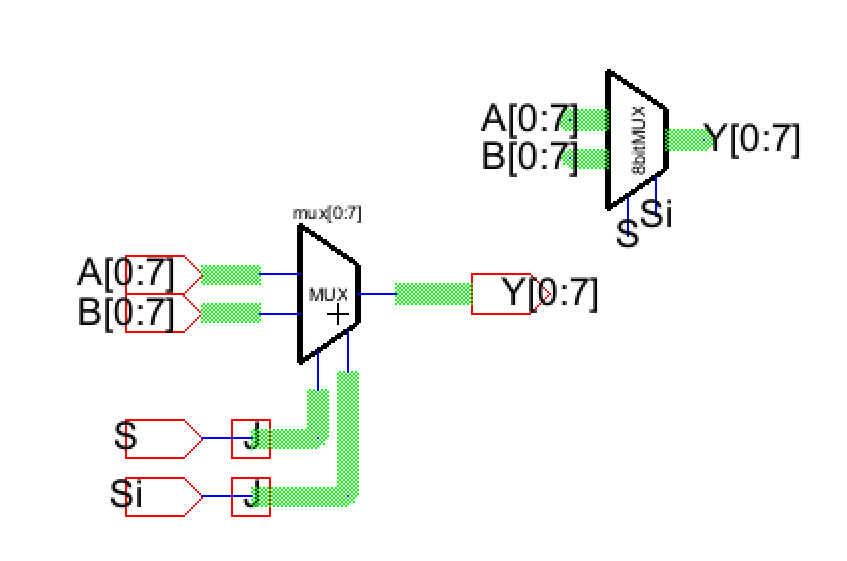

Figure 3: The MUX is then used to create a schematic for the 8-bit MUX.

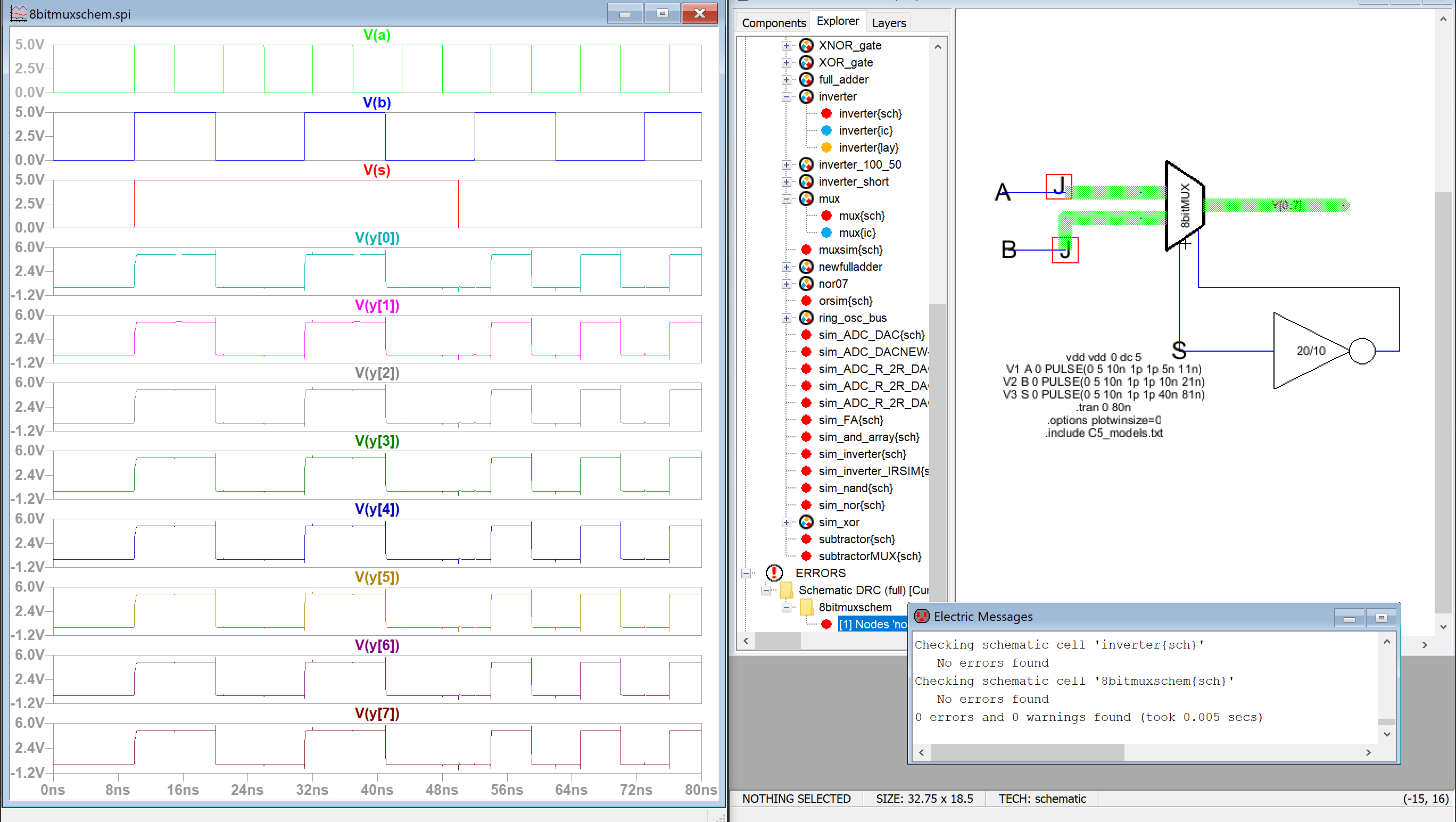

Figure 4: The schematic is then tested in LT Spice to verify functionality.

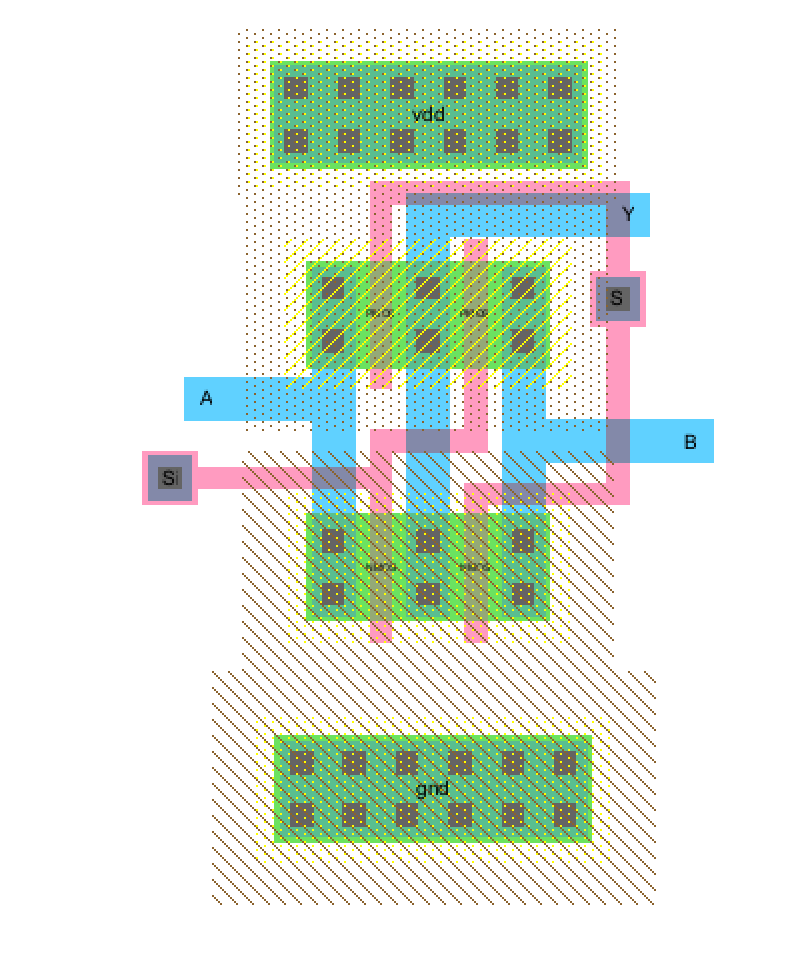

Figure 5: The layout of the MUX is then created in Electric VLSI.

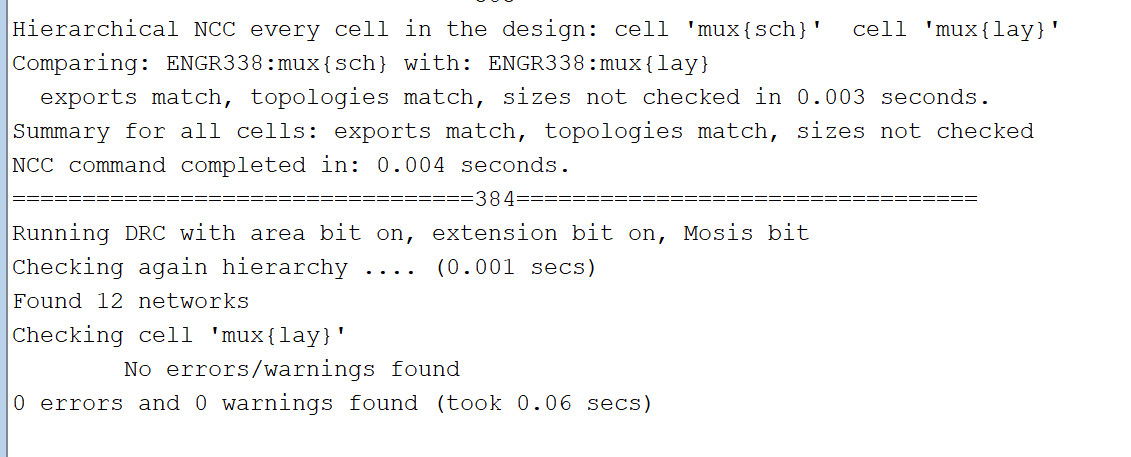

Figure 6: The Layout passes both DRC and NCC error checks.

Figure 7: The layout of the 8-bit MUX can then be created.

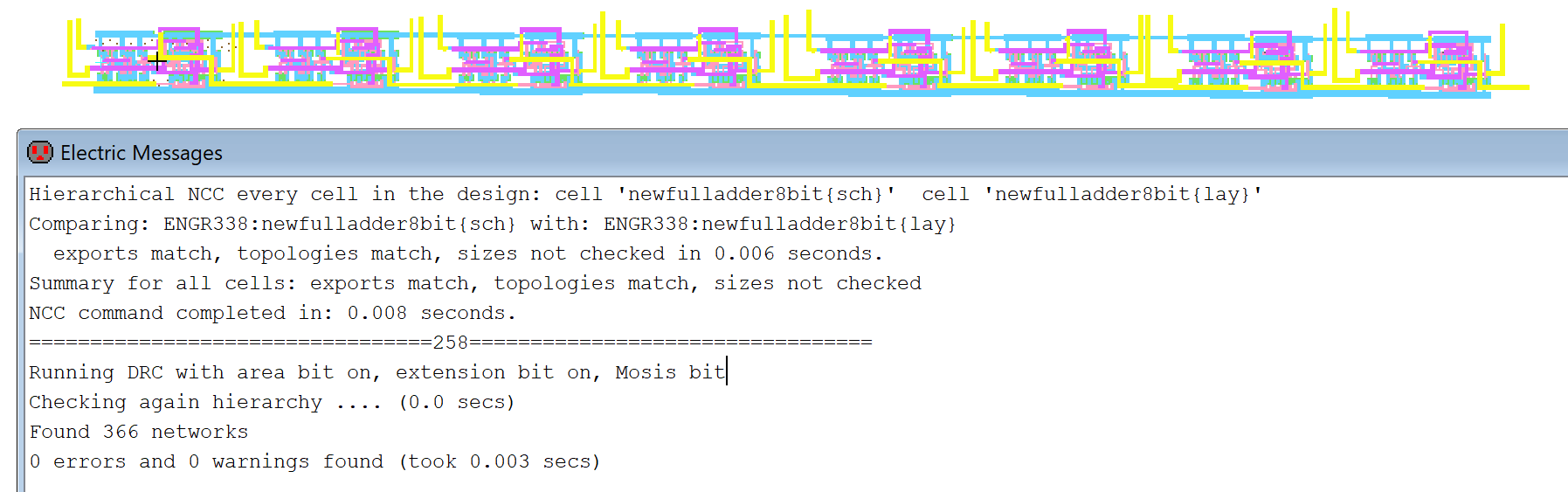

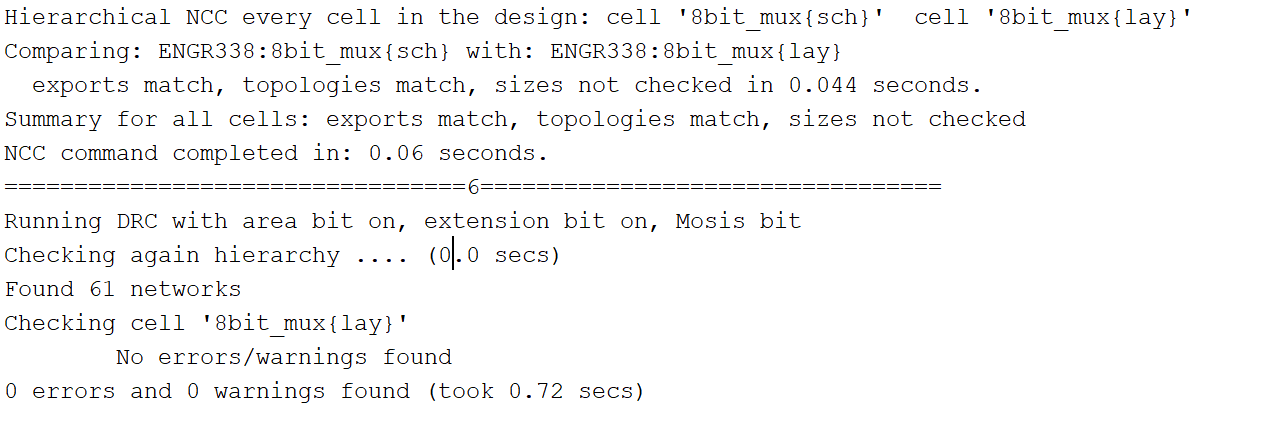

Figure 8: The layout passes both DRC and NCC error checks.

Task 2:

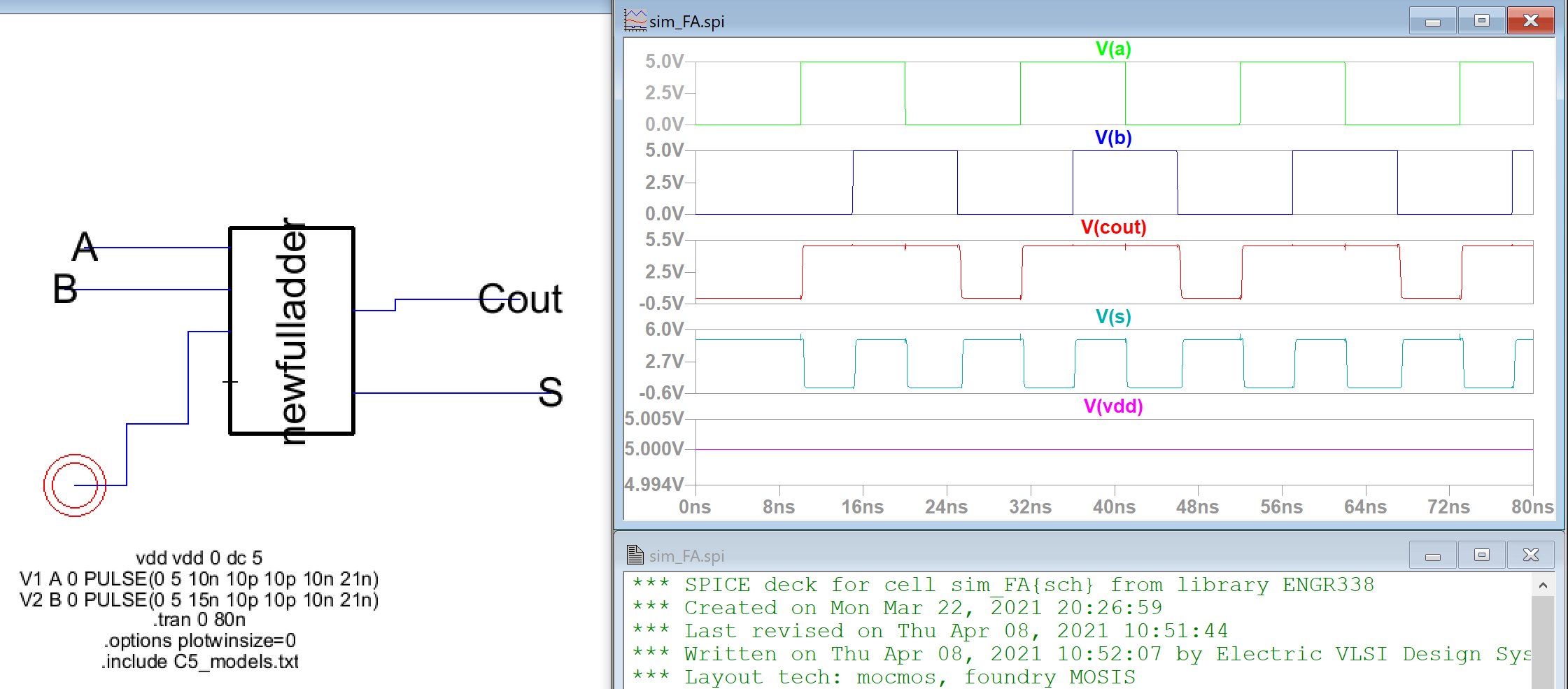

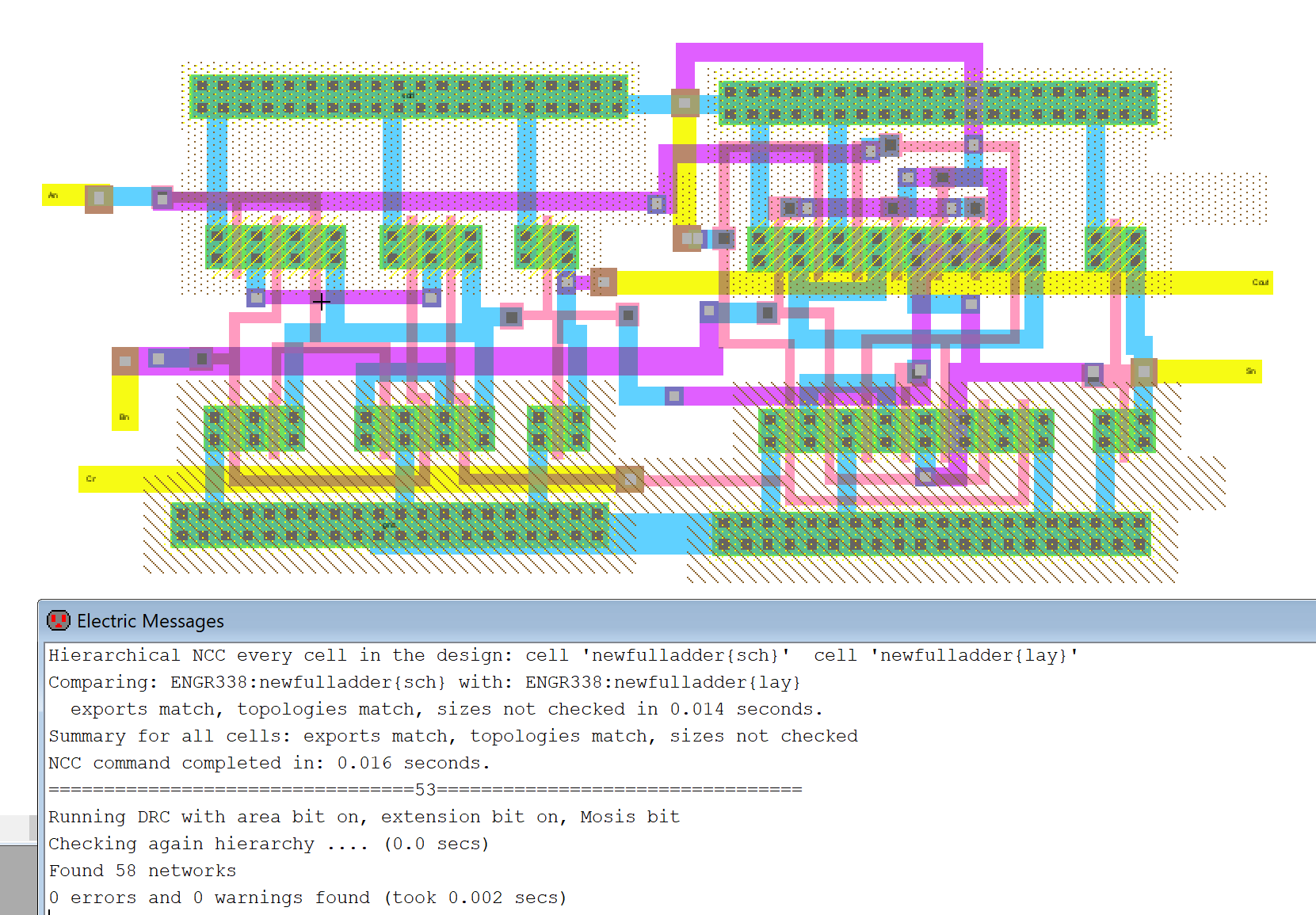

In this task we built a 1-bit high-speed full-adder

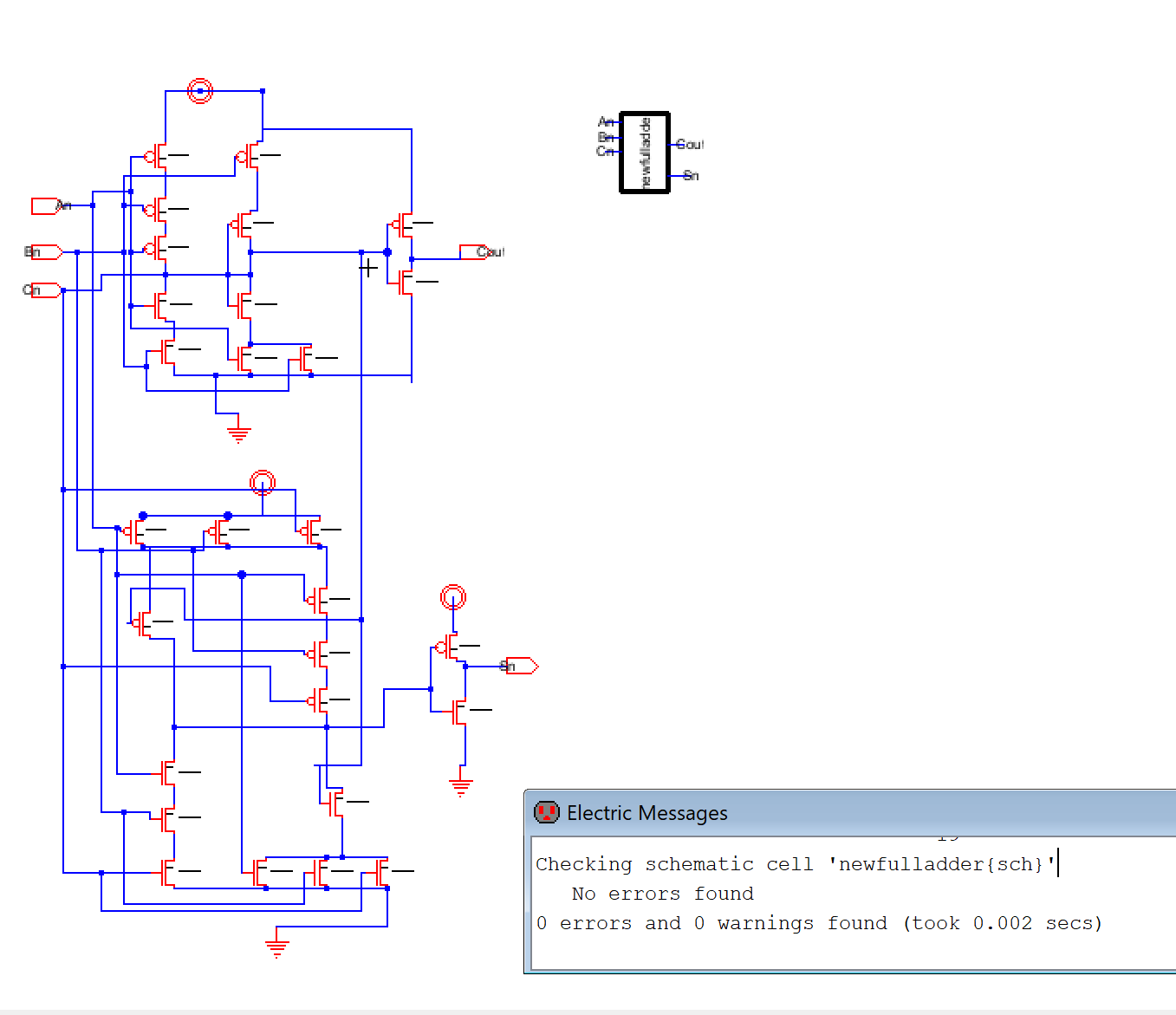

Figure 9: The schematic of the adder is built in Electric VLSI

Figure 10: The schematic is then tested for functionality in LT Spice.

Figure 11: The Layout of the adder can then be built. The layout is more compact than the traditional Full-Adder

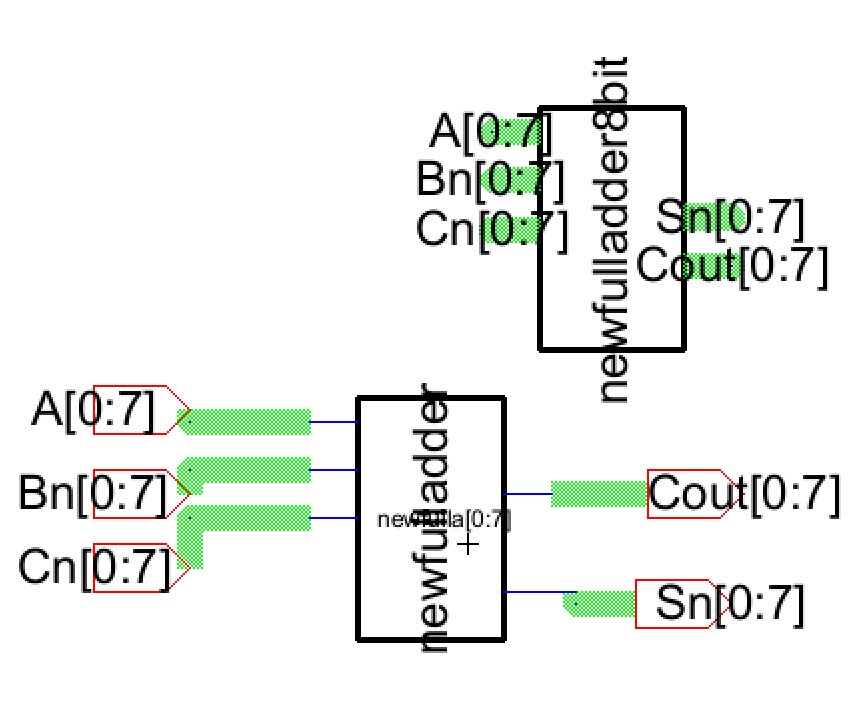

Task 3:

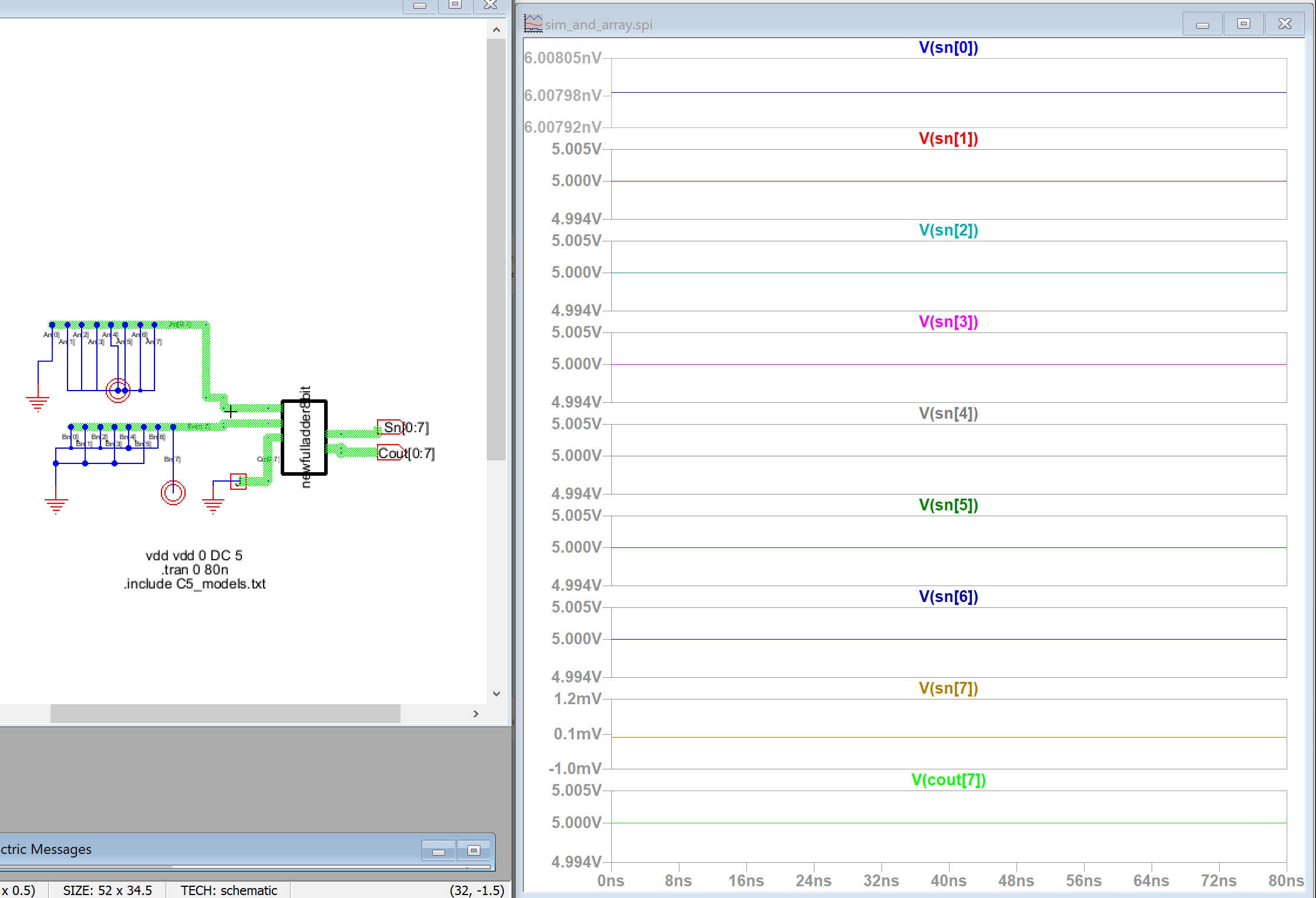

In this task we built used our previous 1-bit high-speed full adder to build an 8-bit version.

Figure 12: The schematic of the 8-bit high-speed full adder is built in Electric VLSI

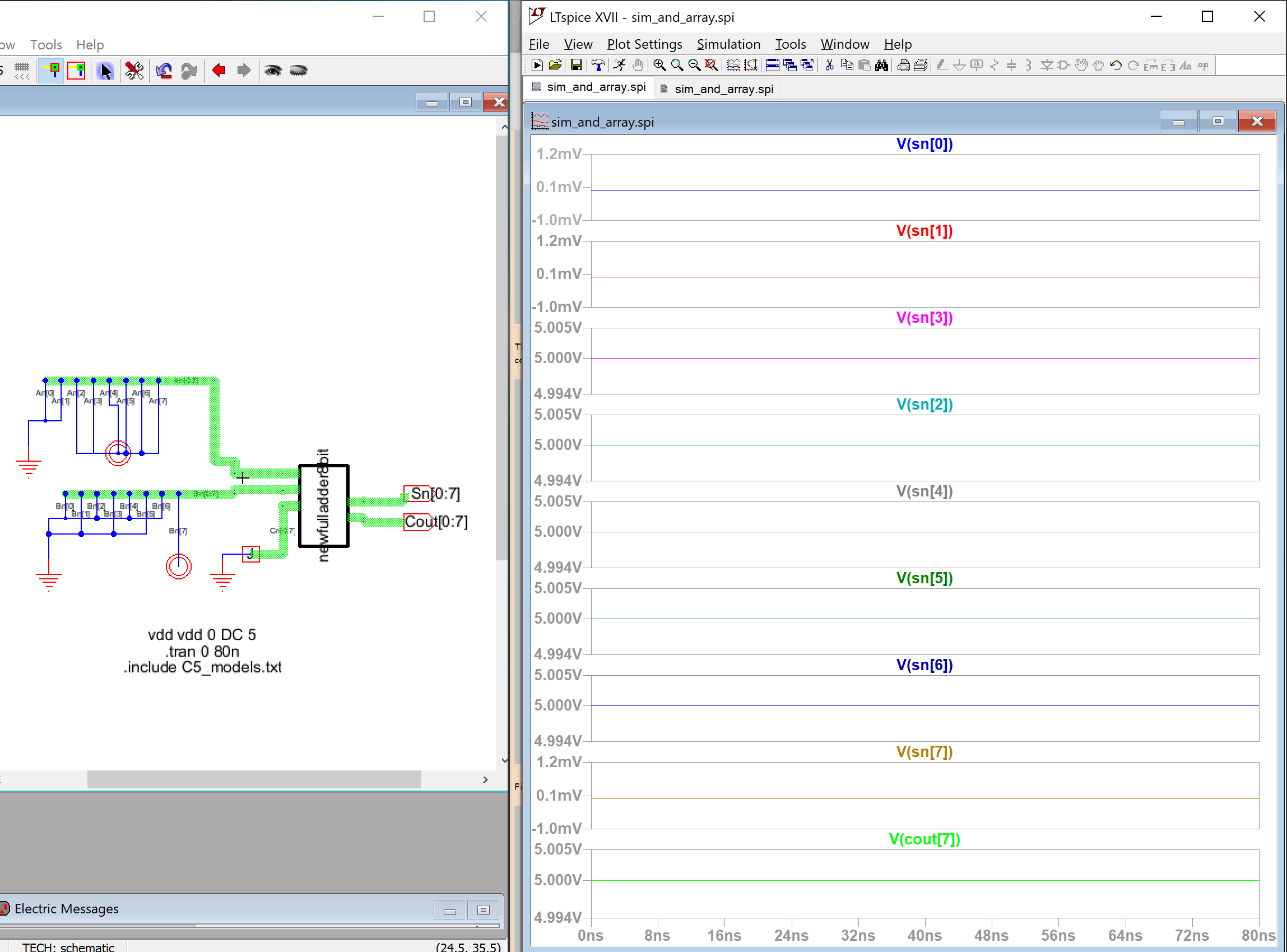

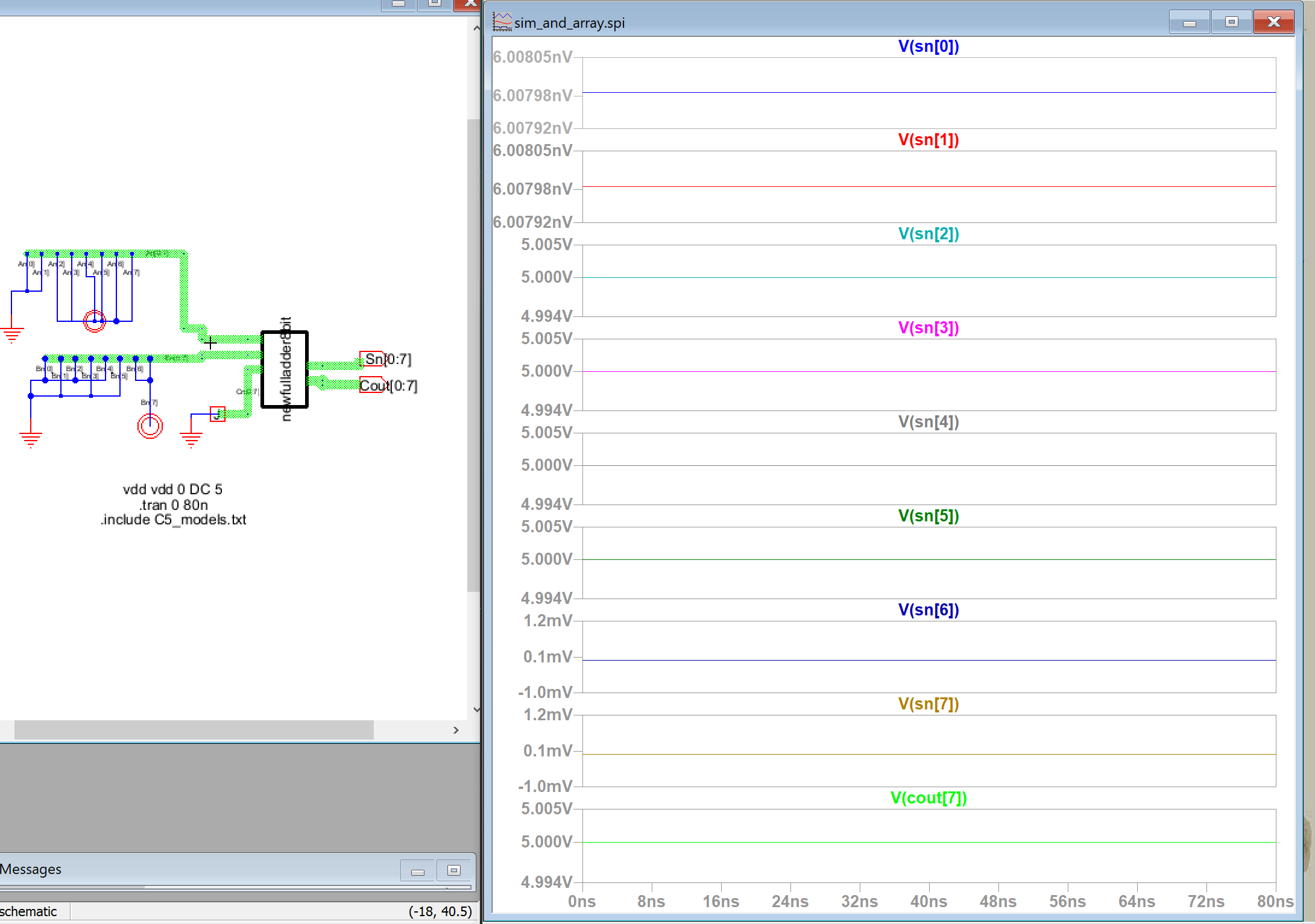

Figure 13: The schematic of the 8-bit high-speed full adder can then be tested in LT Spice to verify functionality.

Figure 14: The schematic of the 8-bit high-speed full adder is further tested in LT Spice to verify functionality.

Figure 15: The schematic of the 8-bit high-speed full adder is further tested in LT Spice to verify functionality.

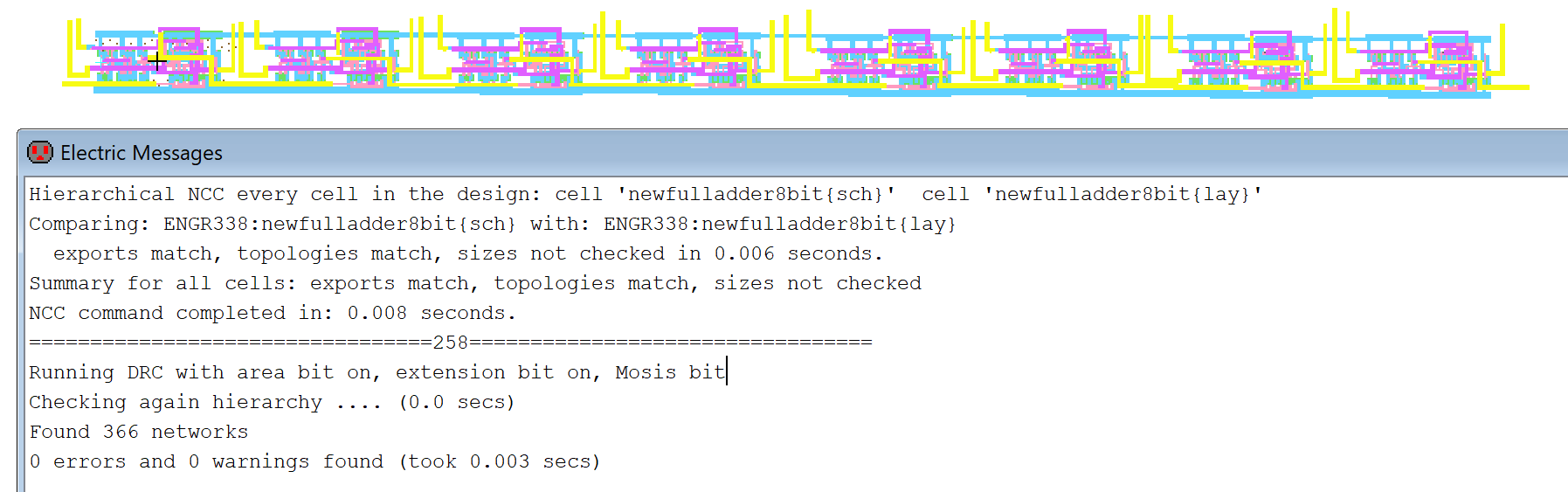

Figure 16: The layout of the 8-bit high-speed full adder can then be built in Electric VLSI

Discussion:In this task we started by building and simulating the 8-bit MUX.

Figure 1: The schematic of the MUX is built in Electric VLSI and it's output is displayed in LT Spice.

Figure 2: The schematic is then tested in LT Spice to verify functionality.

Figure 3: The MUX is then used to create a schematic for the 8-bit MUX.

Figure 4: The schematic is then tested in LT Spice to verify functionality.

Figure 5: The layout of the MUX is then created in Electric VLSI.

Figure 6: The Layout passes both DRC and NCC error checks.

Figure 7: The layout of the 8-bit MUX can then be created.

Figure 8: The layout passes both DRC and NCC error checks.

Task 2:

In this task we built a 1-bit high-speed full-adder

Figure 9: The schematic of the adder is built in Electric VLSI

Figure 10: The schematic is then tested for functionality in LT Spice.

Figure 11: The Layout of the adder can then be built. The layout is more compact than the traditional Full-Adder

Task 3:

In this task we built used our previous 1-bit high-speed full adder to build an 8-bit version.

Figure 12: The schematic of the 8-bit high-speed full adder is built in Electric VLSI

Figure 13: The schematic of the 8-bit high-speed full adder can then be tested in LT Spice to verify functionality.

Figure 14: The schematic of the 8-bit high-speed full adder is further tested in LT Spice to verify functionality.

Figure 15: The schematic of the 8-bit high-speed full adder is further tested in LT Spice to verify functionality.

Figure 16: The layout of the 8-bit high-speed full adder can then be built in Electric VLSI

This lab was an excellent overview of the internal design of the MUX device and the high-speed full adder. This lab helped to show how the internal structure of these devices and how they are designed and tested using Electric VLSI and LT Spice.