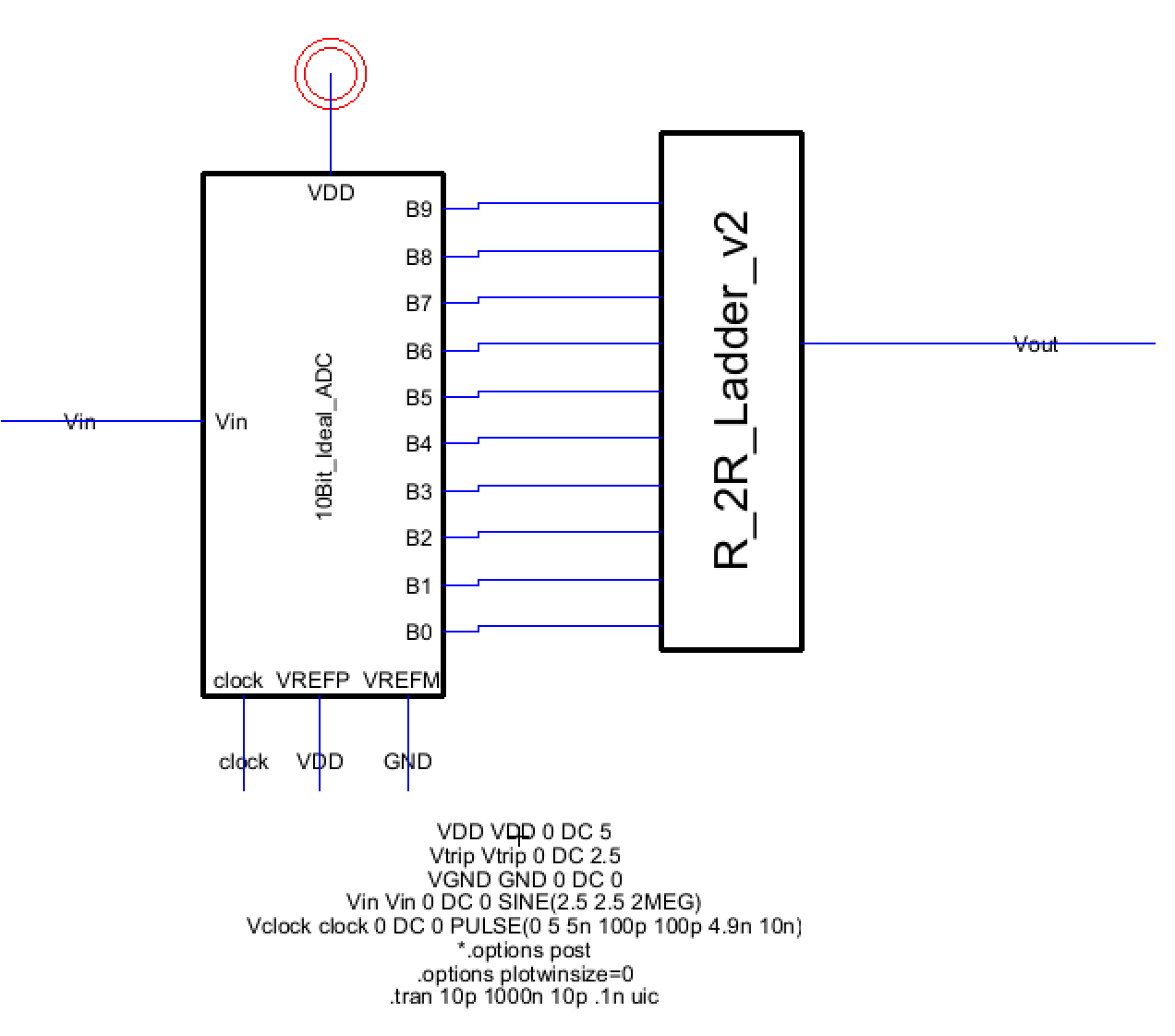

Figure 5. The R-2R DAC is then connected to our ideal ADC for testing

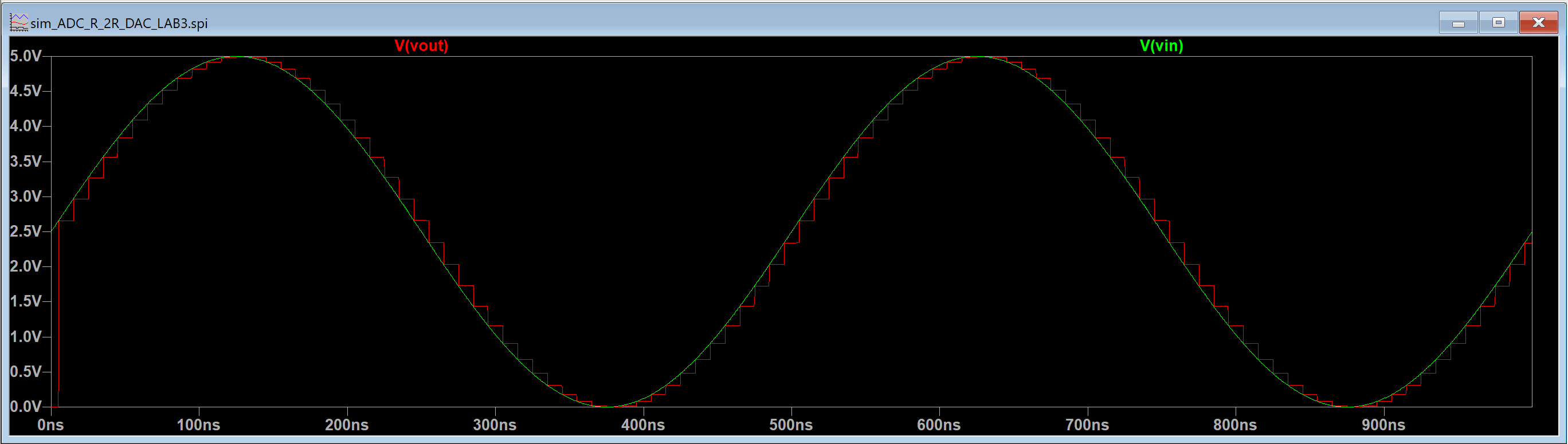

Figure 6. The

output of the R-2R DAC is graphed alongside the input of the ADC showing the proper output

Figure 6. The

output of the R-2R DAC is graphed alongside the input of the ADC showing the proper output

Discussion:

This lab was an excellent introduction to the use of subcells and

layouts in VLSI design. This lab takes us one step further into

understanding how common digital devices are designed and function. The

use of subcells helps to greatly reduce the amount of work required to

design a component with repeating patterns.