ENGR338 Lab 2021 Fall

Lab 7

Name: David Lee

Email:

djlee1@fortlewis.edu

Using Buses in ElectricVLSI

Introduction:

In

this lab we used ElectricVLSI to build a ring oscillator using buses and to build a multi-bit gate

Materials and Methods:

In this Lab we used the computer program ElectricVLSI to create the

schematics that were then simulated in LTSpice.

Results:

Task 1: Build and simulate a Ring Oscillator

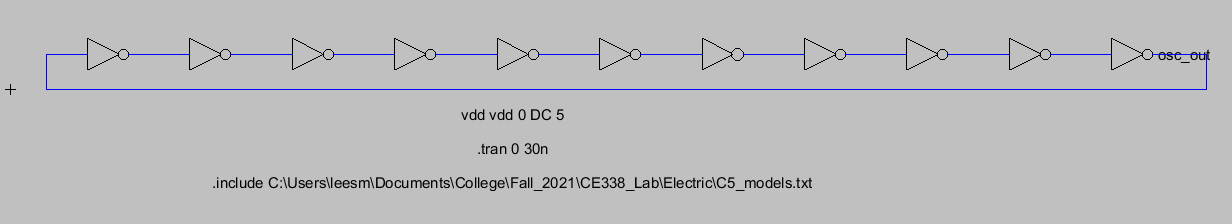

Figure 1: Shows the Schematic of the Ring Oscillator

Figure

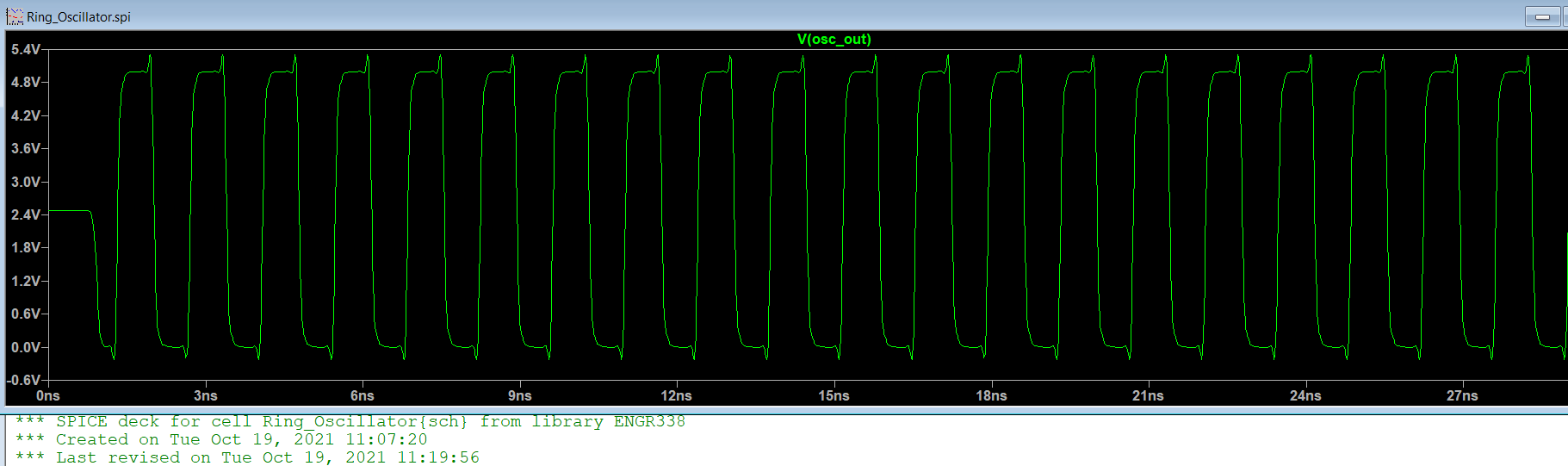

2: Shows the LTSpice simulation output of the Ring Oscillator

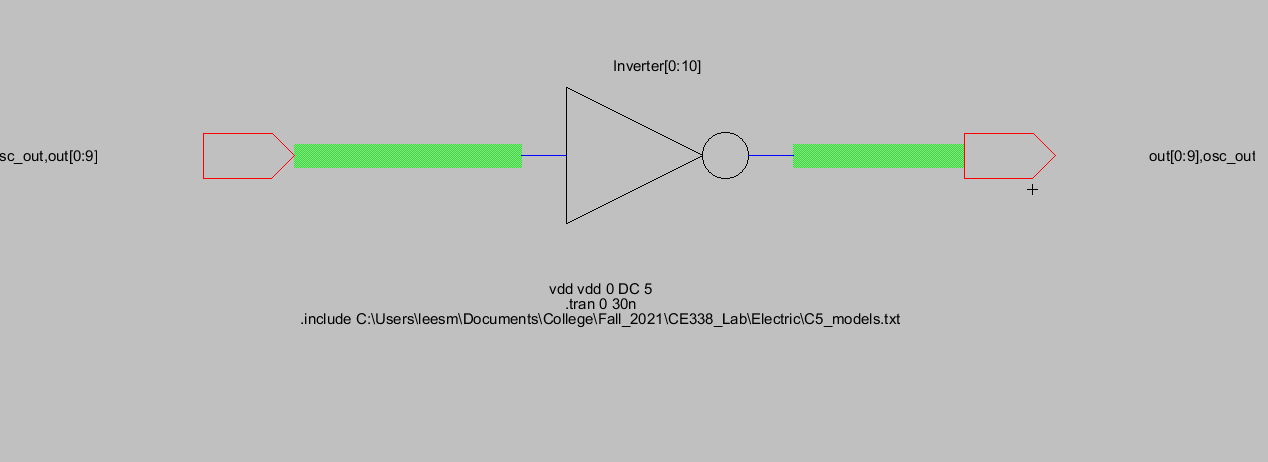

Figure 3: Shows the Schematic of a Ring Oscillator Bus

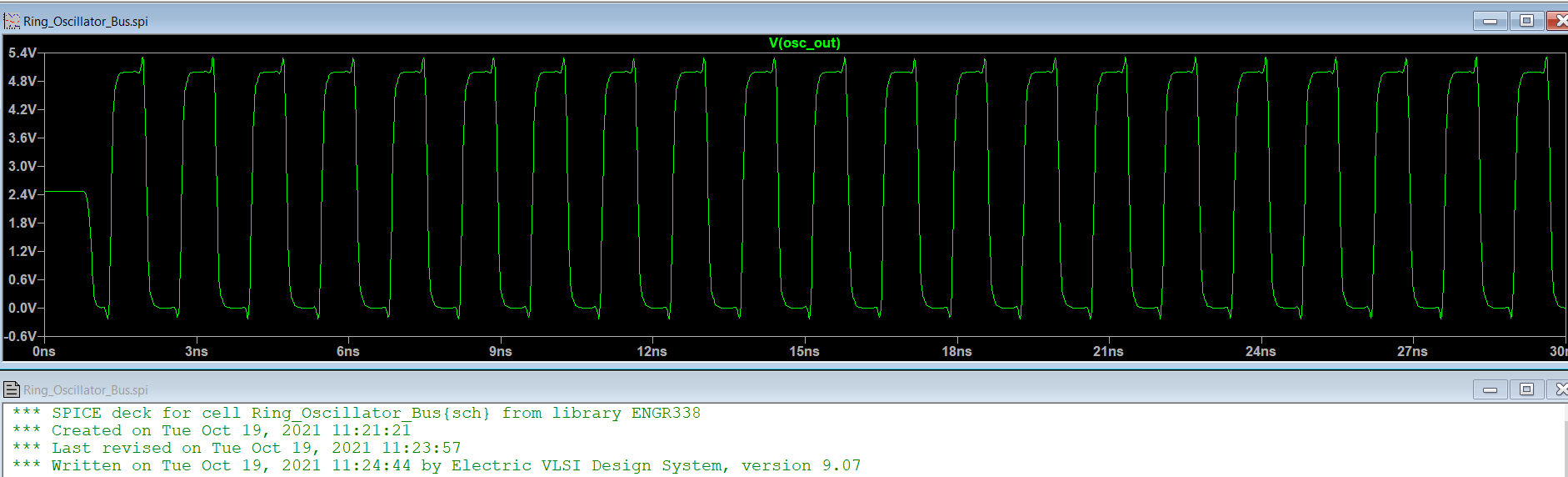

Figure 4: Shows the LTSpice output of the Ring Ocsillator Bus

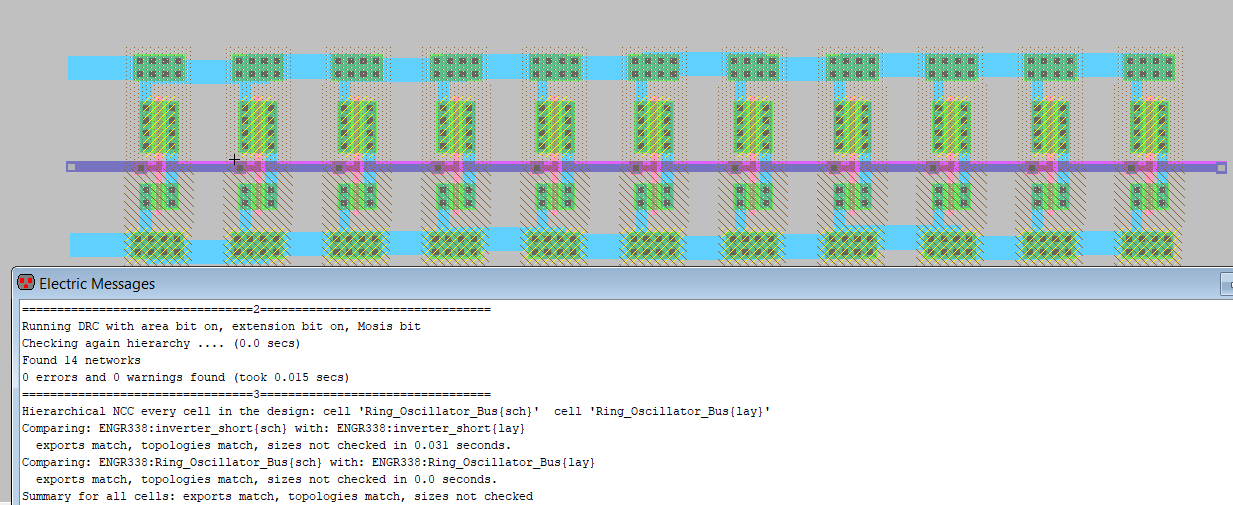

Figure 5: Shows the Layout of the Ring Ocsillator Bus with no Errors

Task 2: Design an 8-bit AND gate

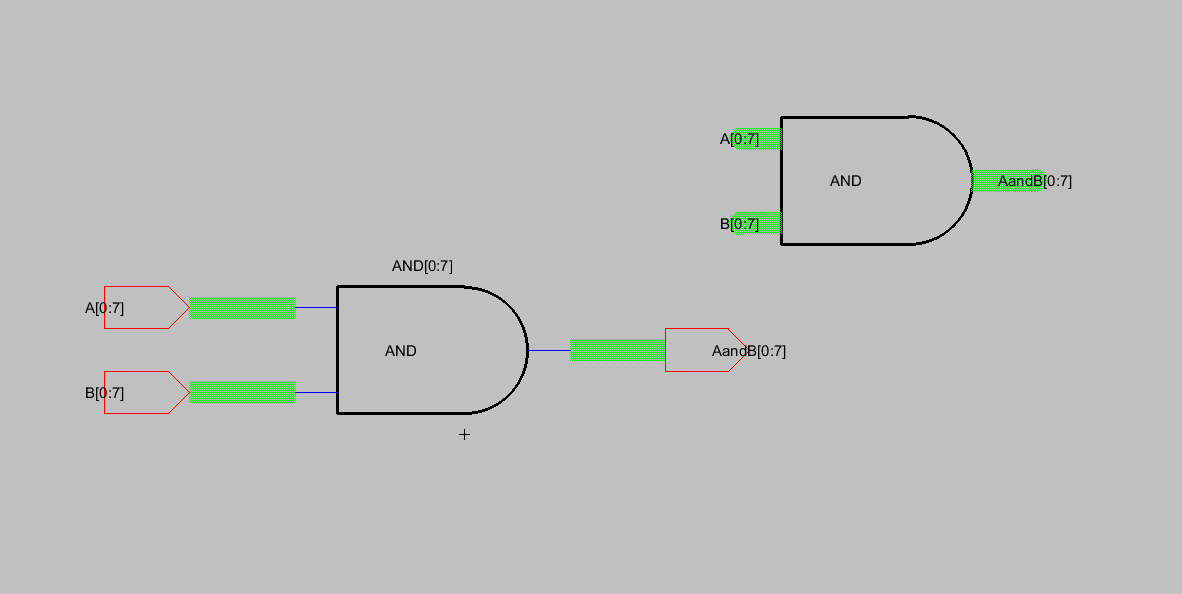

Figure

6: Shows the schematic of the 8-bit AND gate

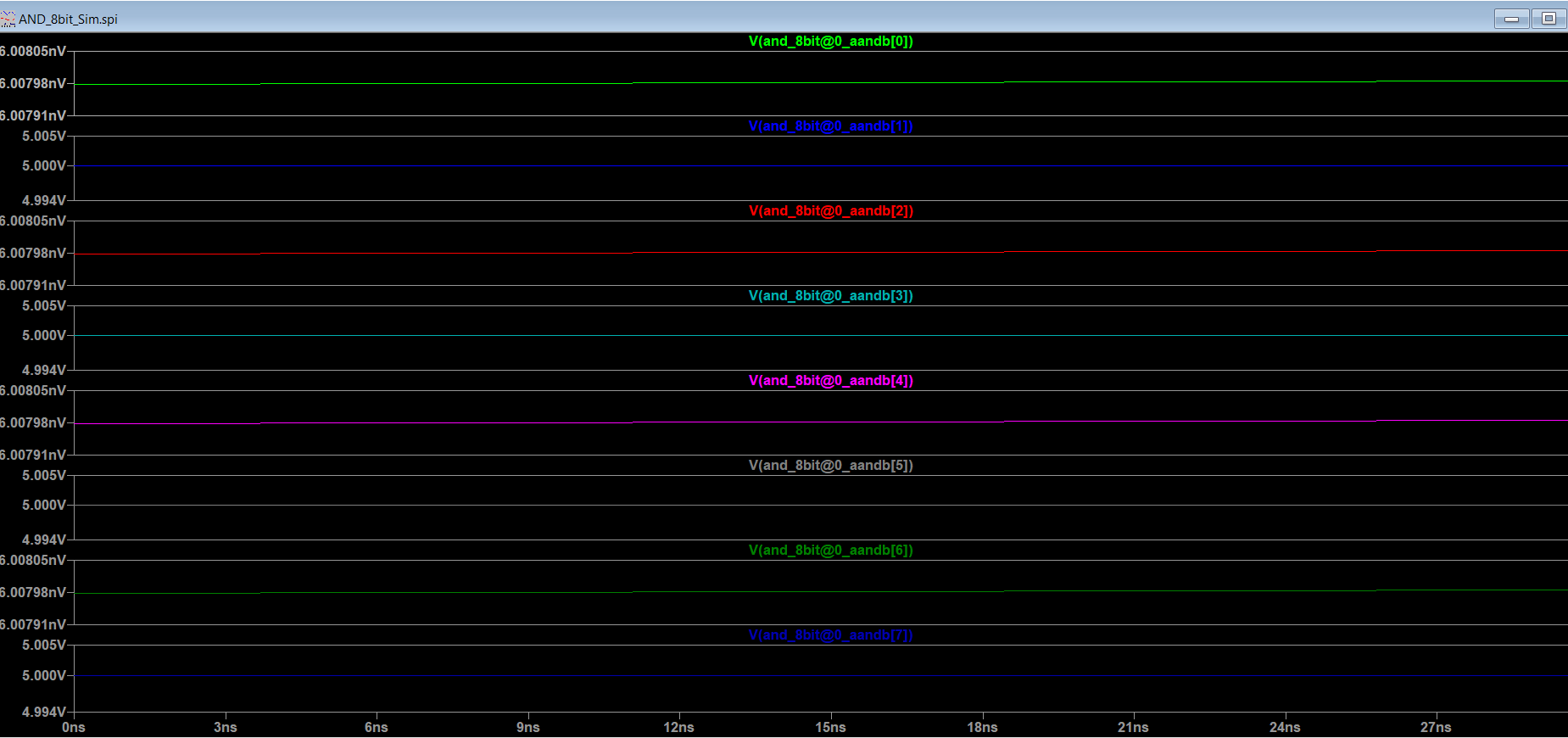

Figure 7: Shows the LTSpice Simulations of the 8-bit AND gate

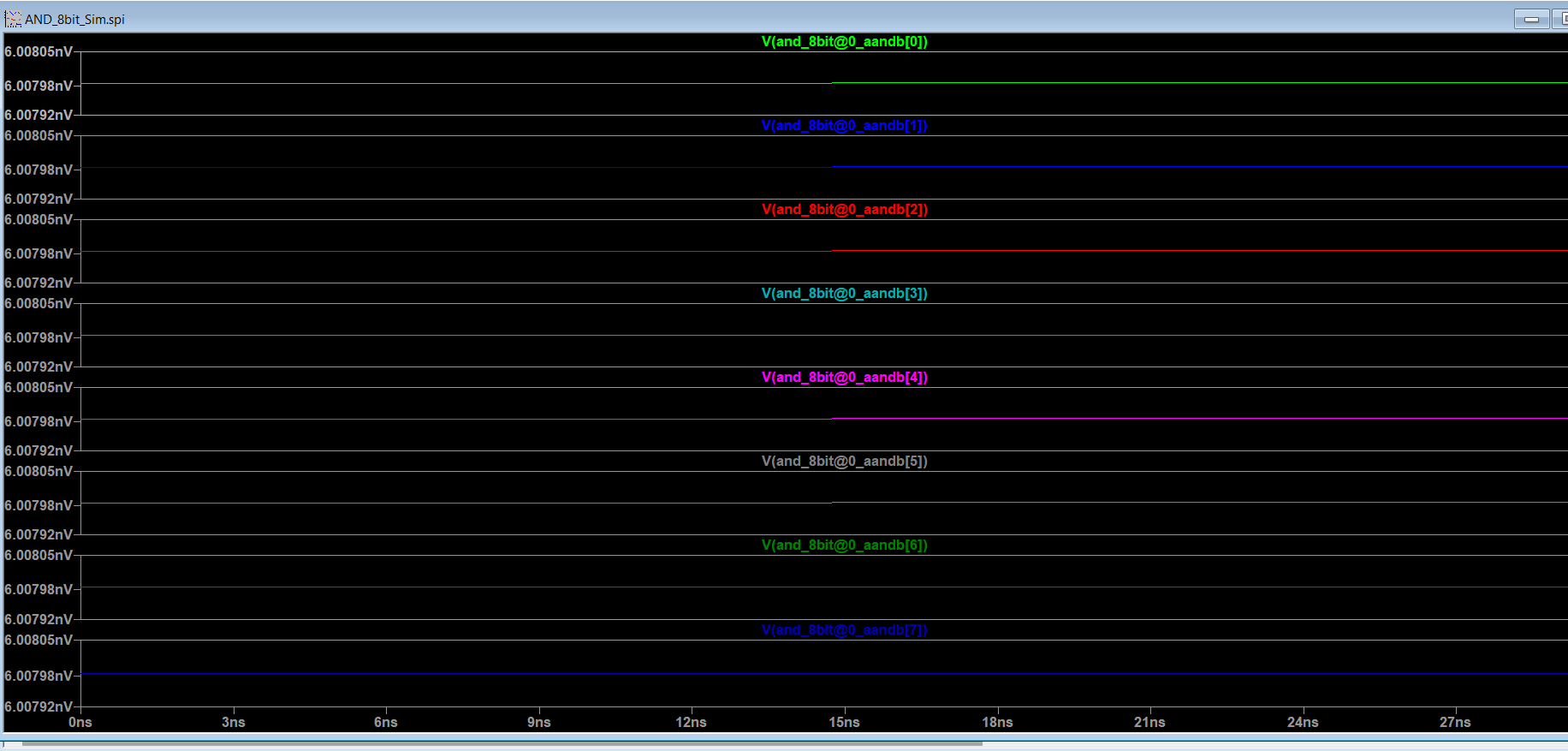

Figure 8: Shows LTSpice simulation of a grounded 8-bit AND gate

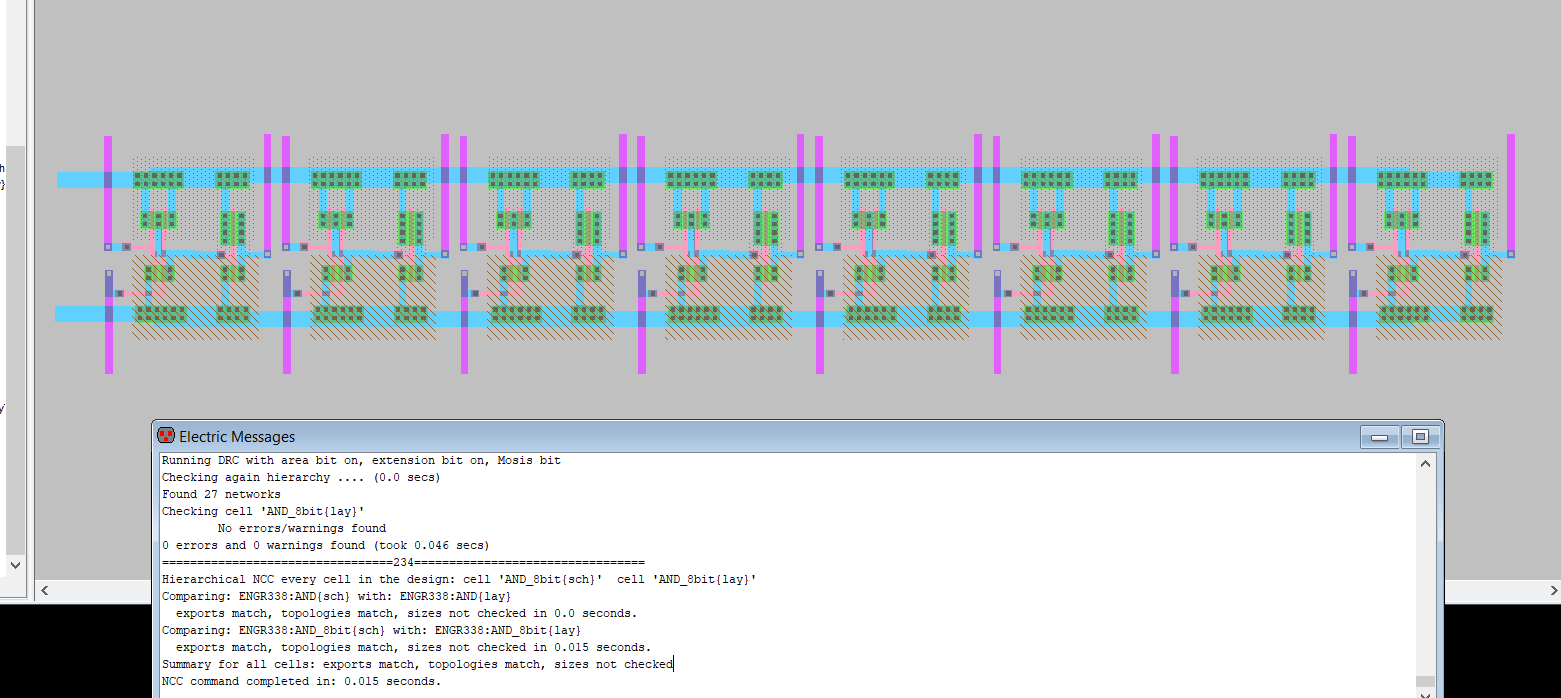

Figure 9: Shows the full layout of the 8-bit AND gate with no errors after running DRC and NCC

Task 3: Design an 8-bit OR gate

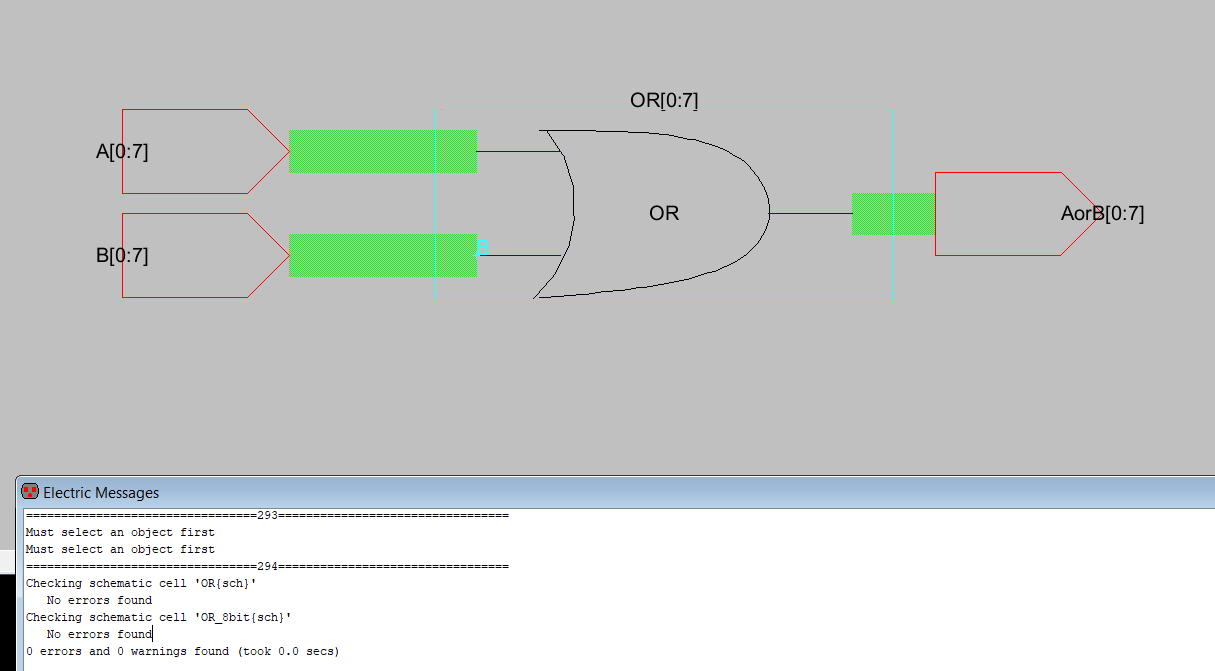

Figure 10: Shows the schematic of the 8-bit OR gate with no errors

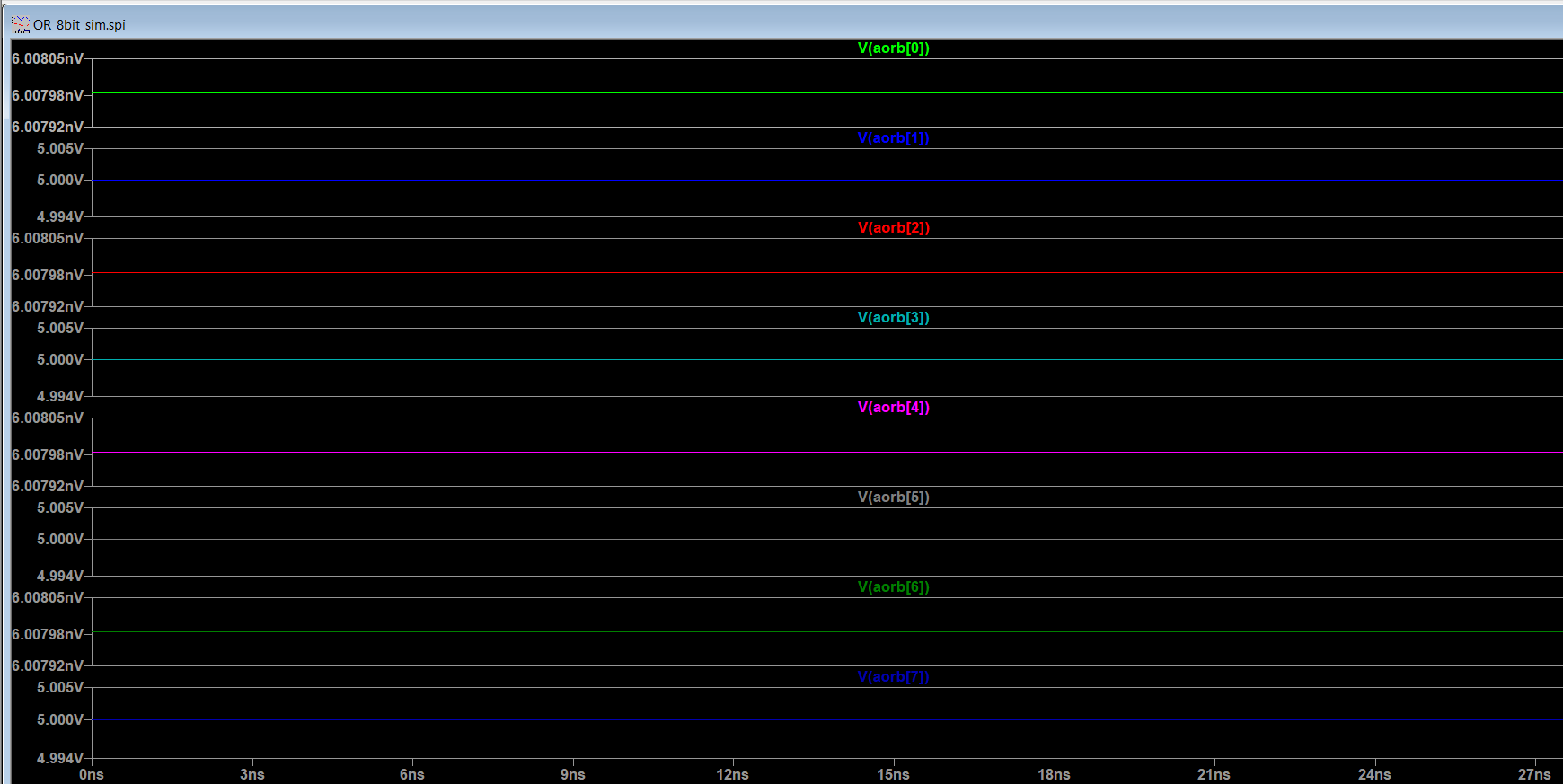

Figure 11: Shows the LTSpice simulation of the 8-bit OR gate

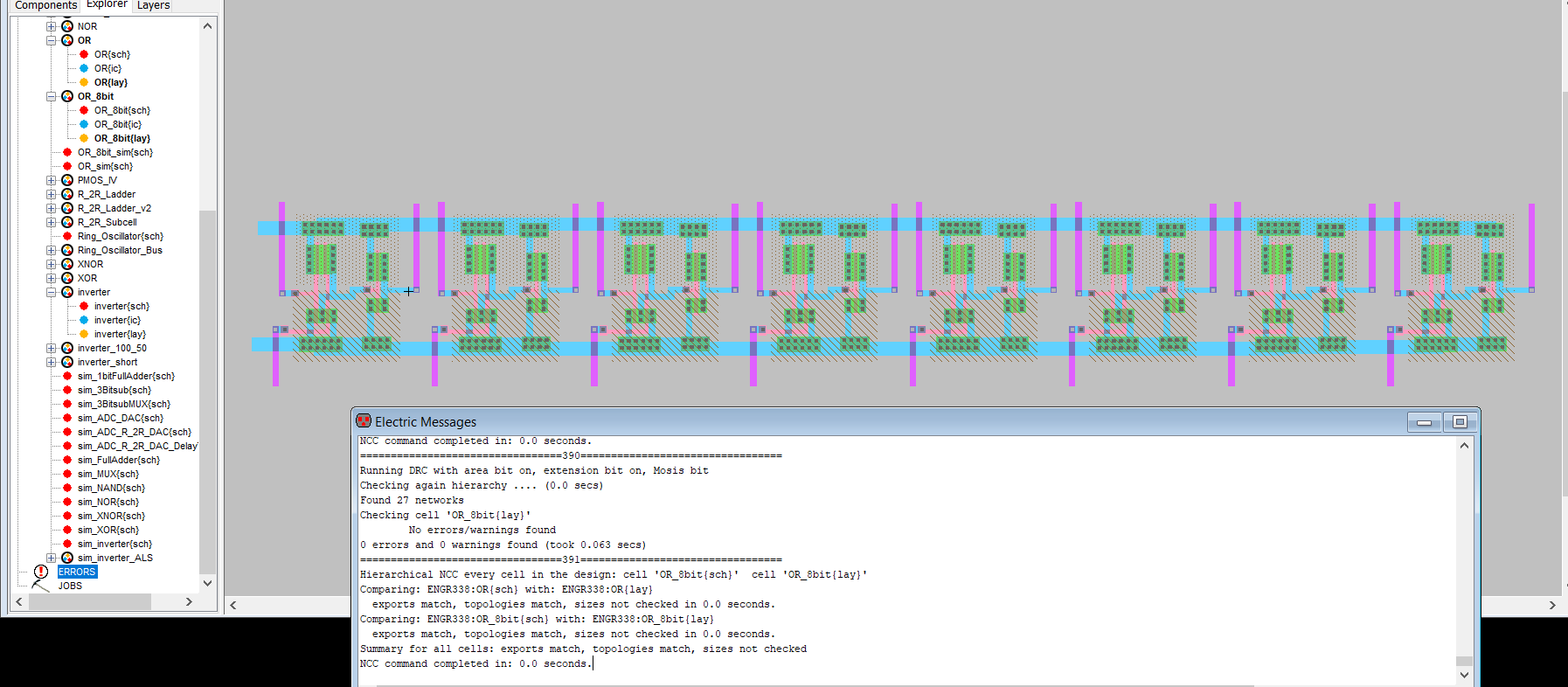

Figure 12: Shows the layout of the 8-bit OR gate with no errors after running DRC and NCC

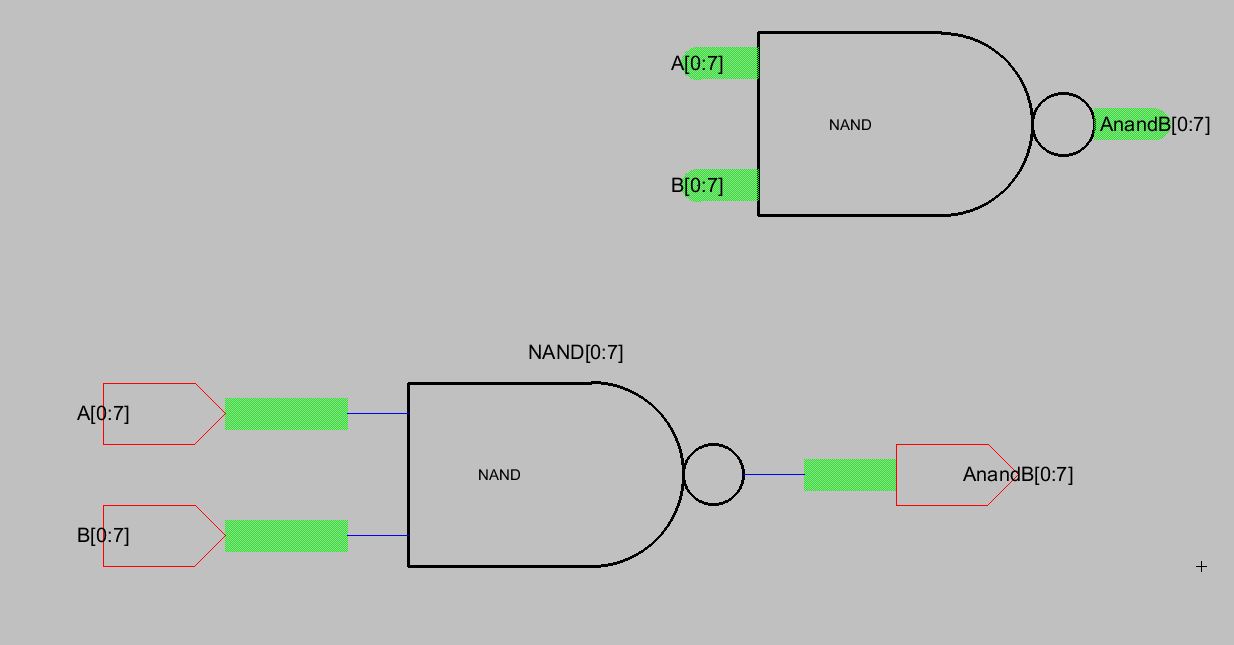

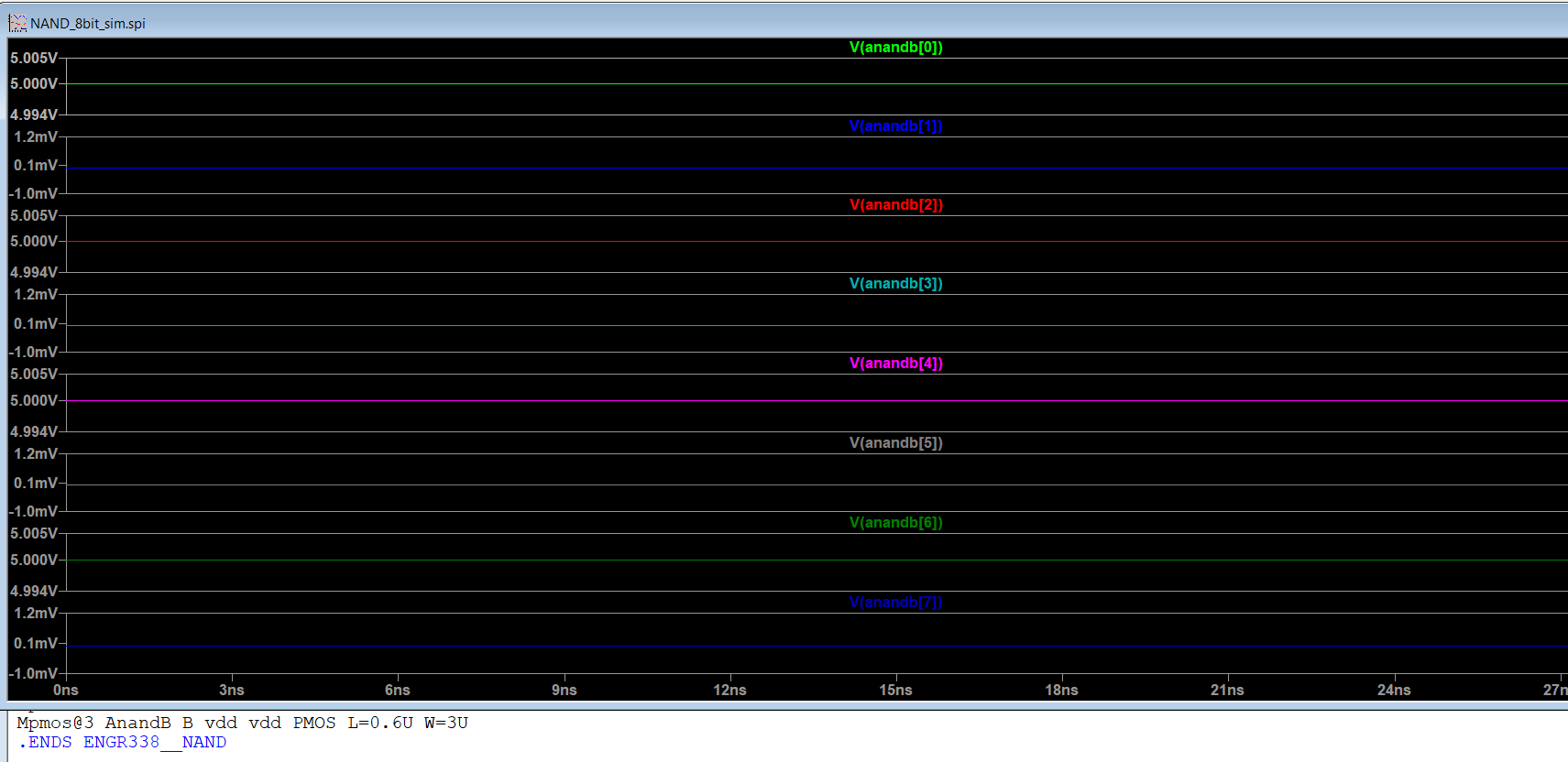

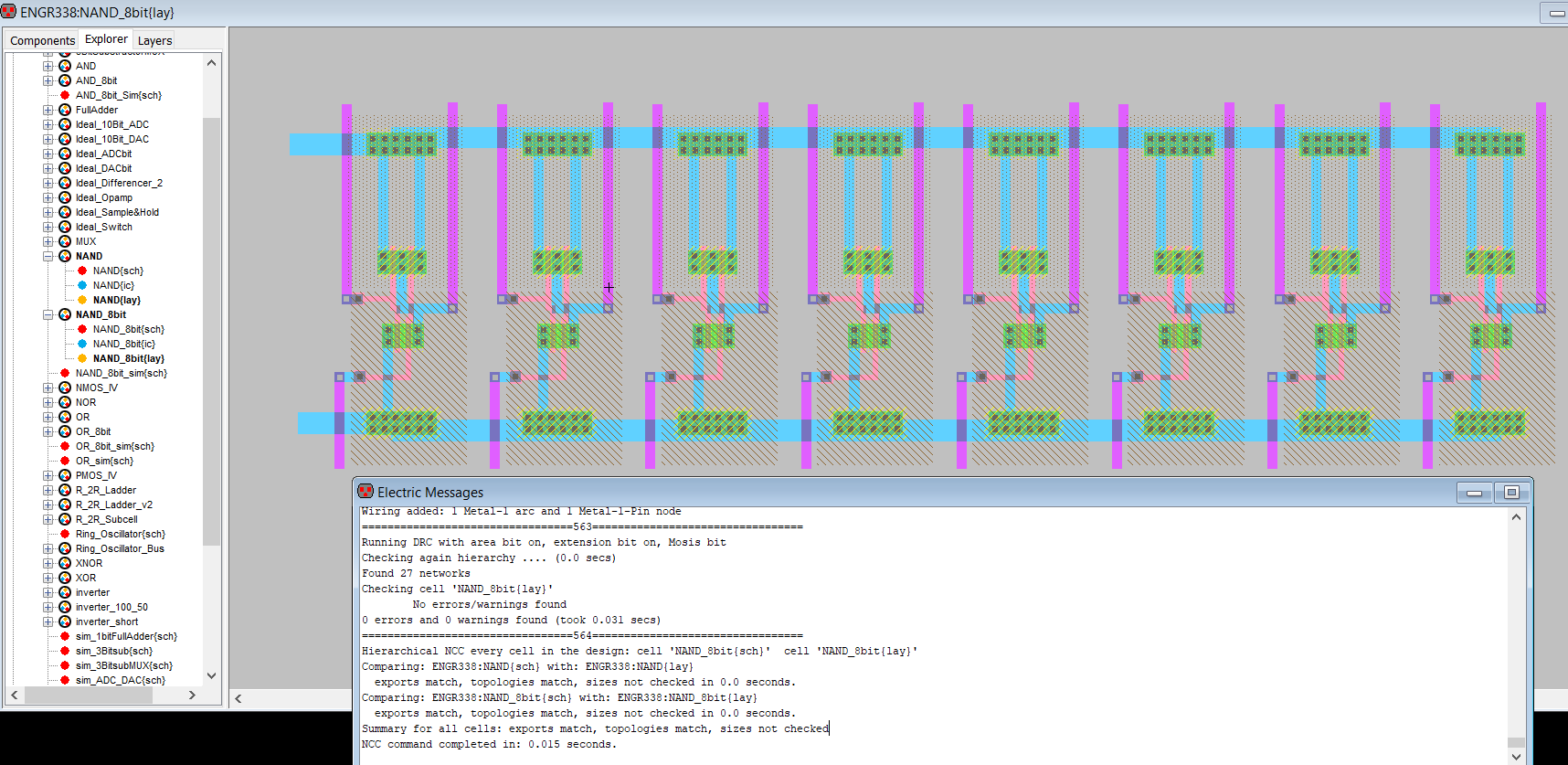

Task 4: Design an 8-bit NAND gate

Figure 13: Shows the Schematic of the 8-bit NAND gate

Figure 14: Shows the LTSpice simulation of the 8-bit NAND gate

Figure 15: Shows the layout of the 8-bit NAND gate with no errors after running DRC and NCC

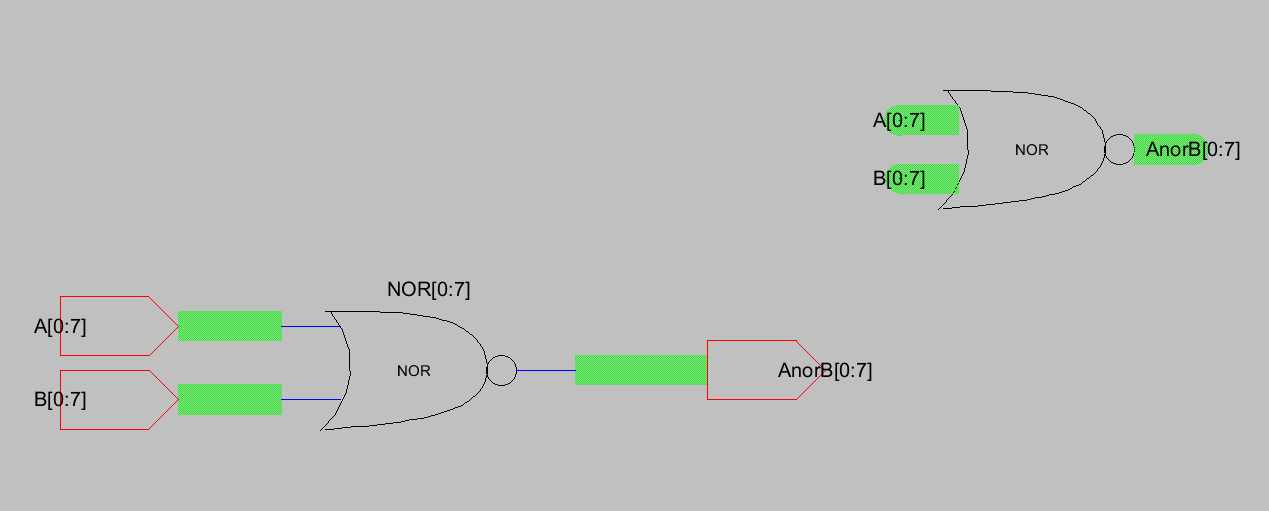

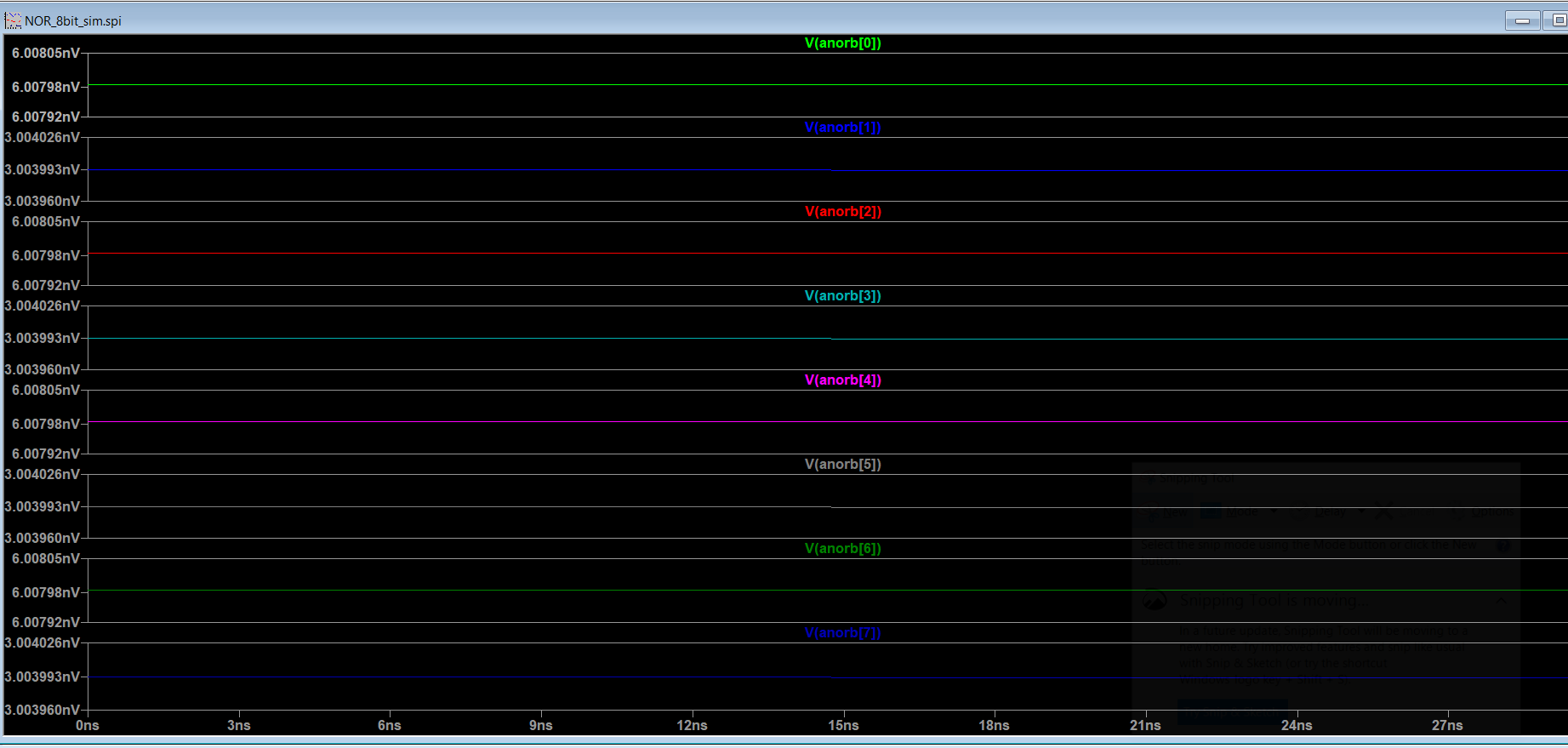

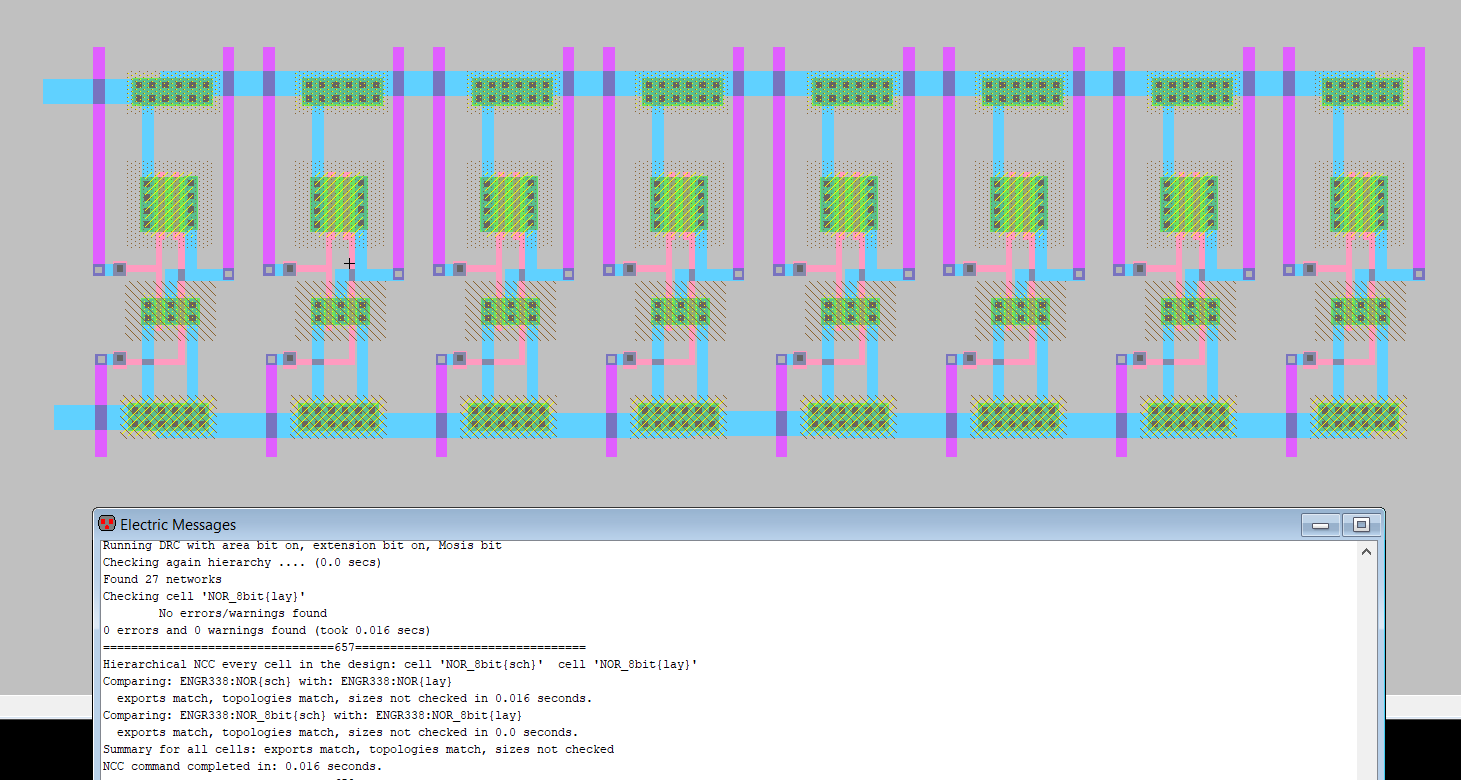

Task 5: Design an 8-bit NOR gate

Figure 16: Shows the layout of the 8-bit NOR gate with no errors after running DRC and NCC

Figure 17: Shows the layout of the 8-bit NOR gate with no errors after running DRC and NCC

Figure 18: Shows the layout of the 8-bit NOR gate with no errors after running DRC and NCC

5. Discussion

The

lab was able to be successfully completed because we were able to

create the simulate and have no errors in the final layout of the Ring

Oscillator, 8-bit AND,NAND,OR and NOR gates. Some problems I ran into

during this lab that made it take longer than it should have was that I

had forgotten that the names of the cells cant have special characters

in them. This became a problem once I started to run the checks to see

if I had any errors. This would cause errors to be thrown because the

program would not like the naming conventions.