ENGR338 Lab 2021 Fall

Lab 6

Name: David Lee

Email:

djlee1@fortlewis.edu

Building

a NAND, NOR, XOR and Full Adder

Introduction:

In

this lab we used ElectricVLSI to build a NAND, NOR, XOR gates and a

Full Adder.

Materials and Methods:

In this Lab we used the computer program ElectricVLSI to create the

schematics that were then simulated in LTSpice.

Results:

Task 1: Create the schematic and layout of the NAND gate

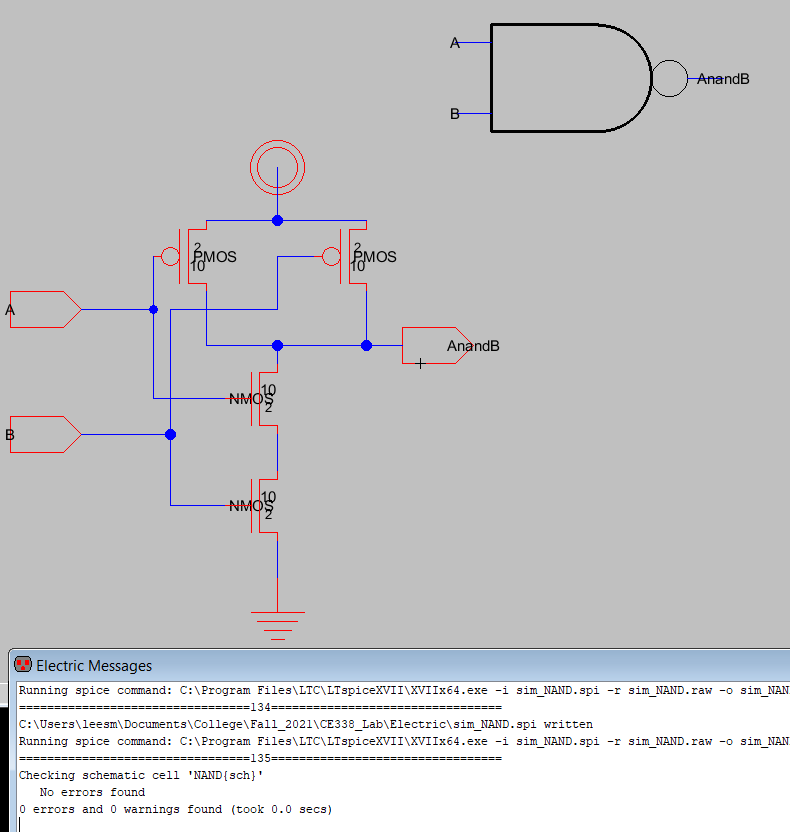

Figure 1: Shows the

Schematic of a NAND gate in Electric without any errors present

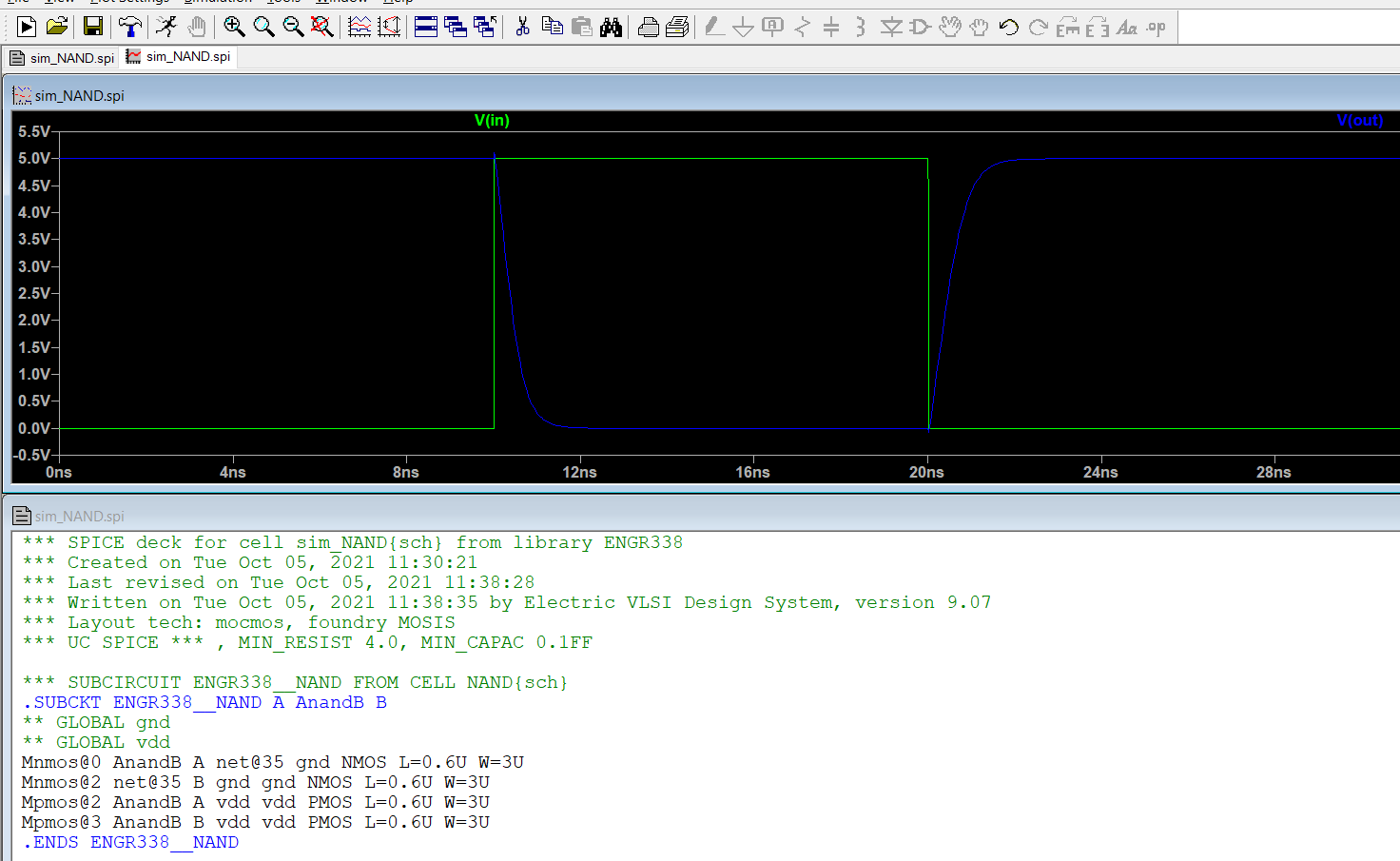

Figure

2: Shows the LTSpice simulations of the NAND gate

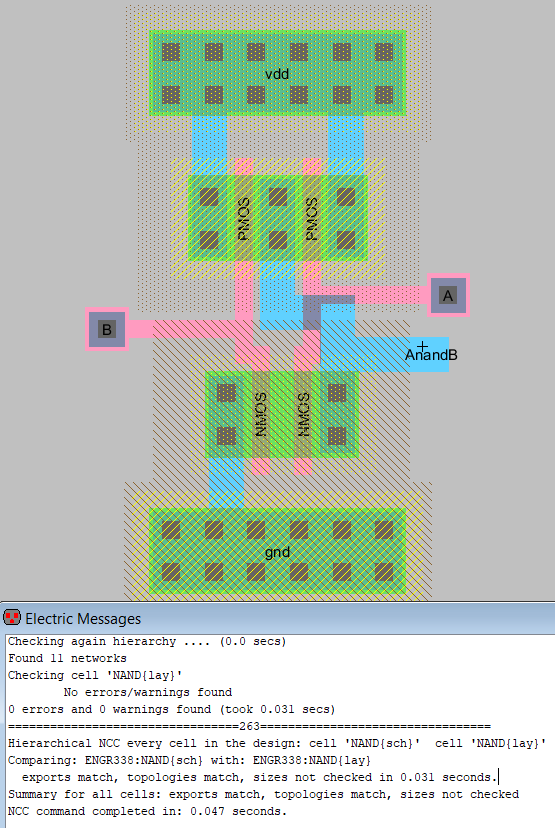

Figure 3: Shows the Layout of a

NAND gate without any errors on DRC and NCC

Task 2: Create the

schematic and layout of the NOR gate

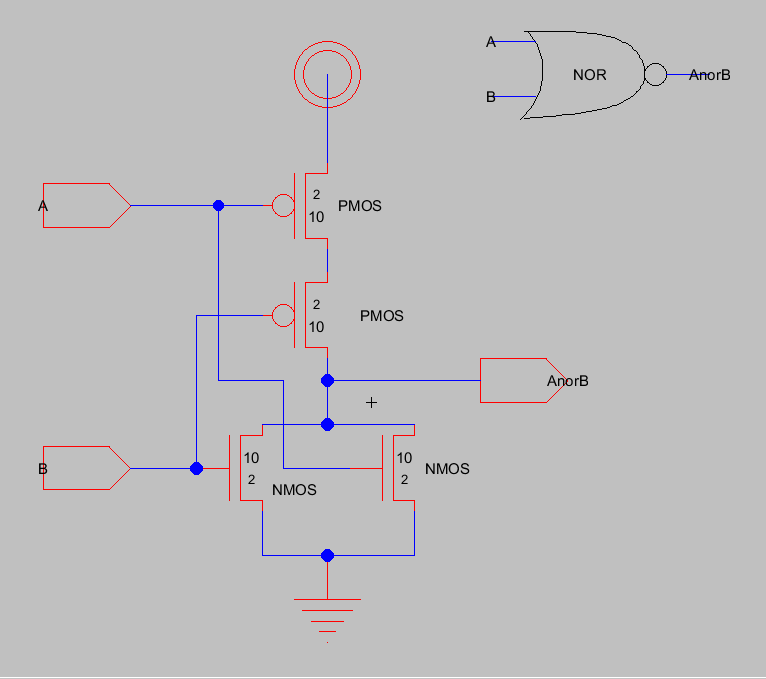

Figure 4: Shows

the

Schematic of a NOR gate in Electric without any errors present

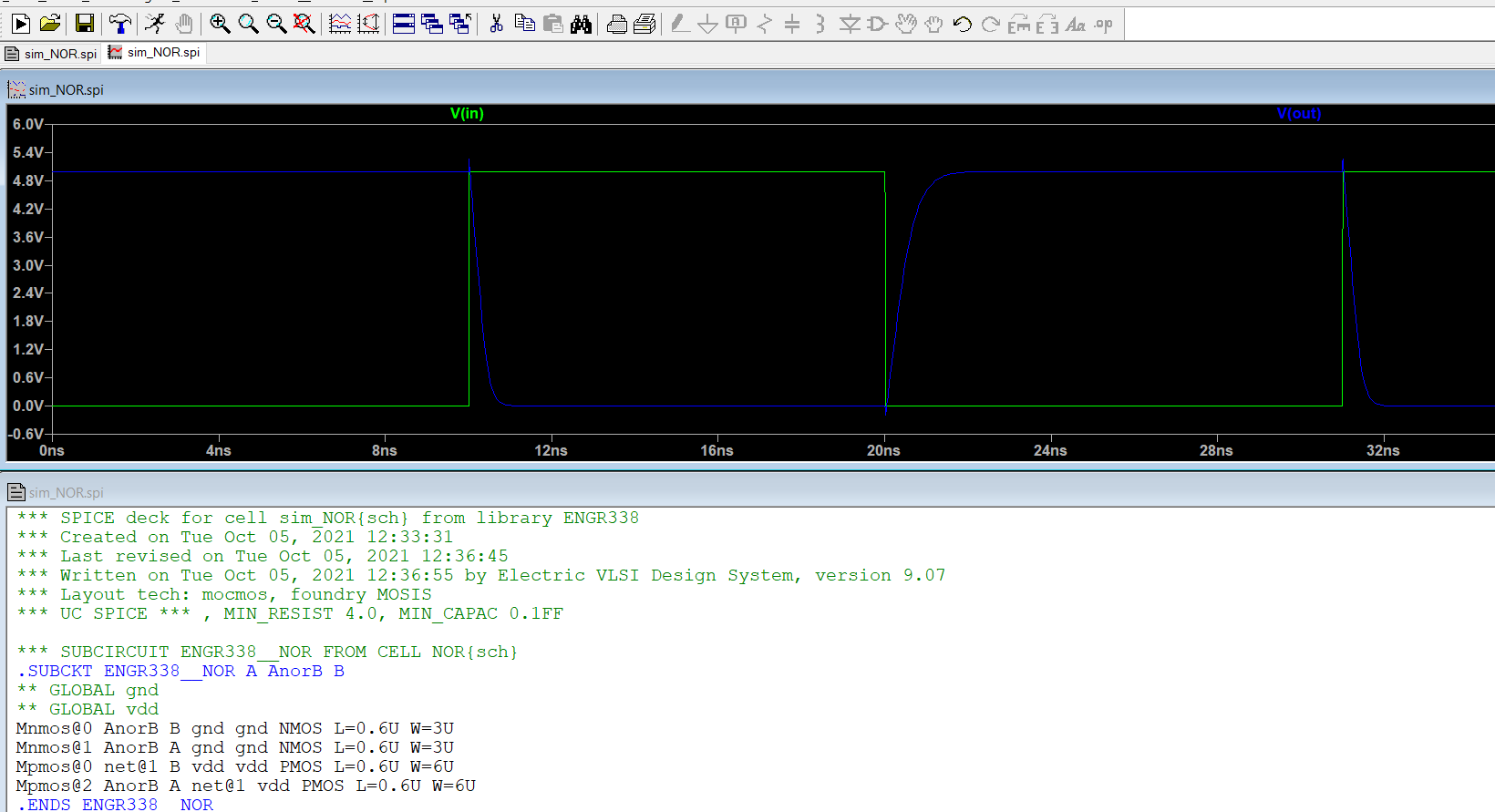

Figure 5: Shows the LTSpice

simulation of the NOR gate

Figure

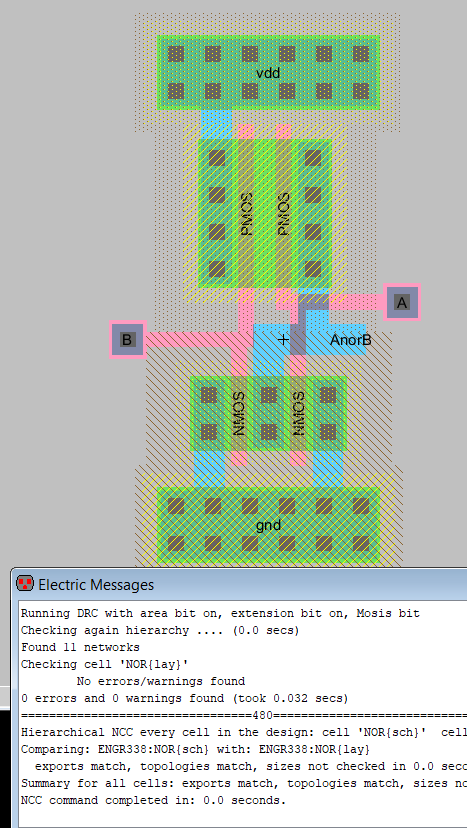

6:

Shows the layout of the NOR gate with no errors on the DRC and NCC

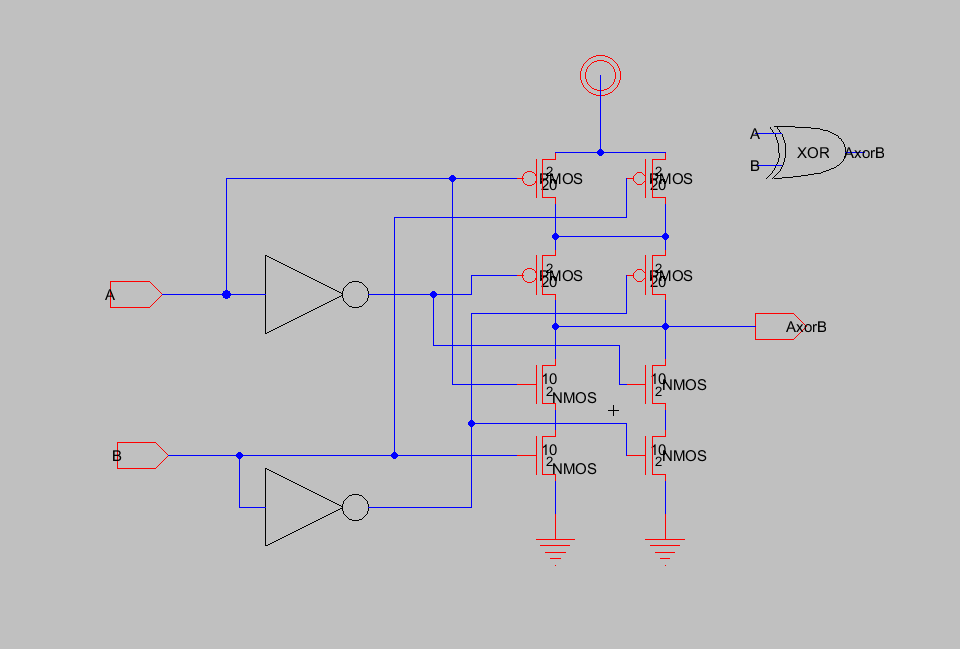

Task 3: Design,

simulate and layout an XOR gate

Figure 7: Shows the Schematic of the XOR gate

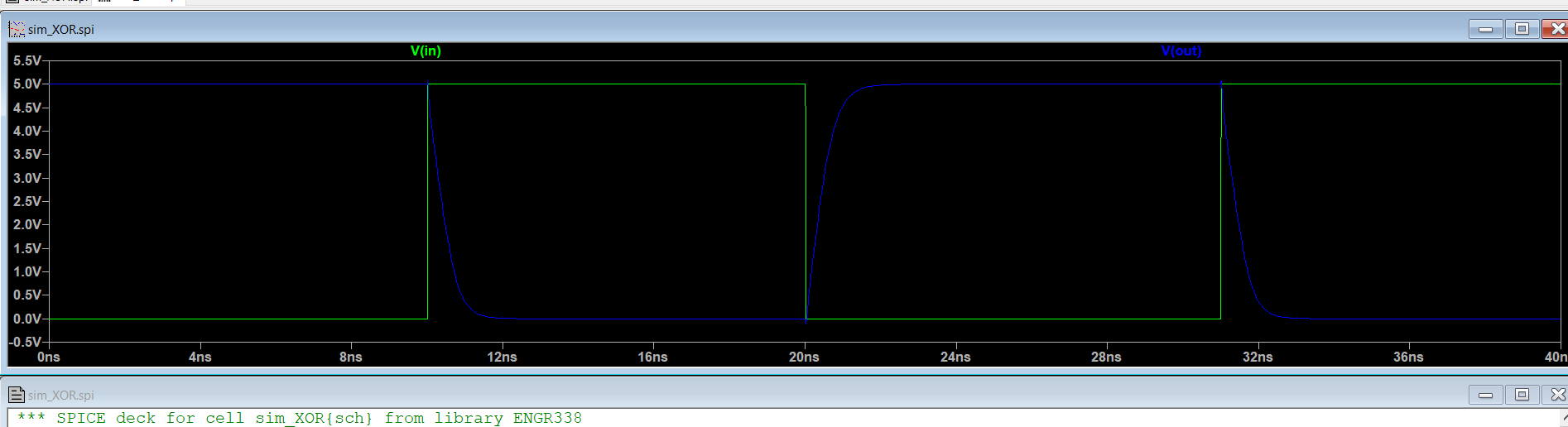

Figure 8: Shows the LTSpice simulation of

the XOR gate with two inputs

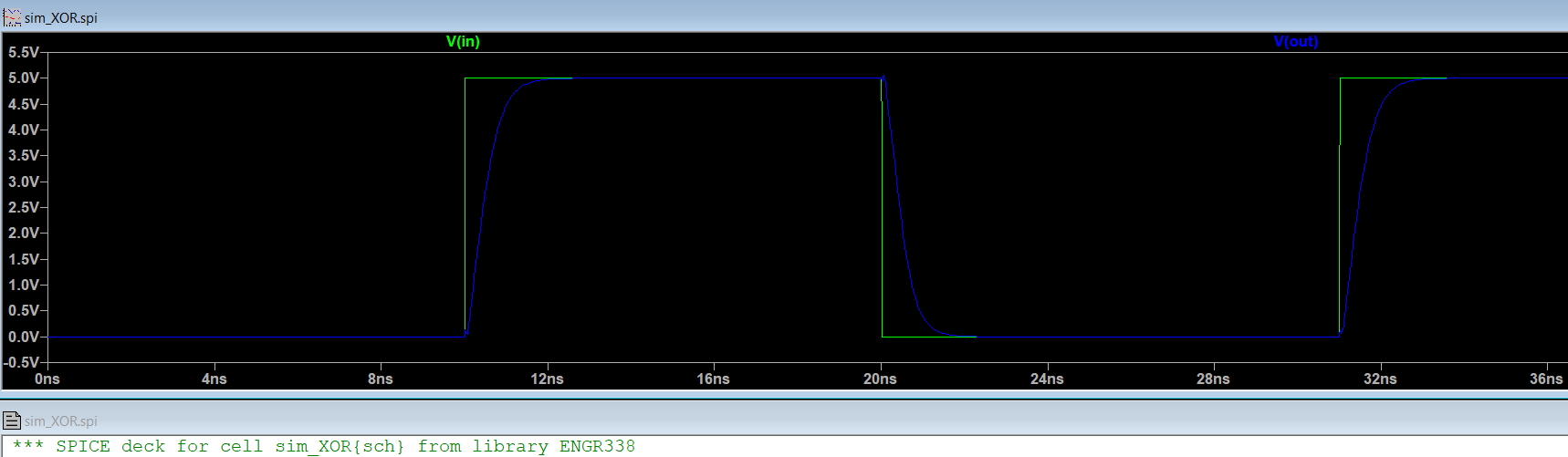

Figure 9: Shows the LTSpice simulation of

the XOR gate with 1 input grounded

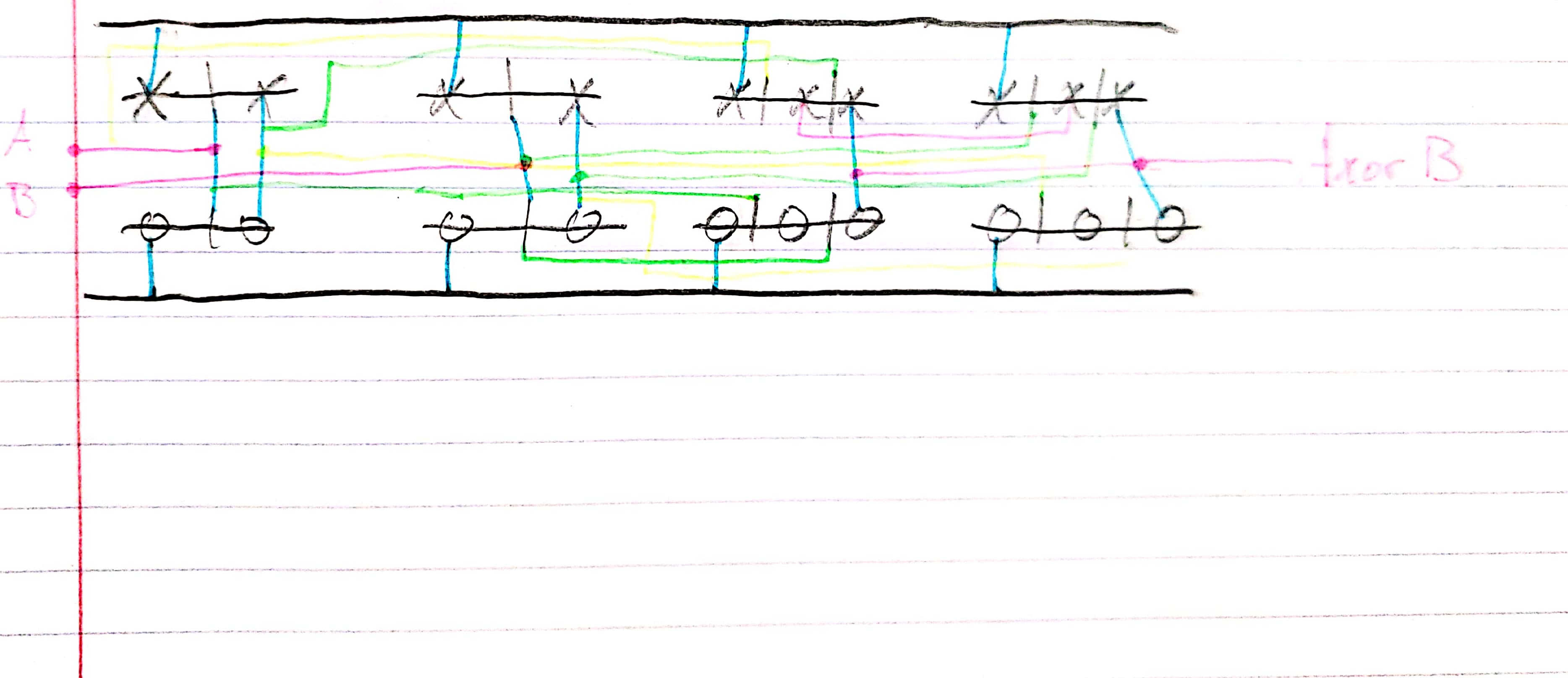

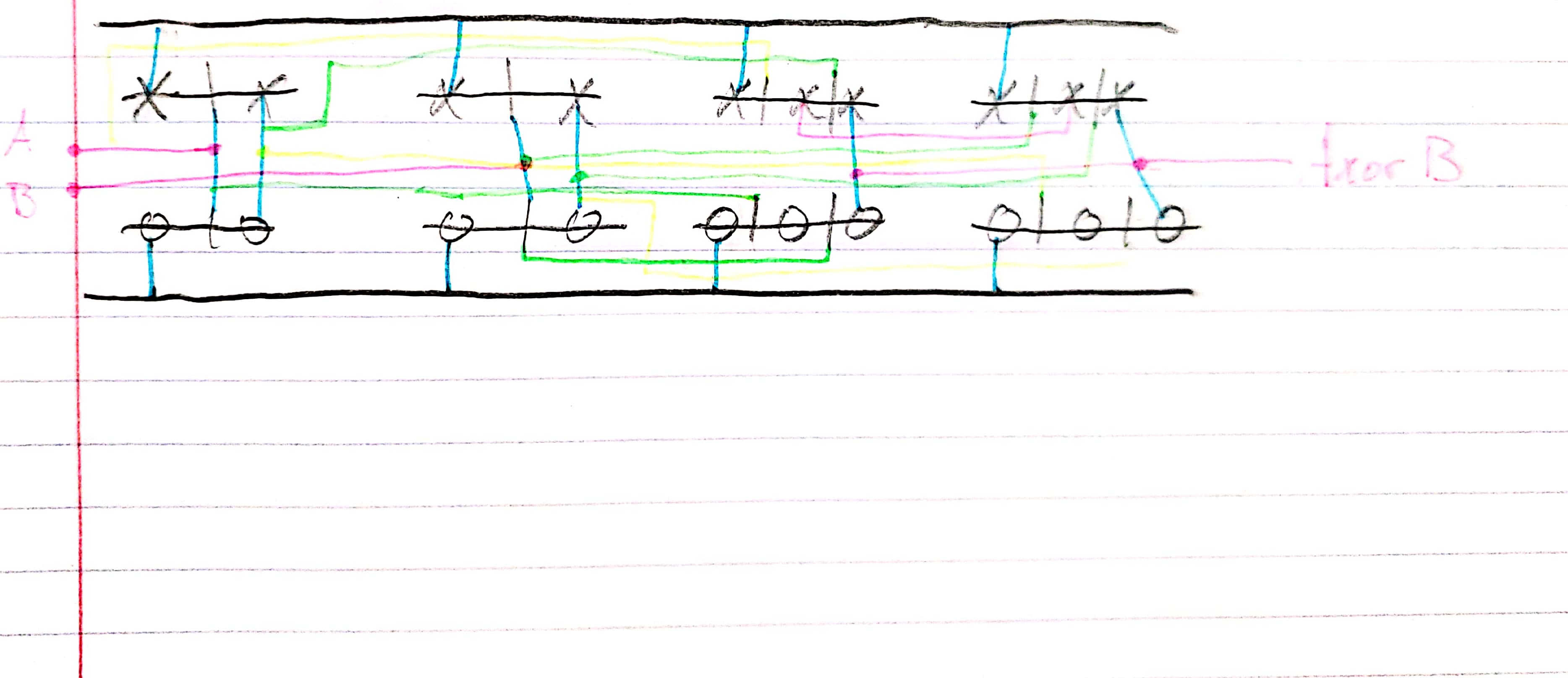

Figure 10: Shows the hand drawn stick diagram

of the XOR gate

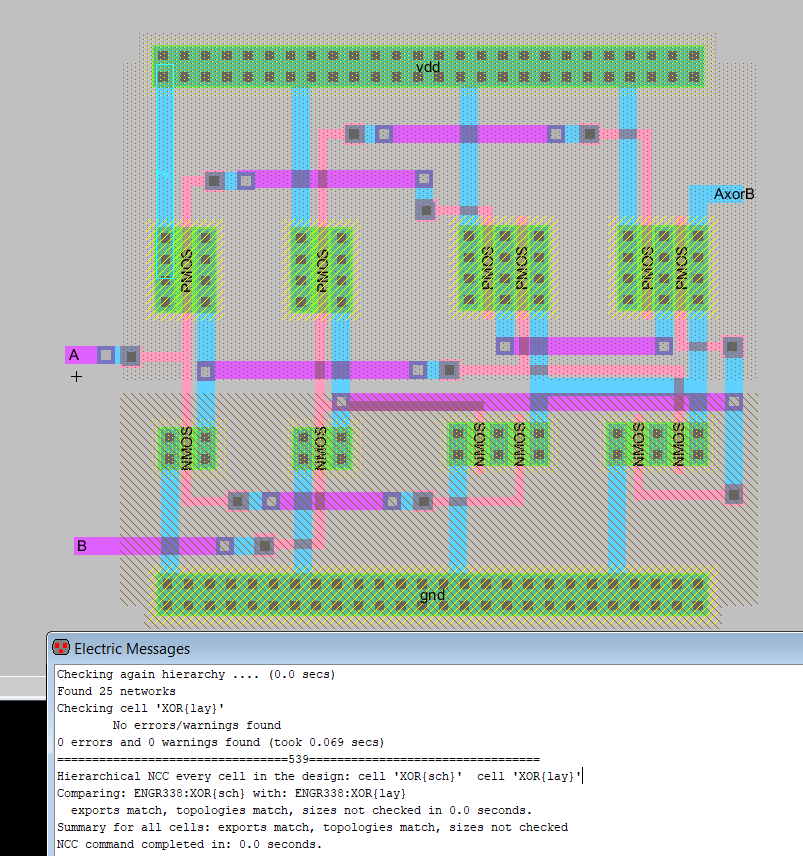

Figure 11: Shows the Layout of the XOR gate

with no errors from DRC or NCC

Task 4: Run

simulations to verify the driving capability of these two different

inverters

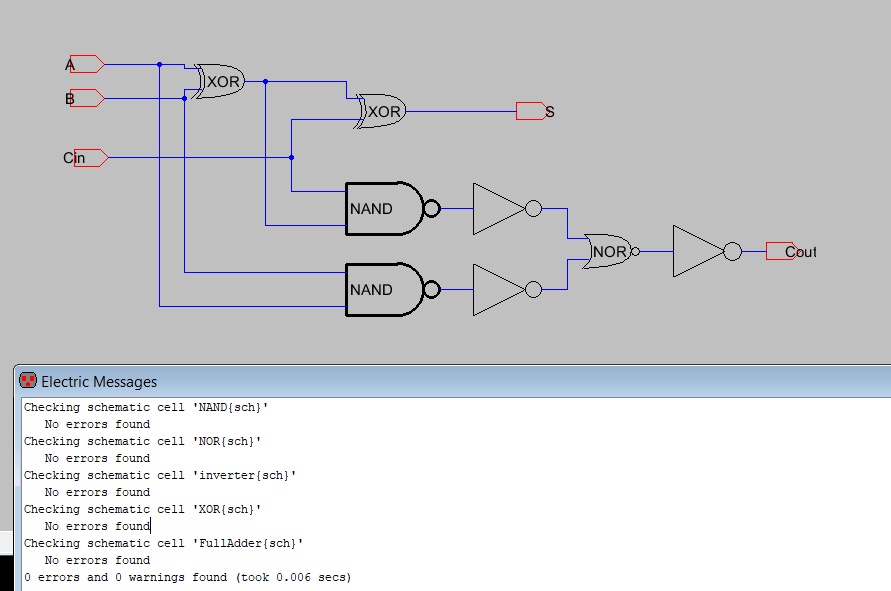

Figure 12: Shows theSchematic of the Full

Adder with no errors

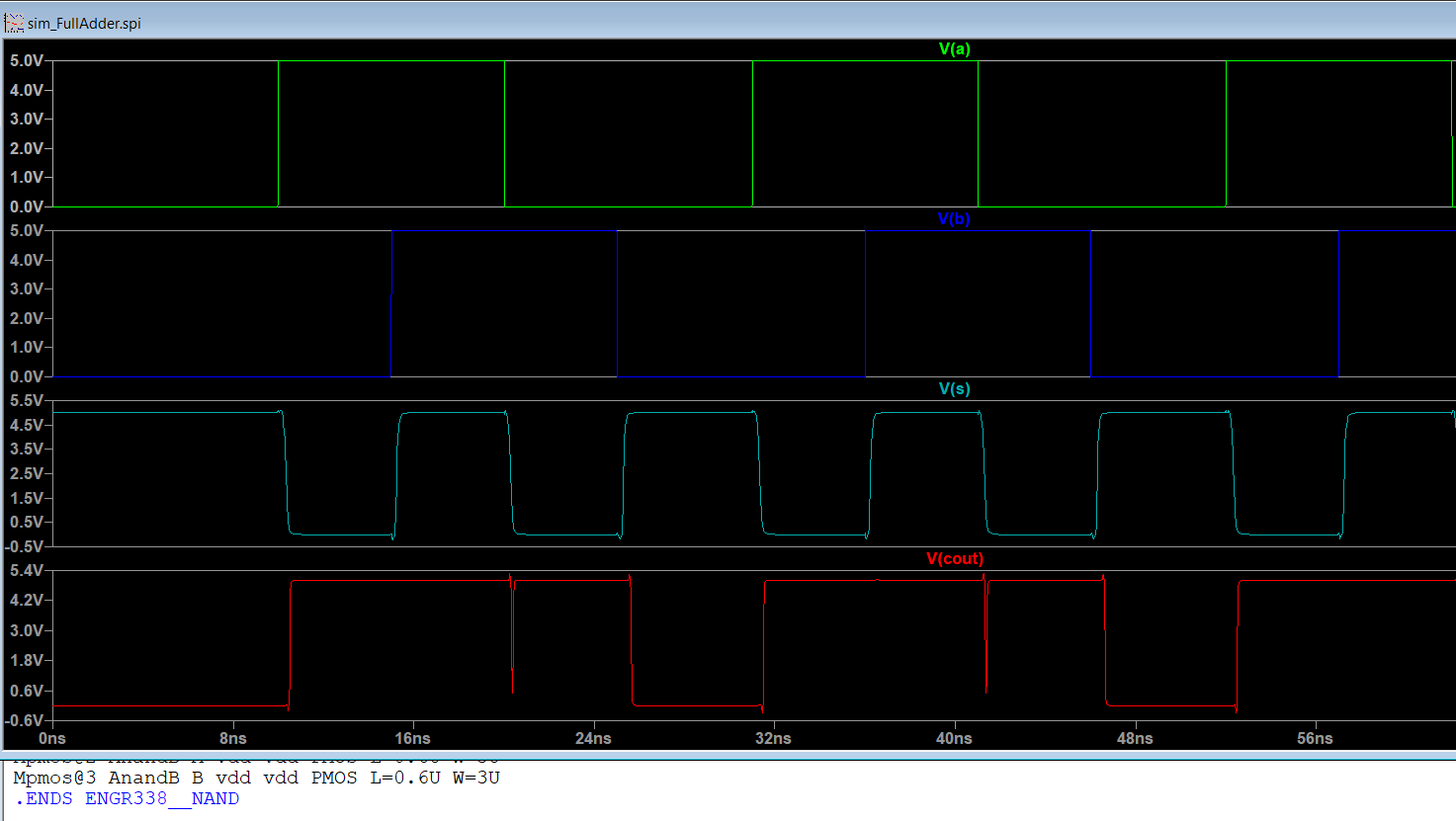

Figure 13: Shows the LTSpice simulation the

Full Adder with the carry in with a source

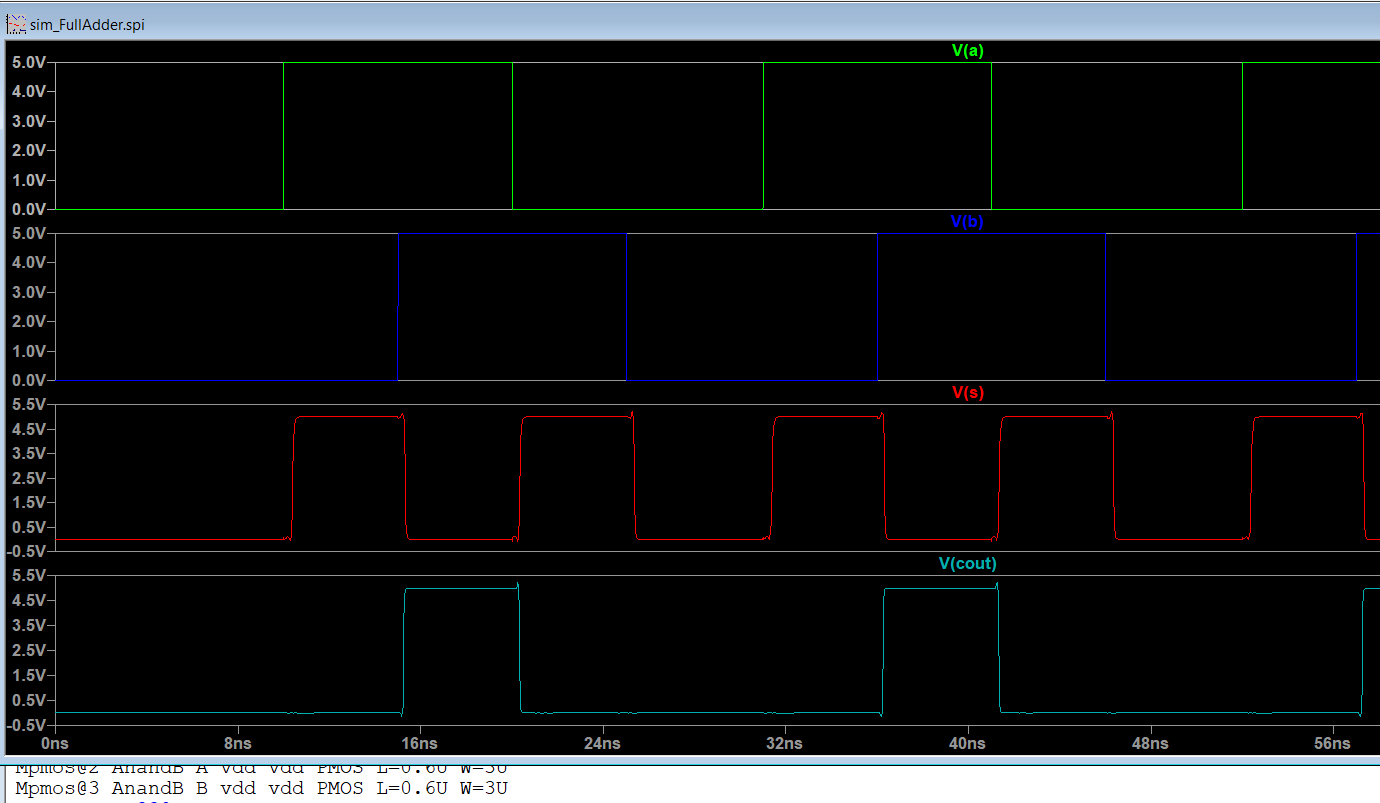

Figure 14: Shows the LTSpice simulation of

the Full Adder with the cin grounded

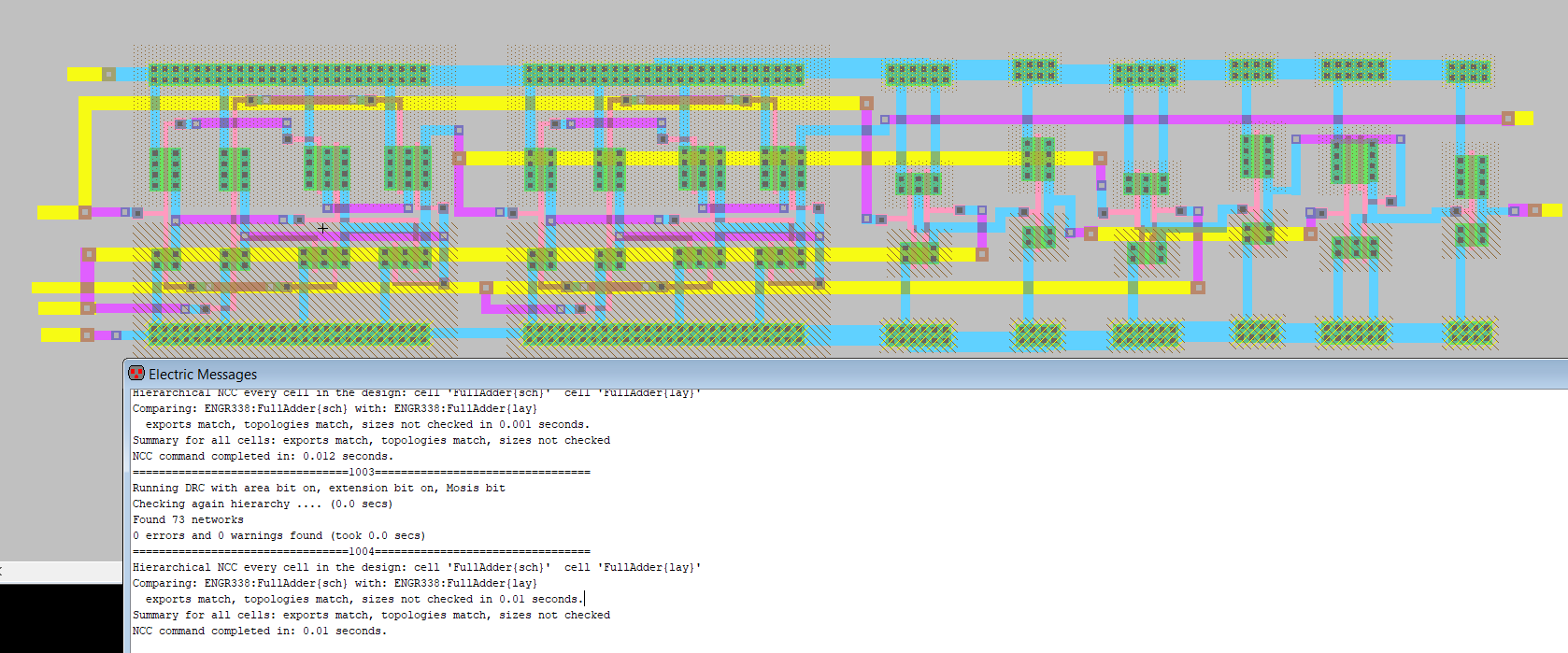

Figure 15: Shows the Layout of the Full Adder

fully connected and with no errors from DRC and NCC

5. Discussion

The lab was able to be successfully completed because we were able to

create the simulate and have no errors in the final layout of the Full

Adder. This lab took a while to complete becuase there were so many

little things that could be left out, or looked over, and cause errors.

This lab helped me get a better understanding of how all the parts of

Electric VLSI are able to work together inorder to create more complex

circuits.