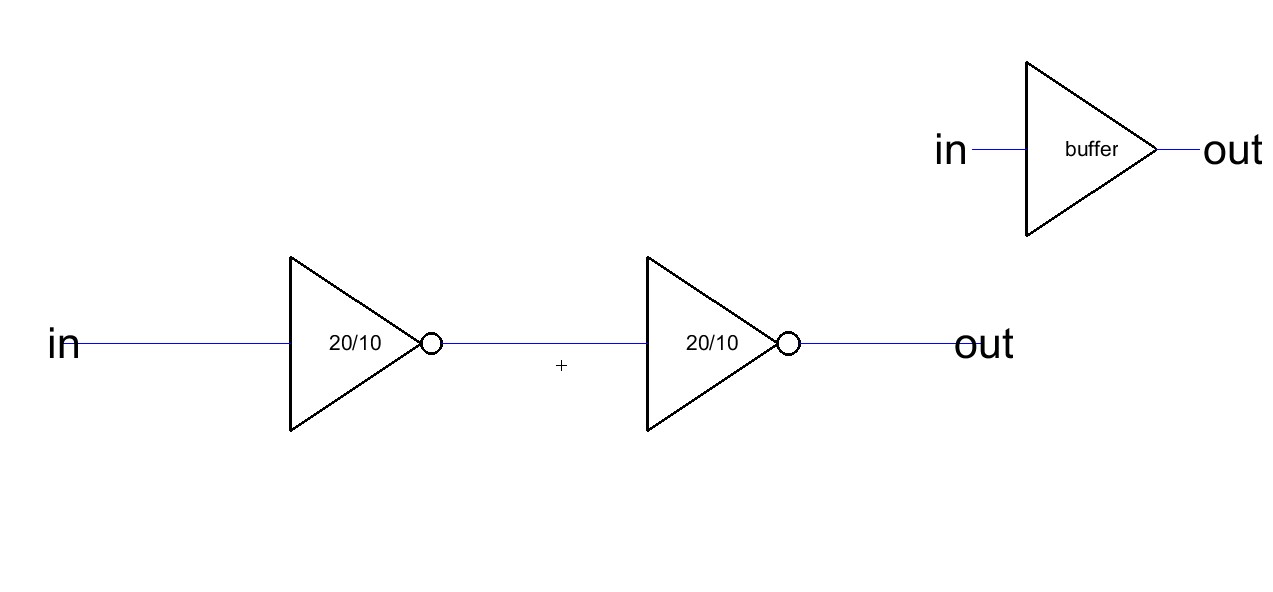

Here is the buffer schematic/symbol:

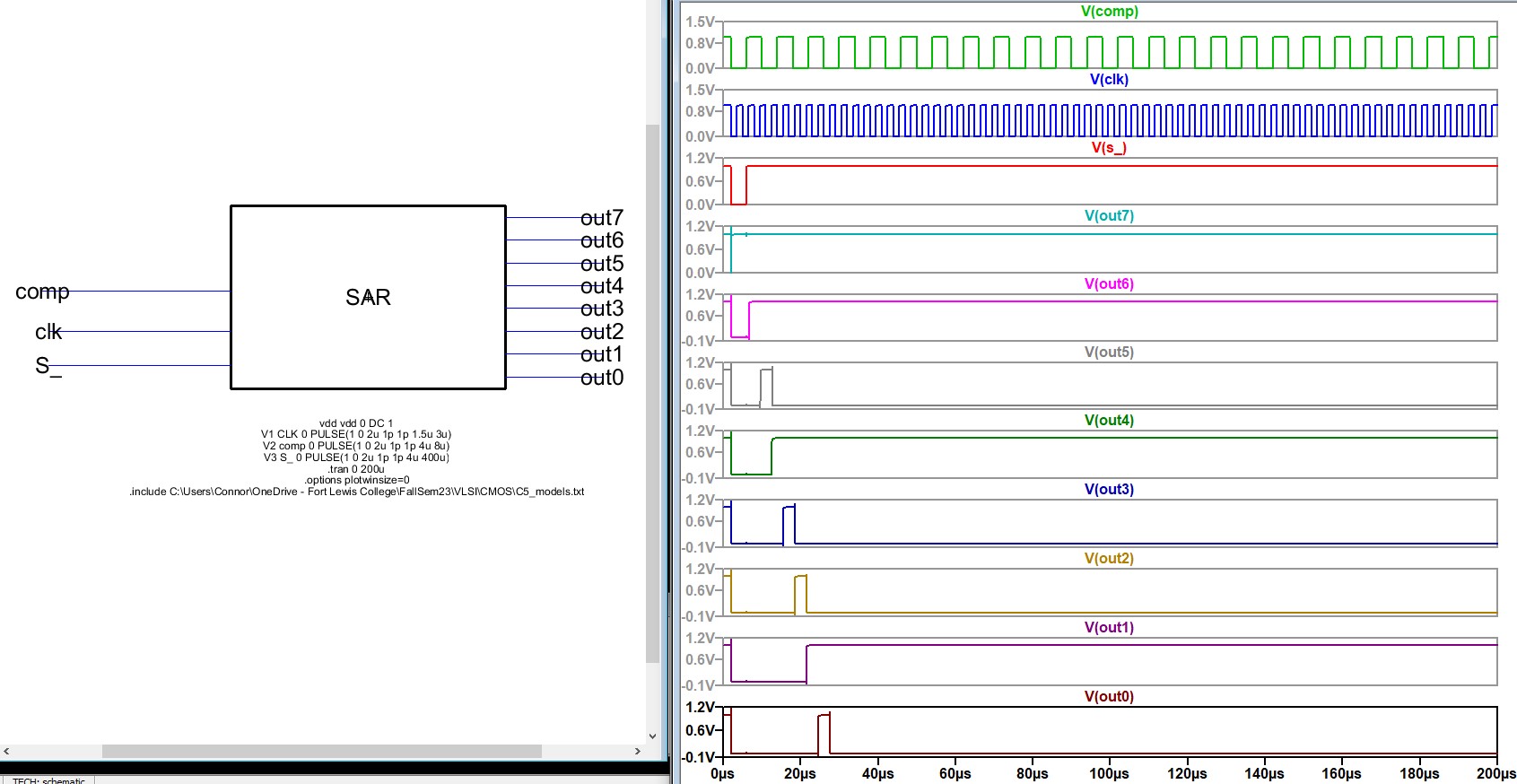

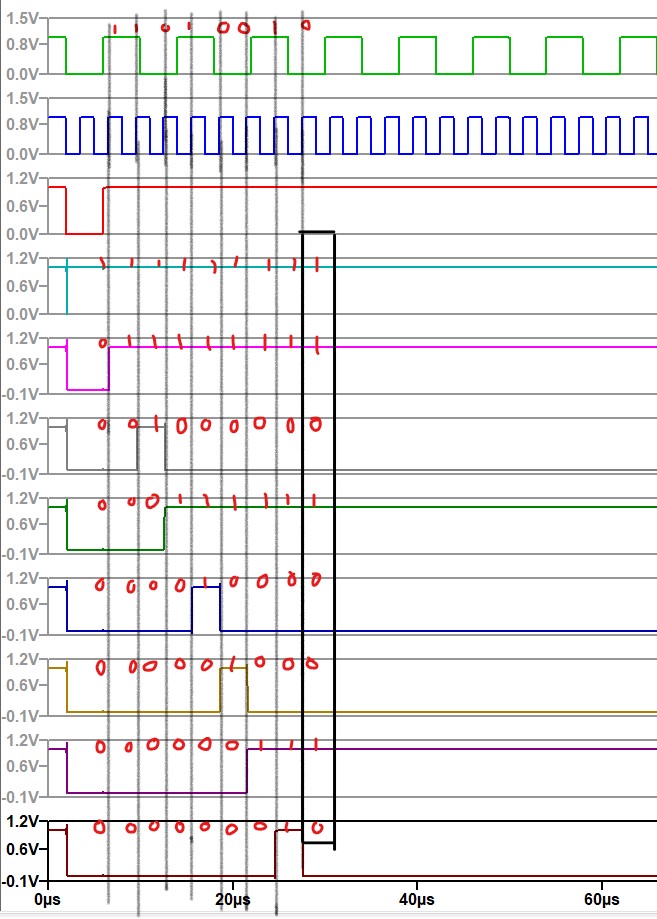

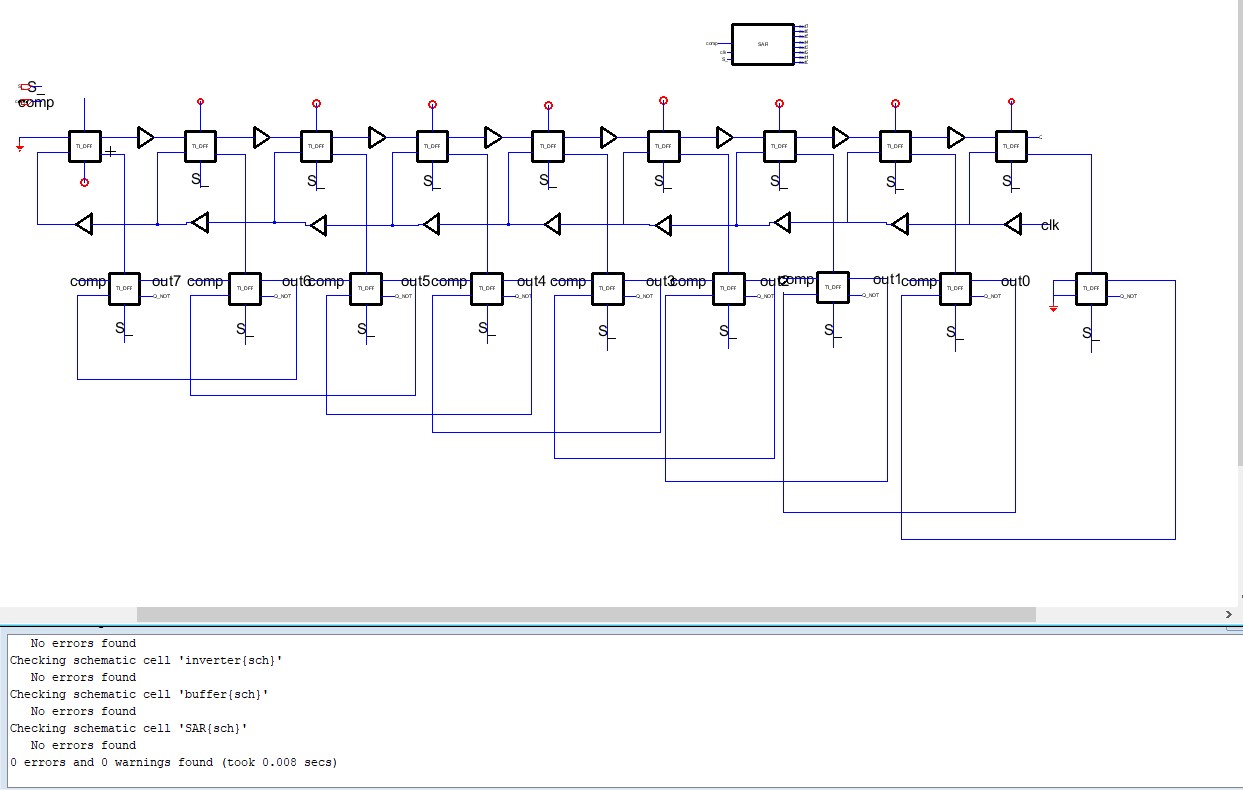

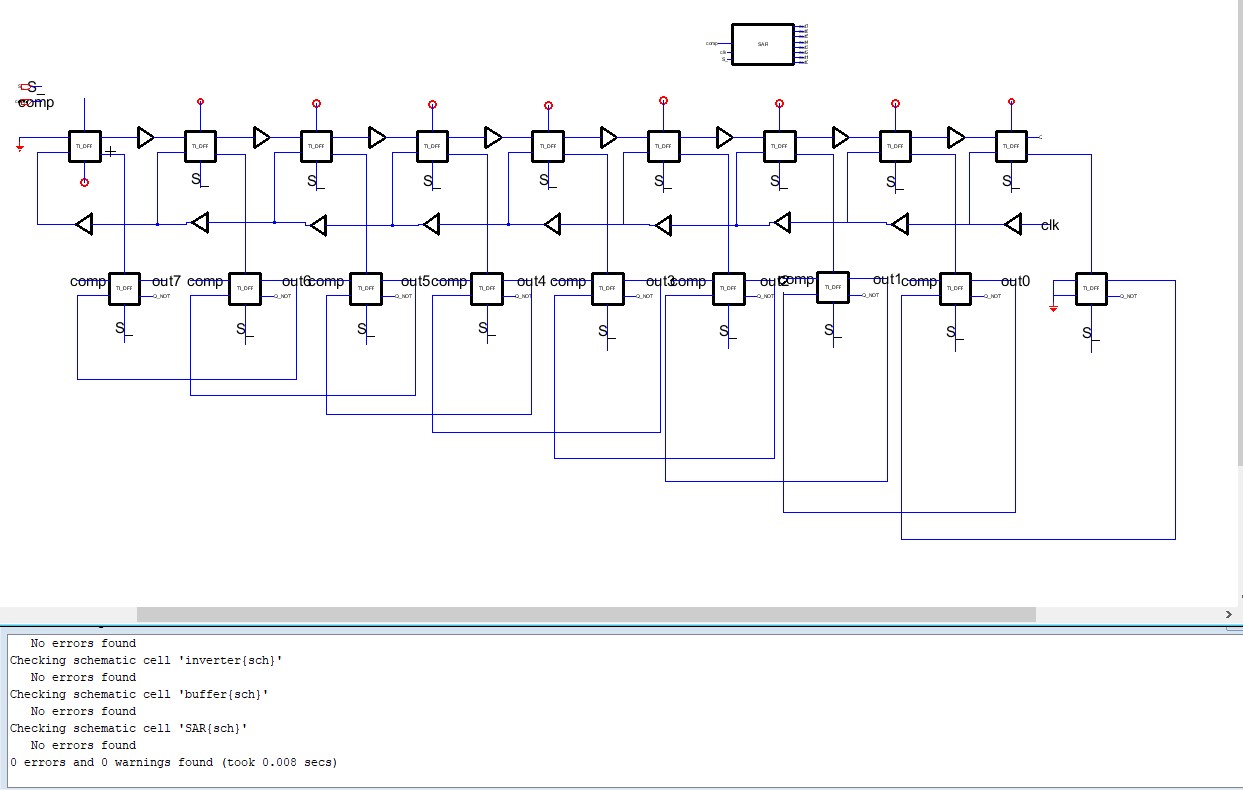

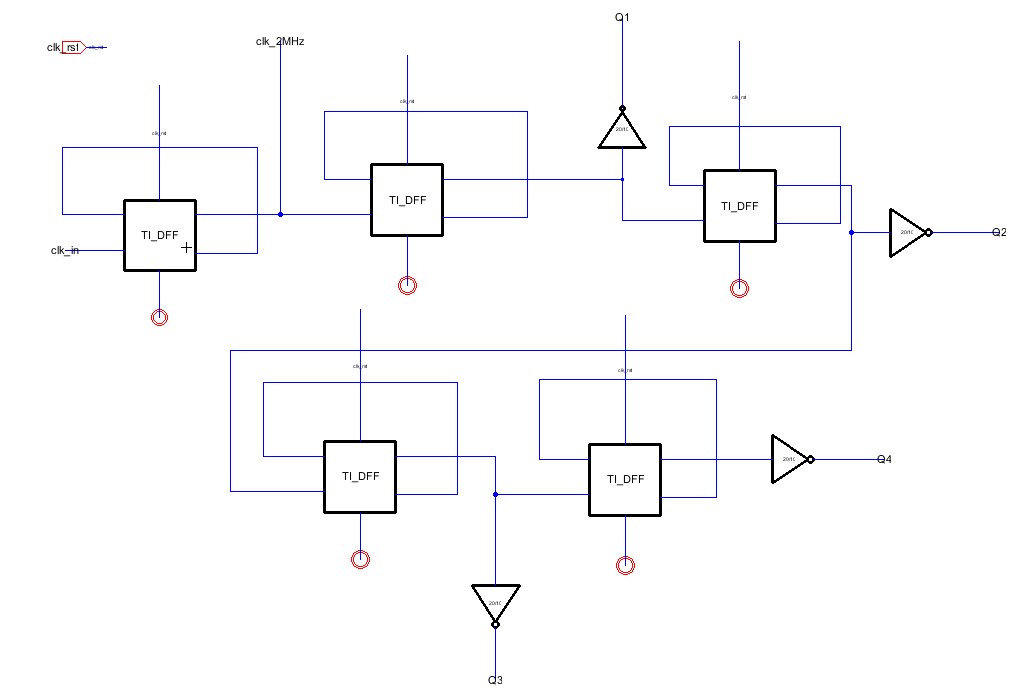

Here is the SAR schematic/symbol:

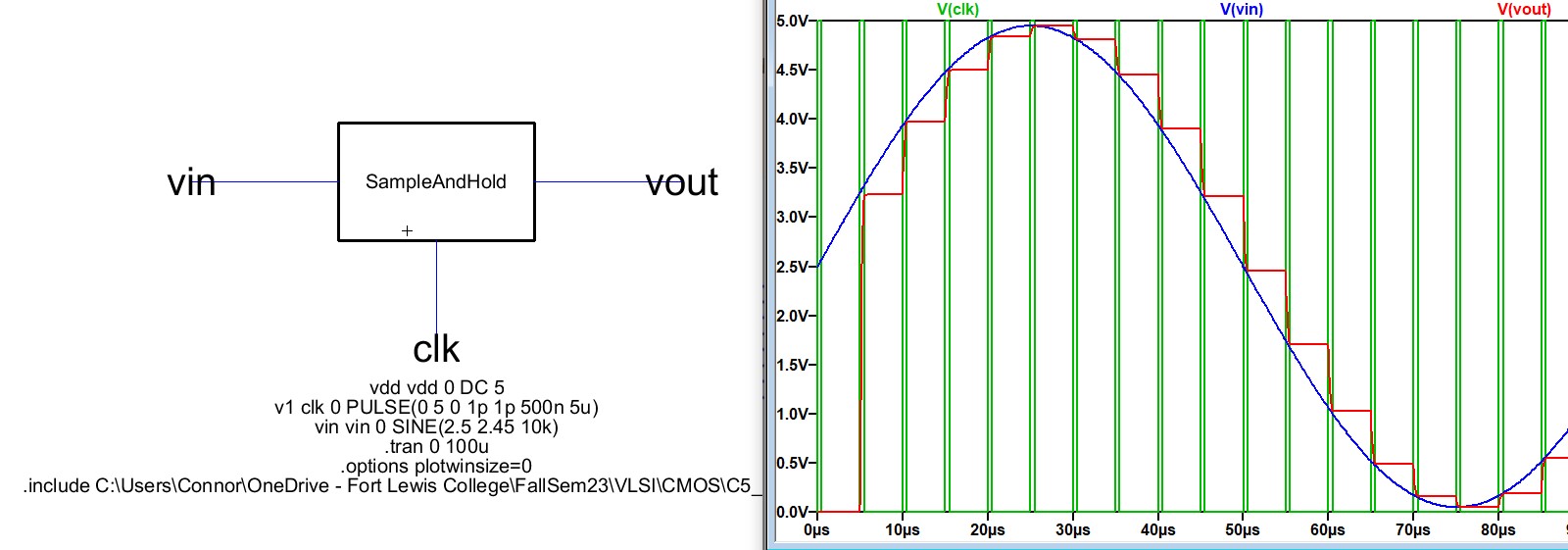

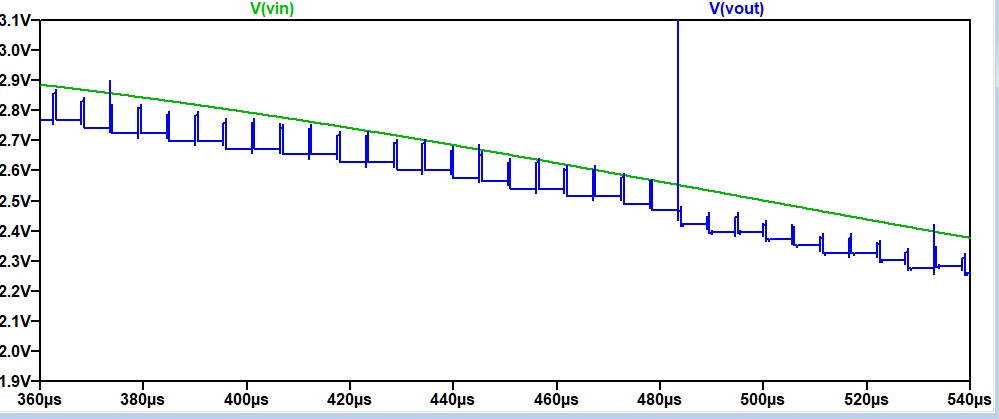

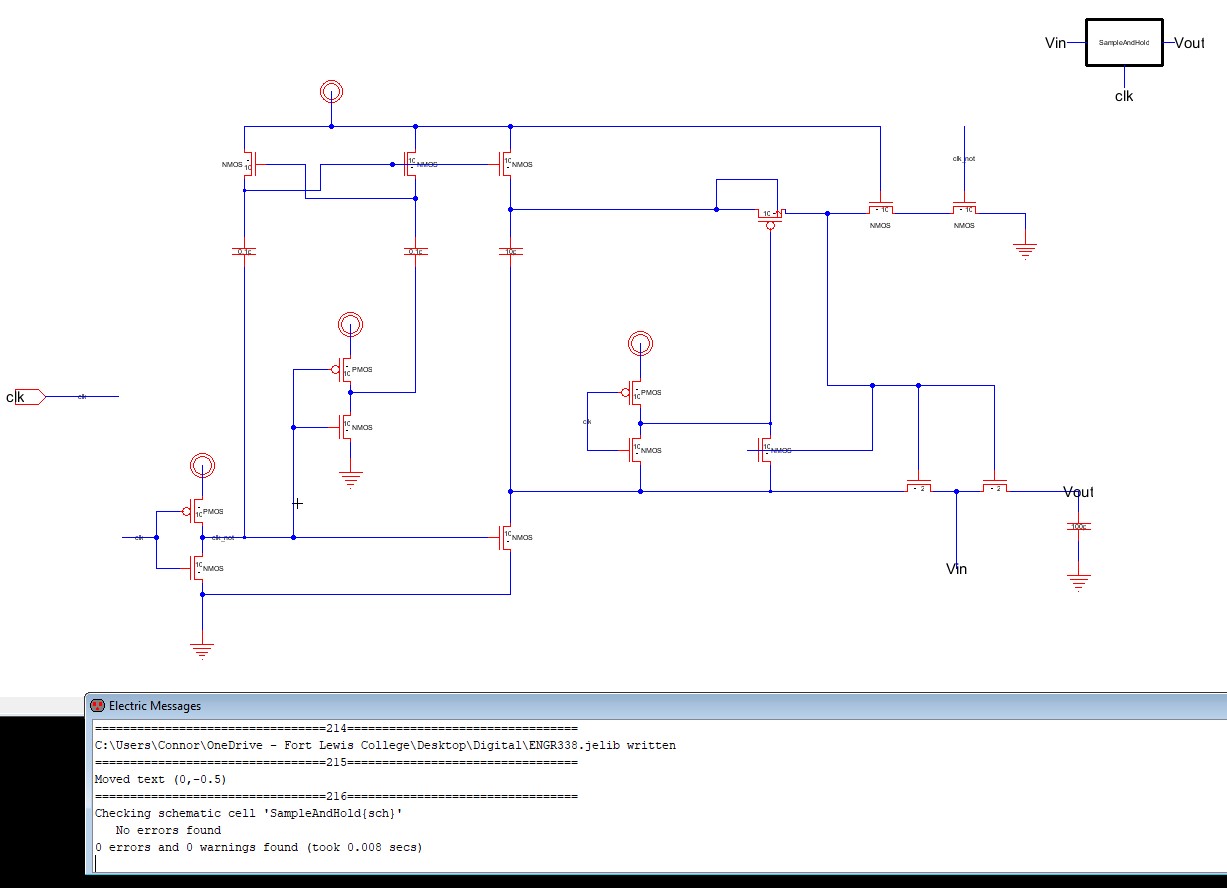

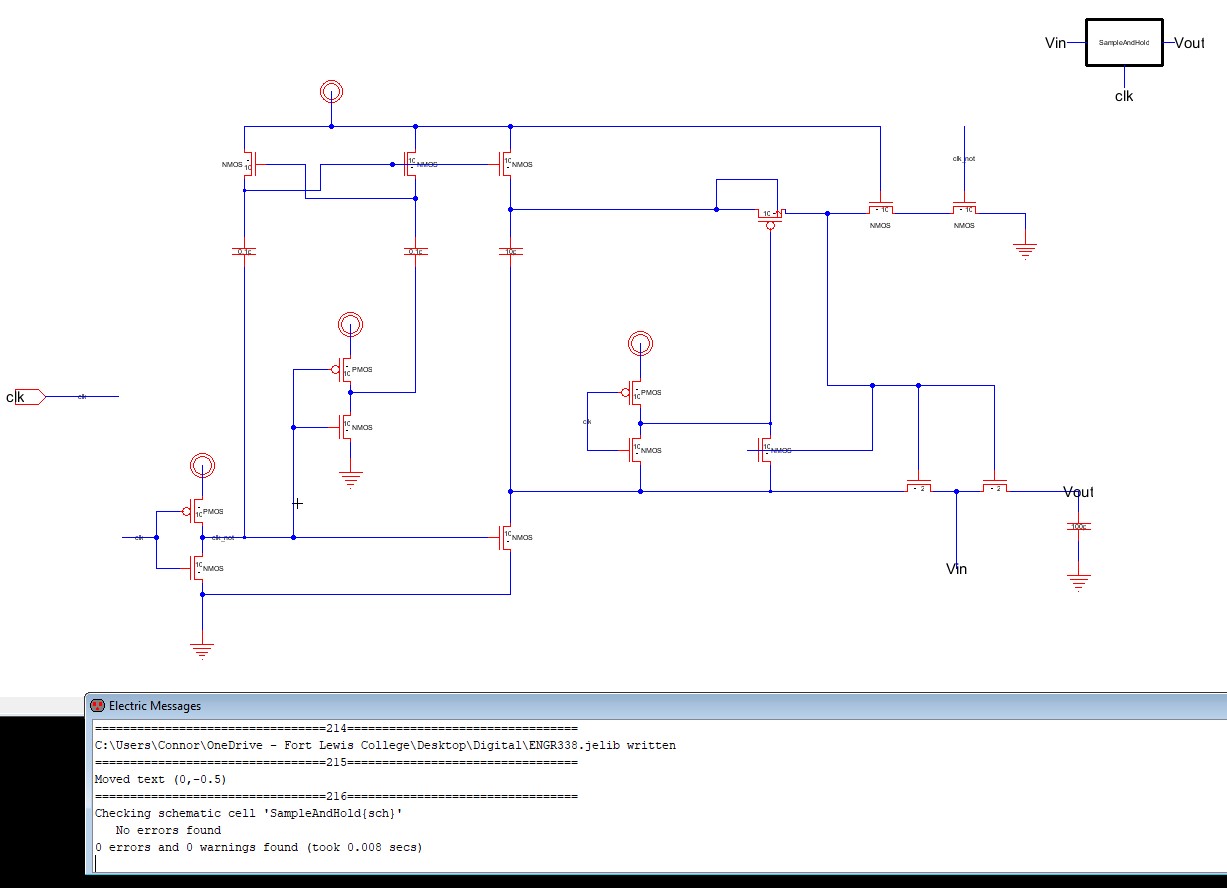

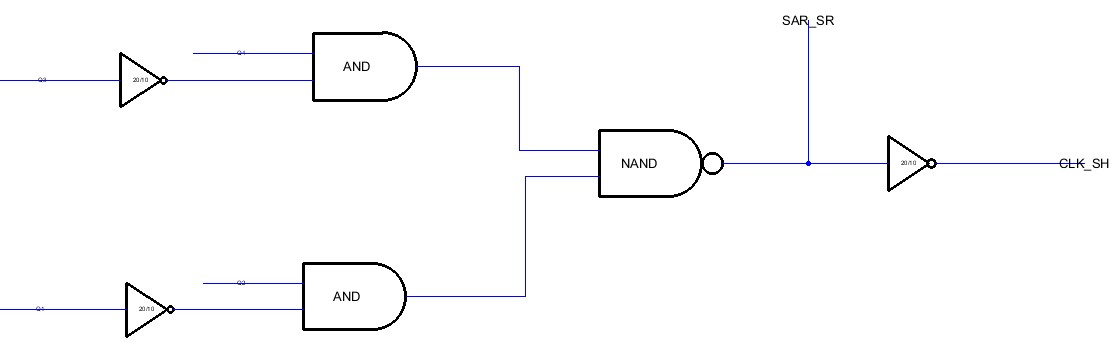

Here is the Sample and Hold schematic/symbol:

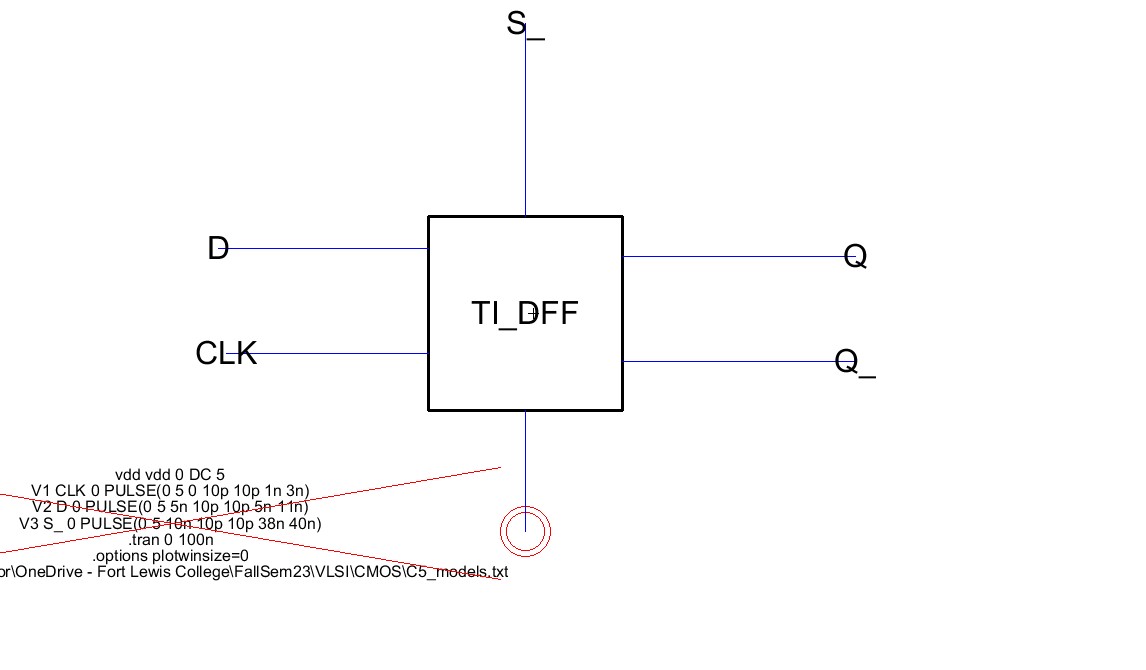

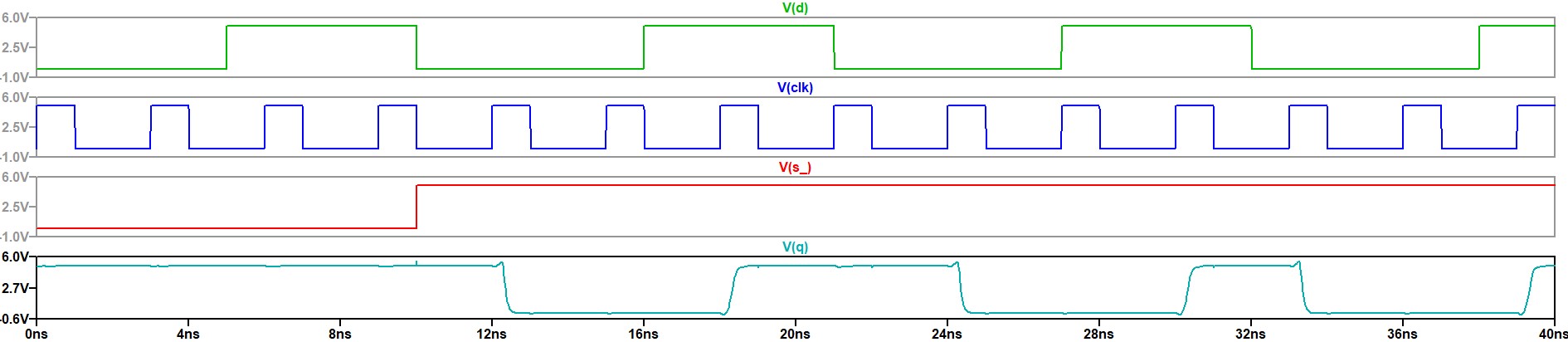

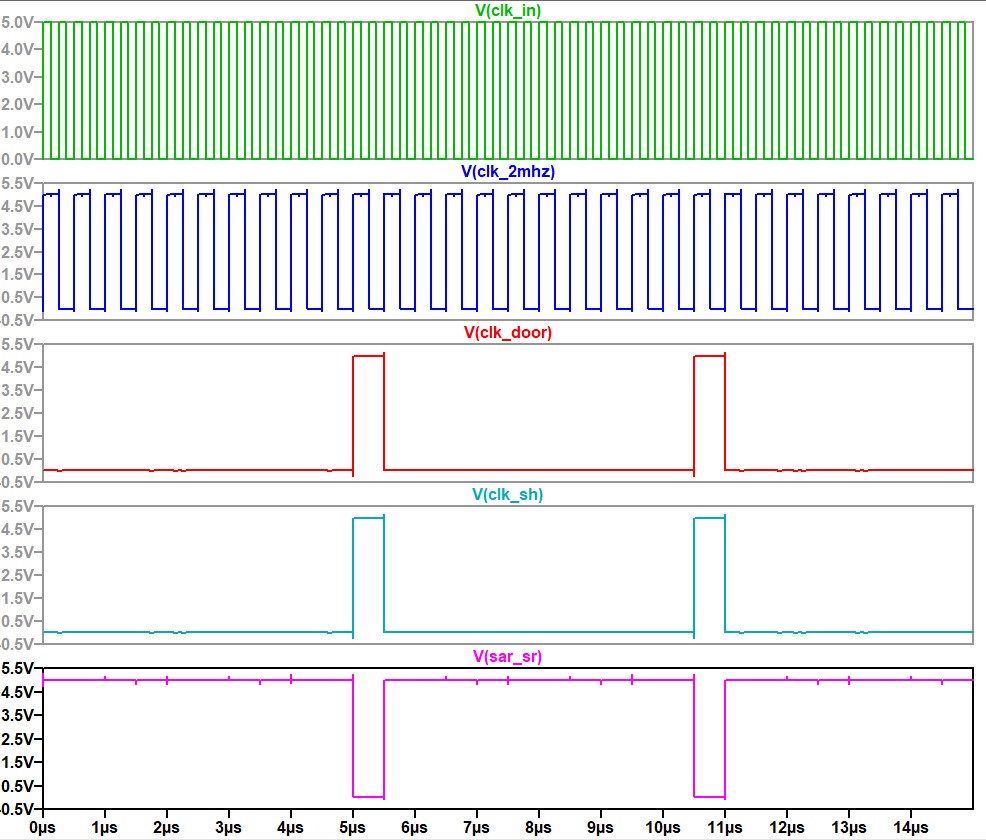

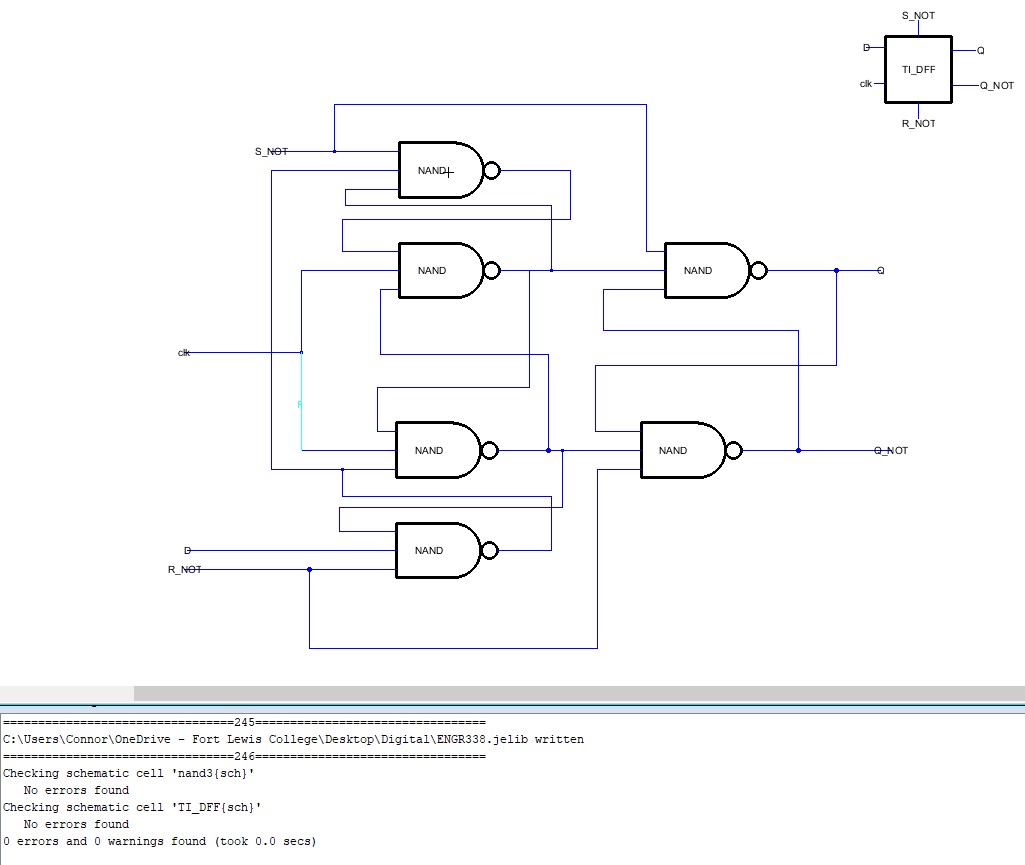

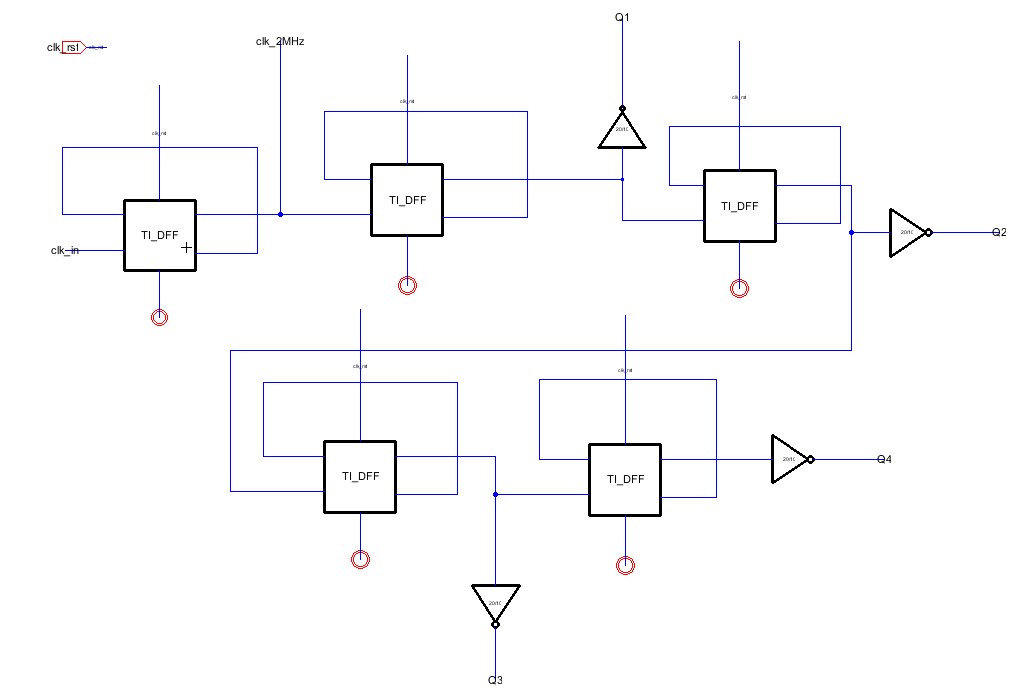

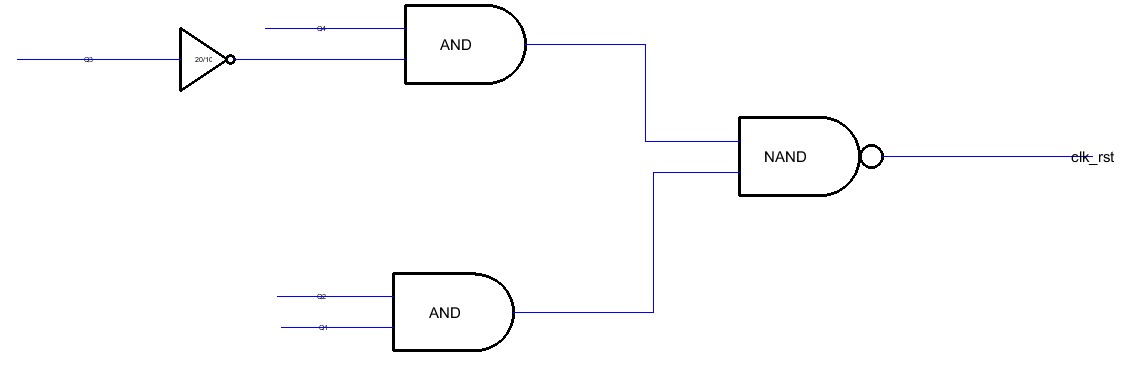

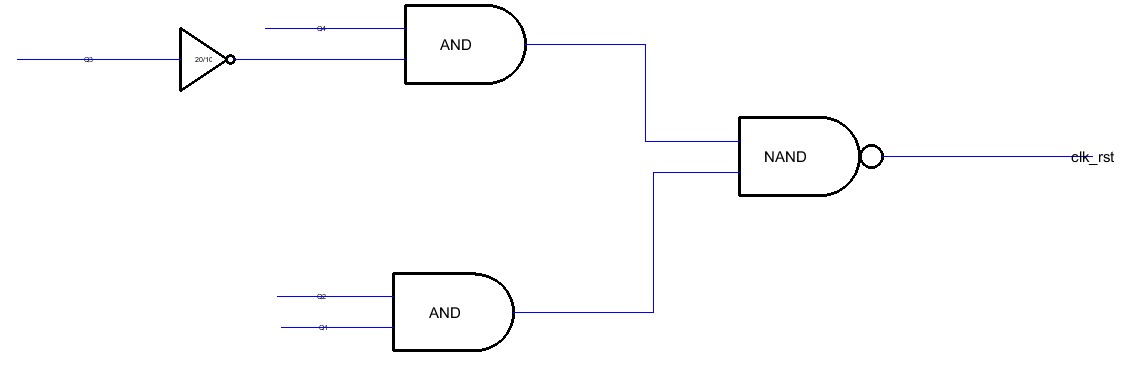

Here is the schematic for the Clock Register:

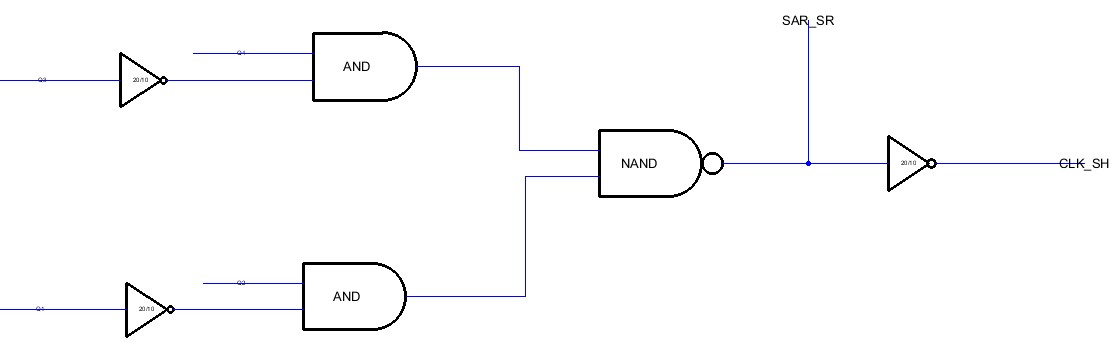

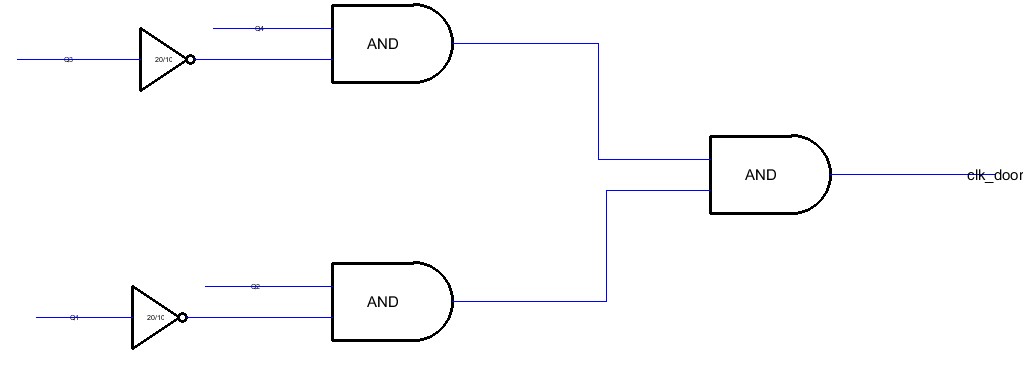

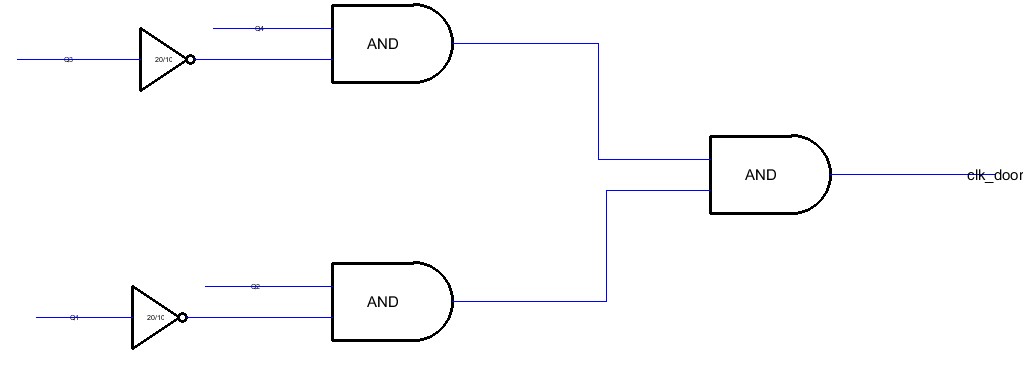

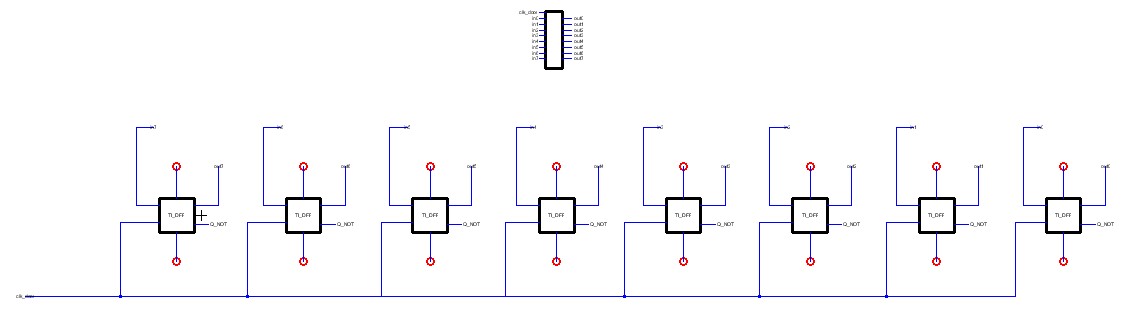

Here is the Door Register Schematic:

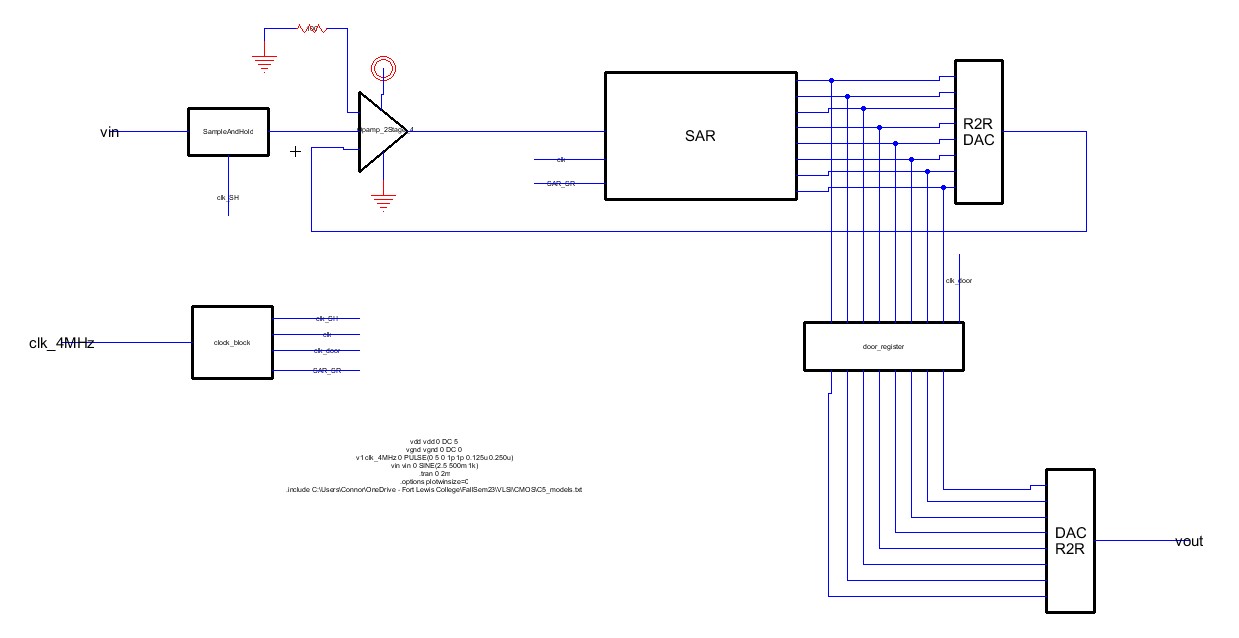

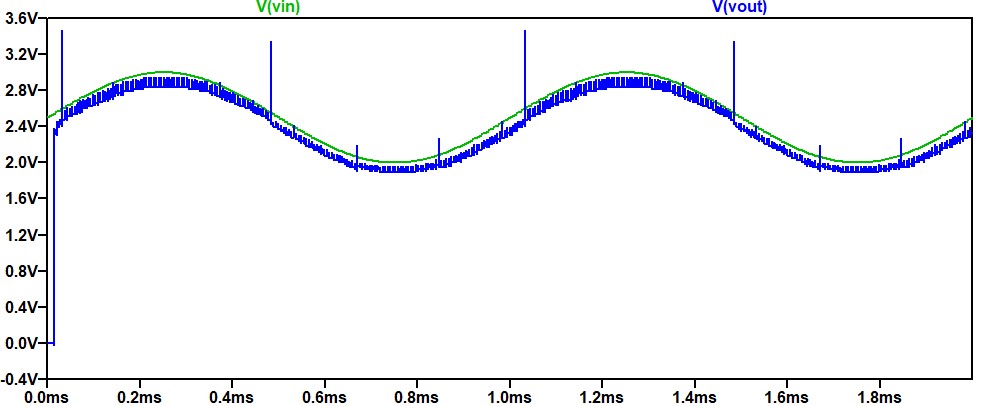

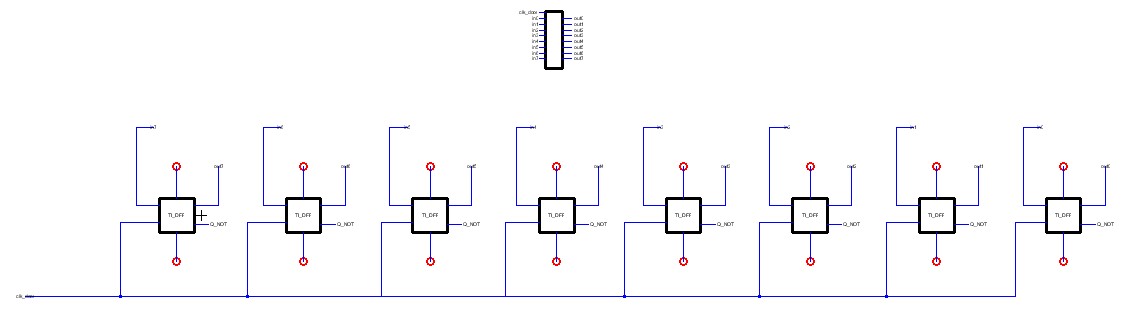

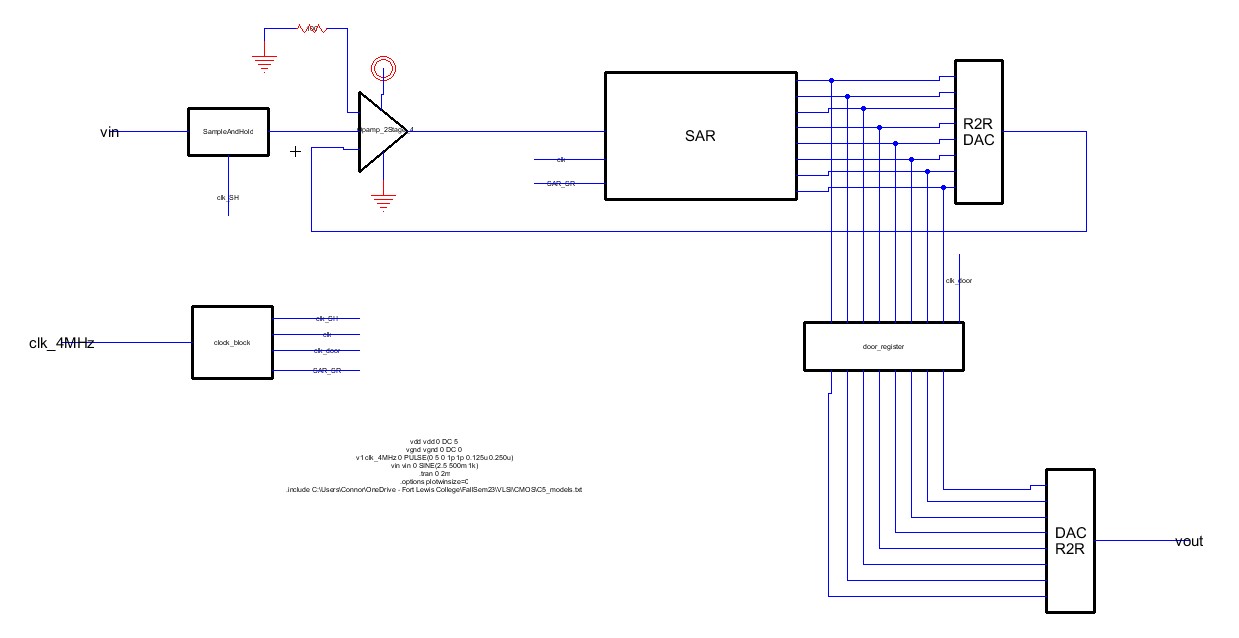

With all of the components together, we can finally build the 8-bit SAR ADC: