CE433 Embedded Systems

Tutorial 5: Sequential Circuit

Name: Audra Benally

Email: albenally1@fortlewis.edu

1. Title: Sequential Circuit

2. Introduction: This tutorial covered sequential circuits. This

included shift registers, counters and other intricate logic sequences.

3. Materials and Methods:

Materials:

- Computer

- Vivado Software

- GVim Software

Methods:

In the first task two different

equations were derived from the given truth table. From the equation, a

sequential circuit is drawn. For the next task, two methods of

implementing the circuit were simulated. For the 3rd task, four

different shift registers were shown with various input and output

types. In the 4th task, a counter module was chosen from the given

options and simulated. In the last task, verilog files are derived from

a sequential circuit diagram and simulated.

4. Results:

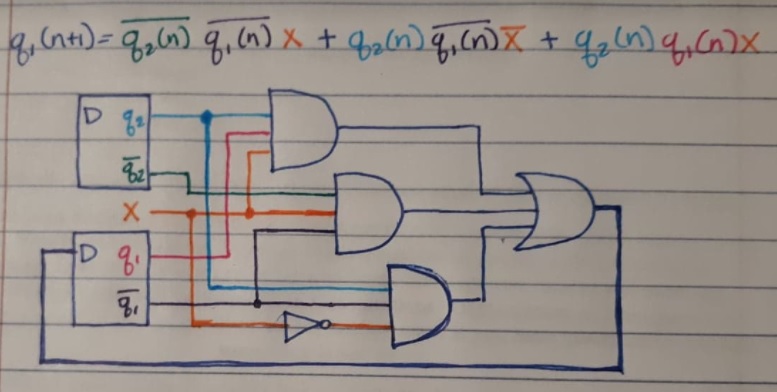

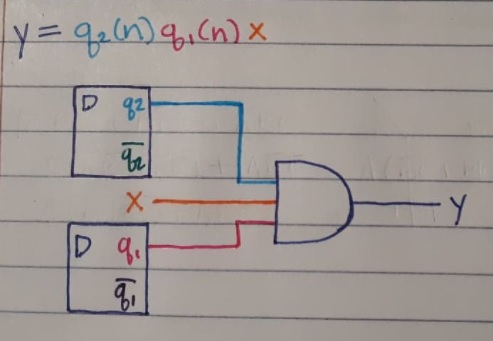

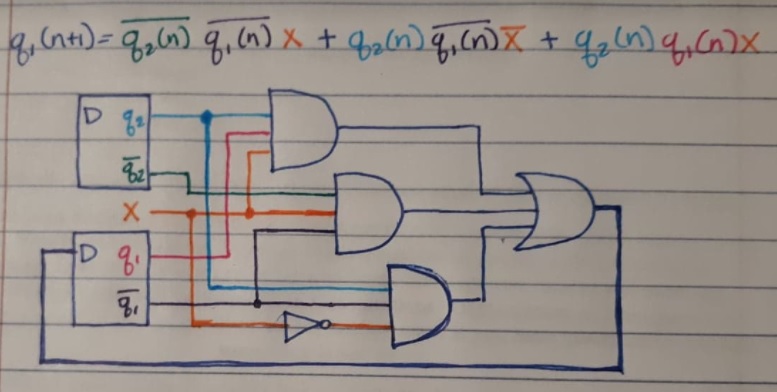

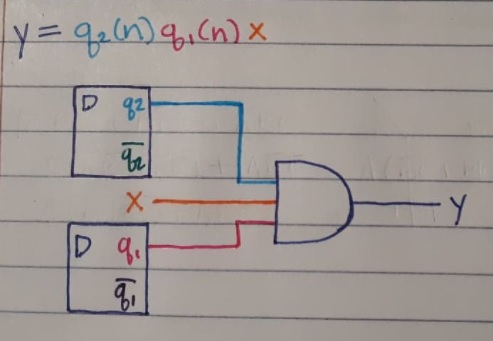

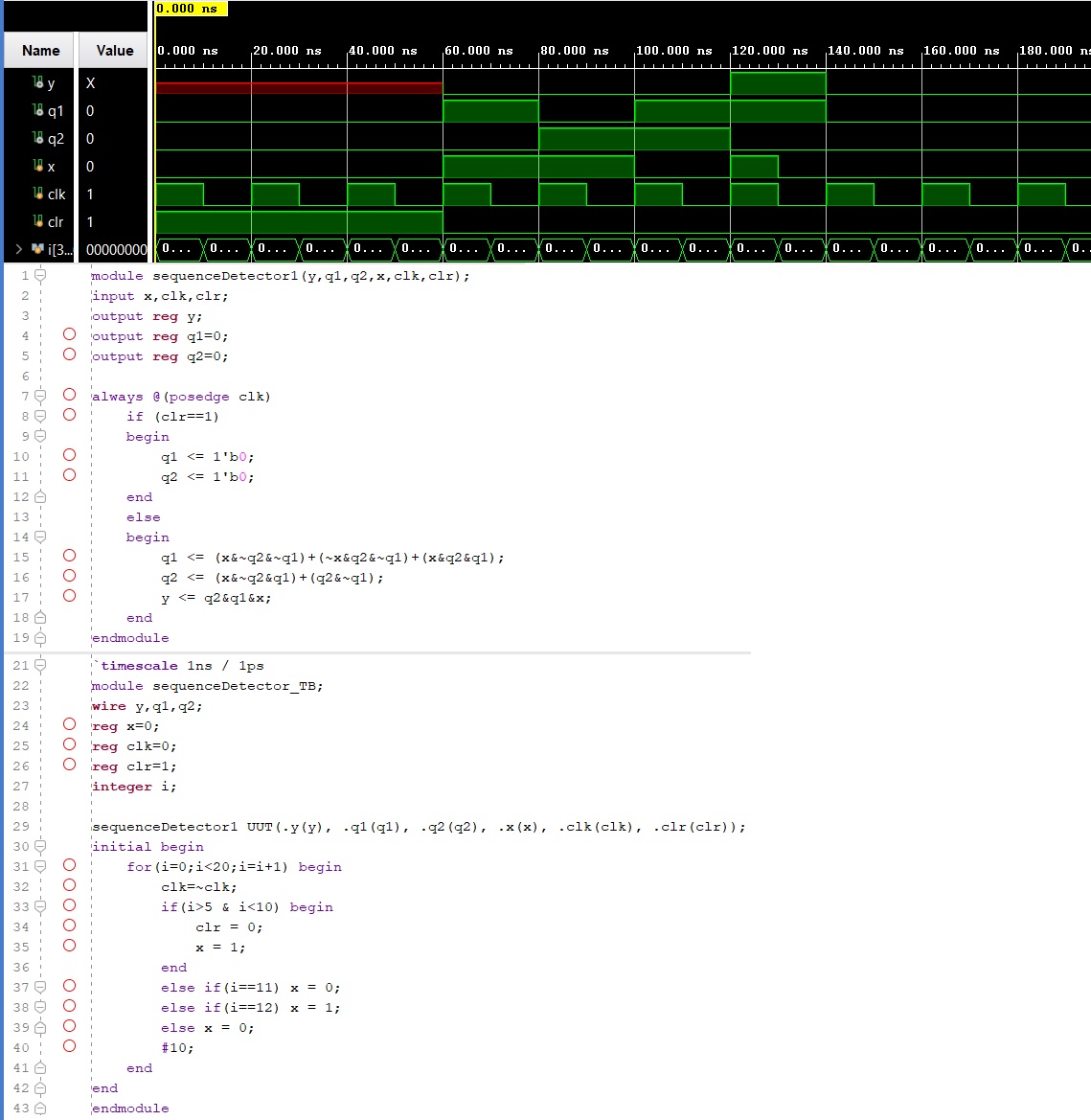

Task 1: Find the logic equations

for q1(n+1) and y from the state table then draw the sequential

circuits.

Figure 1. q1(n+1) equation and sequential circuit.

Figure 2. y equation and sequential circuit.

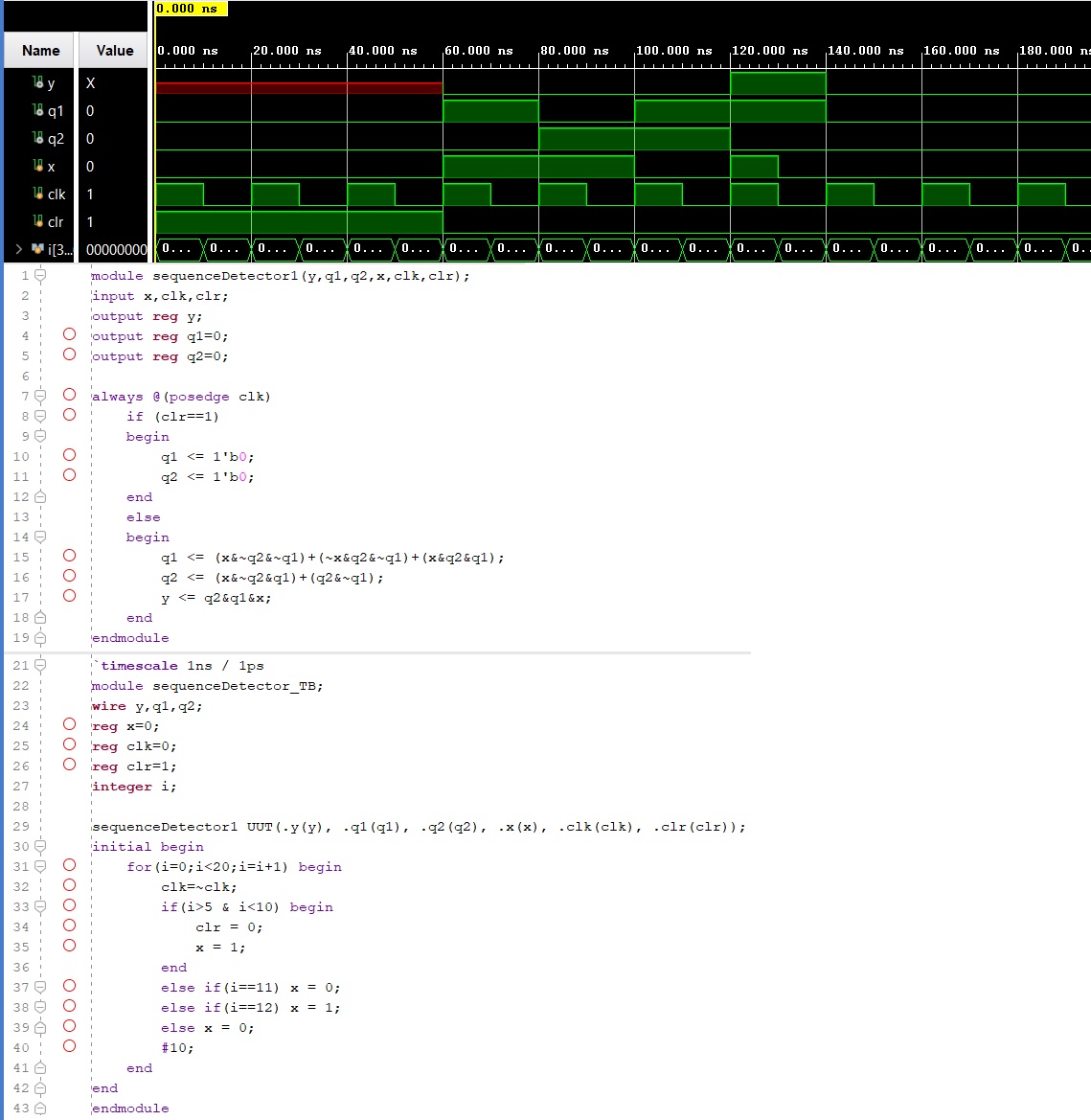

Task 2. Repeat the work in section 3 using two methods.

Figure 3. Sequence detector 1 with data flow method.

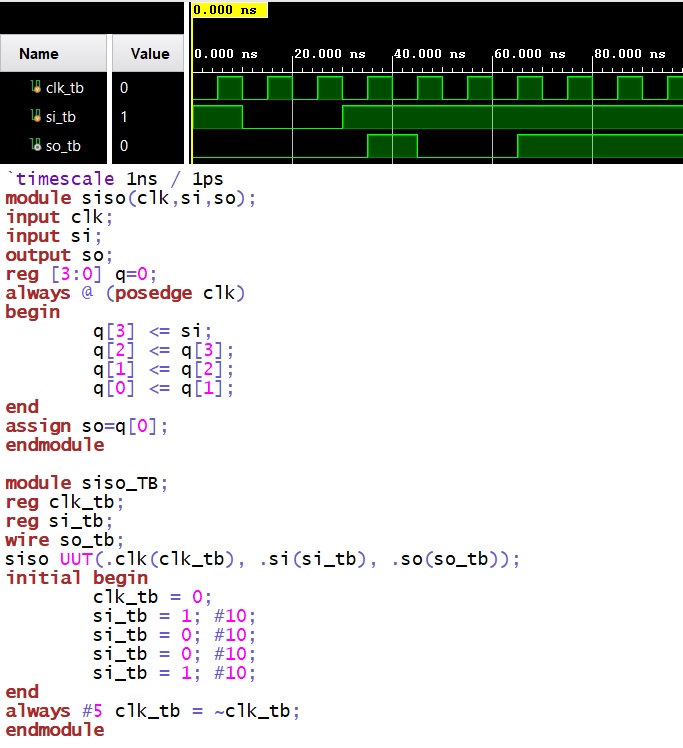

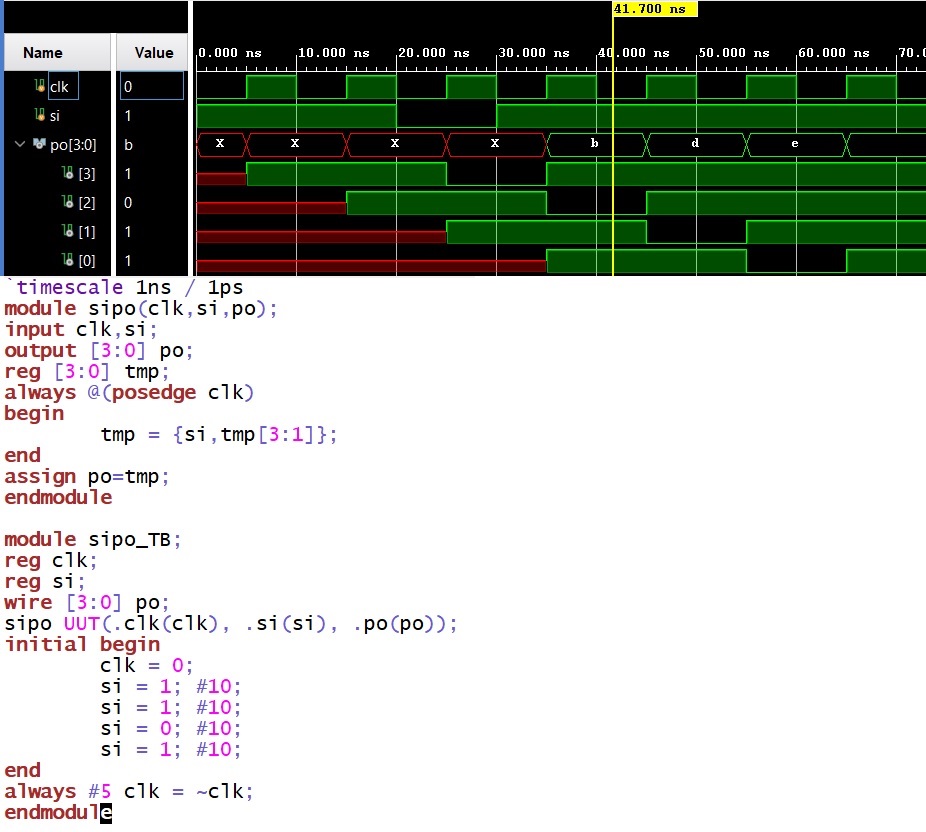

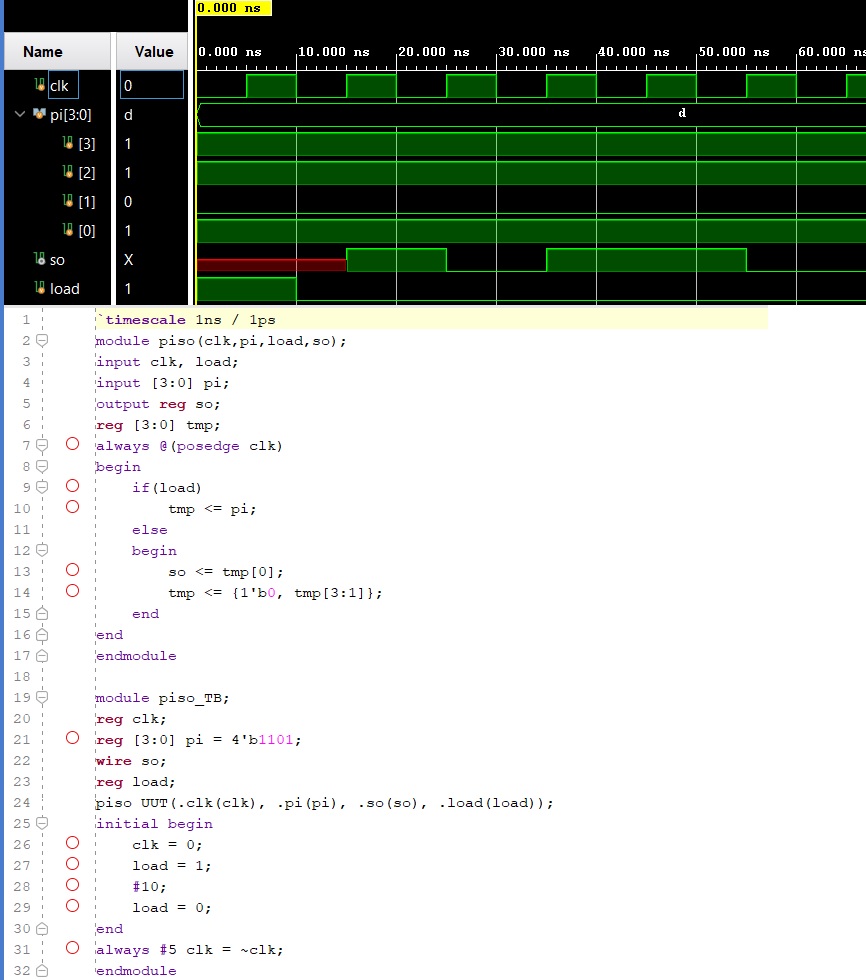

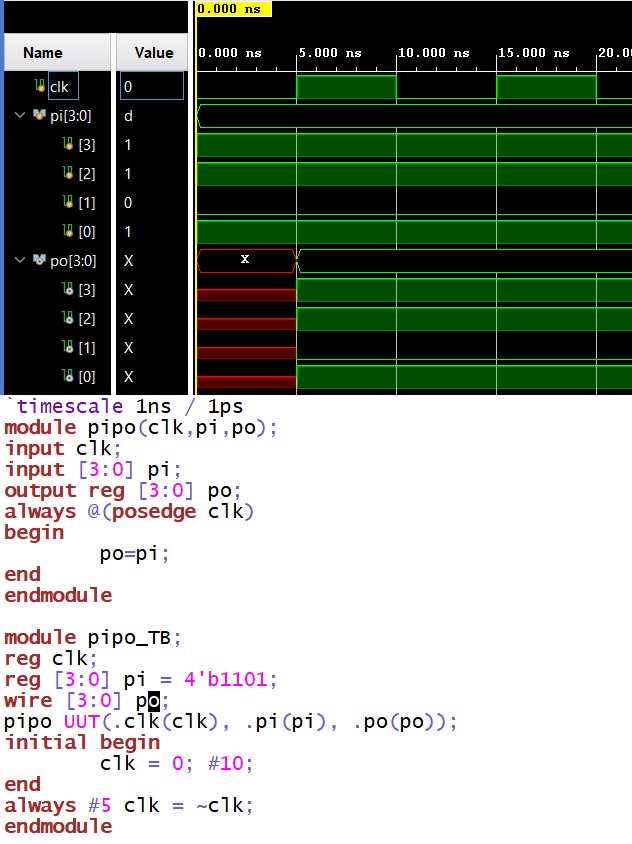

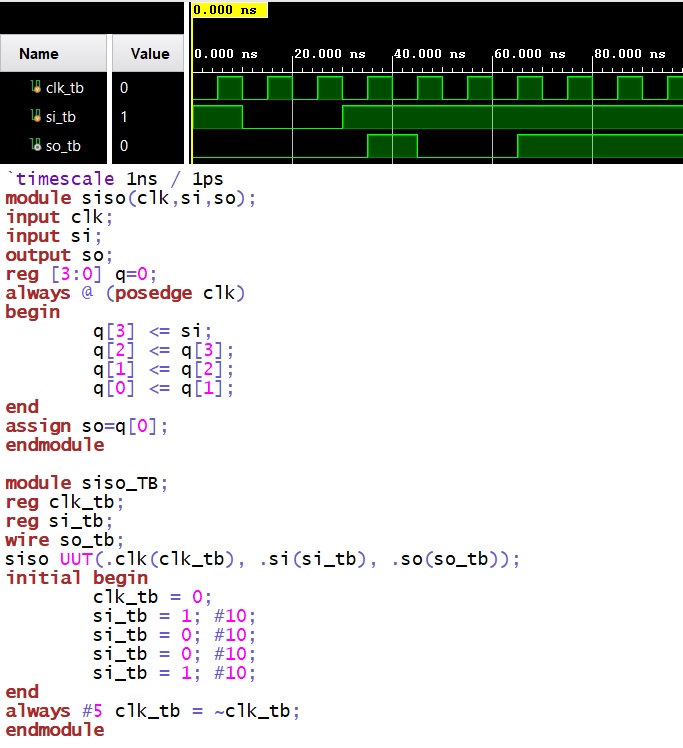

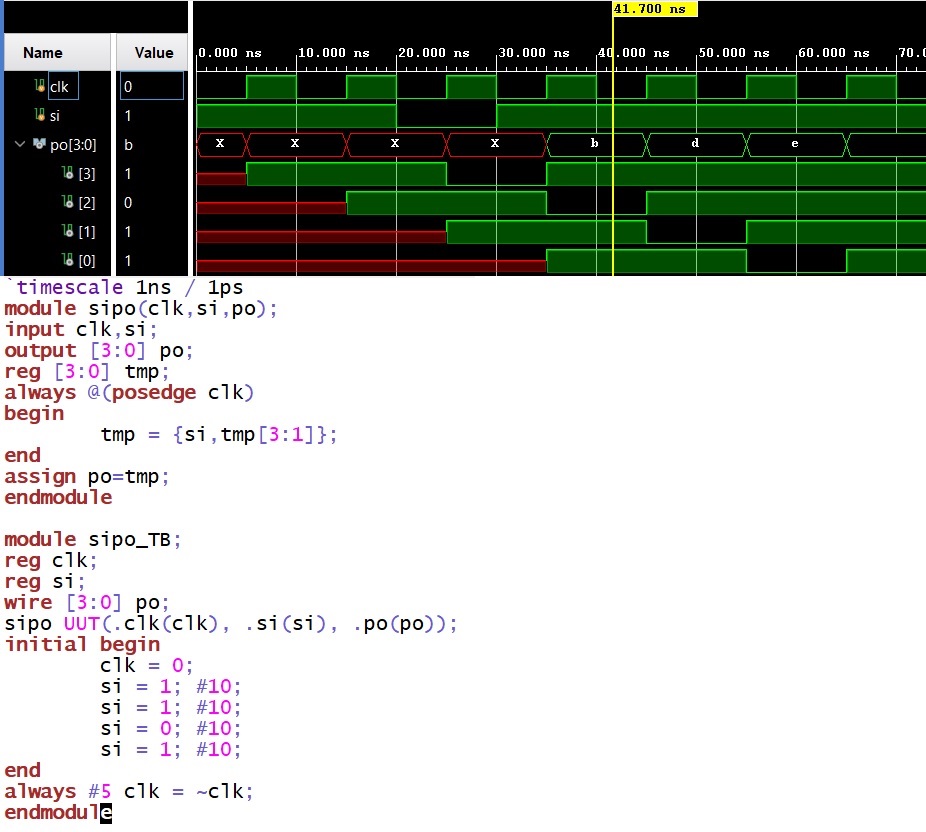

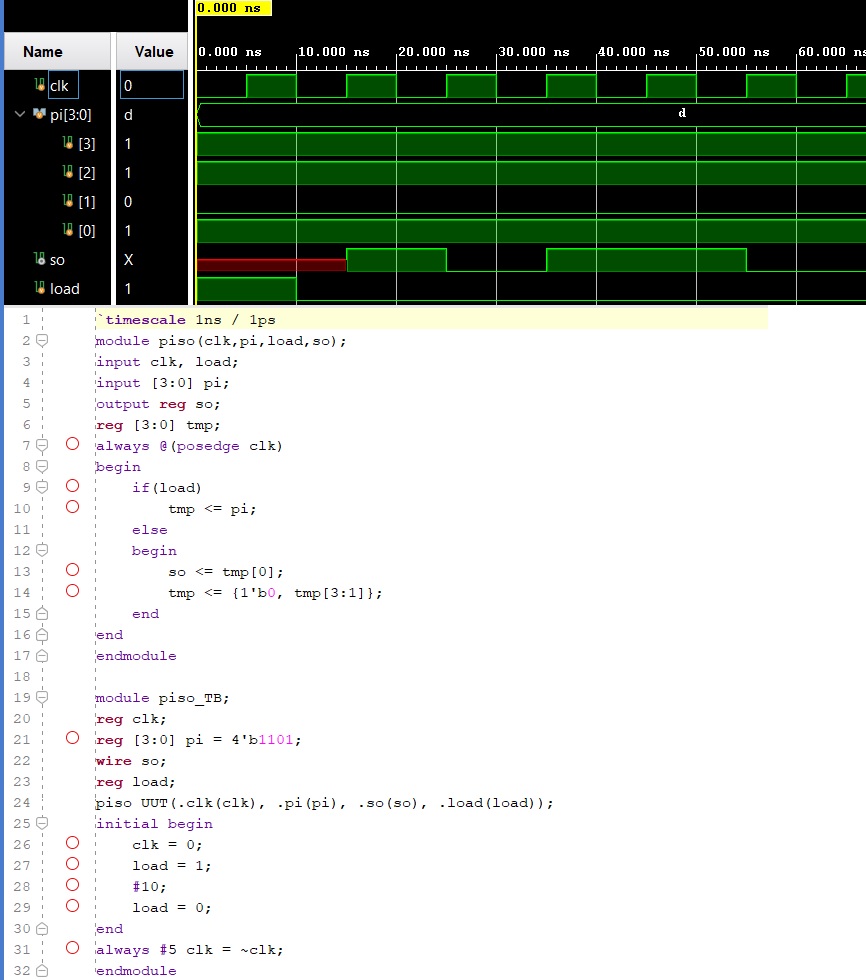

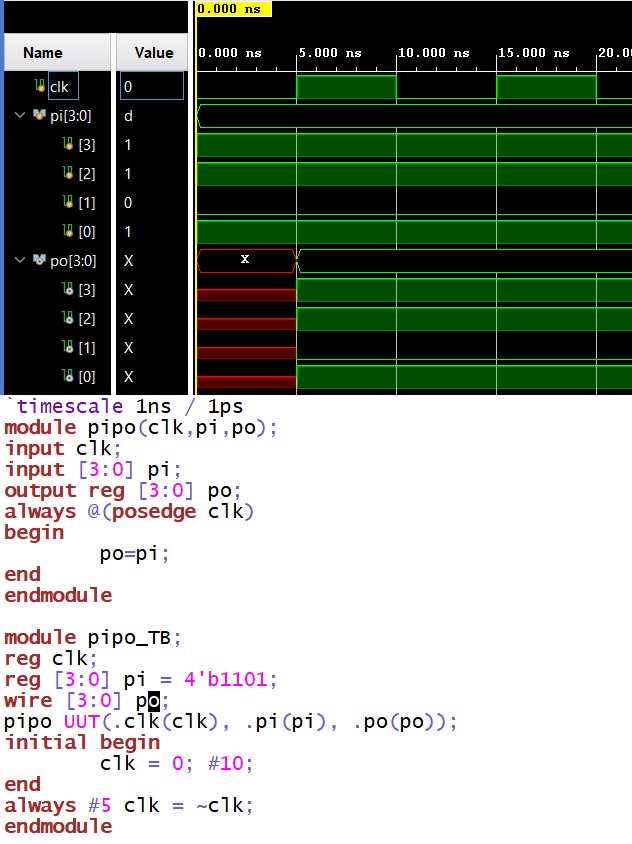

Task 3. Simulate the four types of shift registers in section 5.

Figure 4. Serial in serial out shifter simulation and file.

Figure 5. Serial in parallel out shifter.

Figure +6. Parallel in serial out.

Figure 7. Parallel in parallel out.

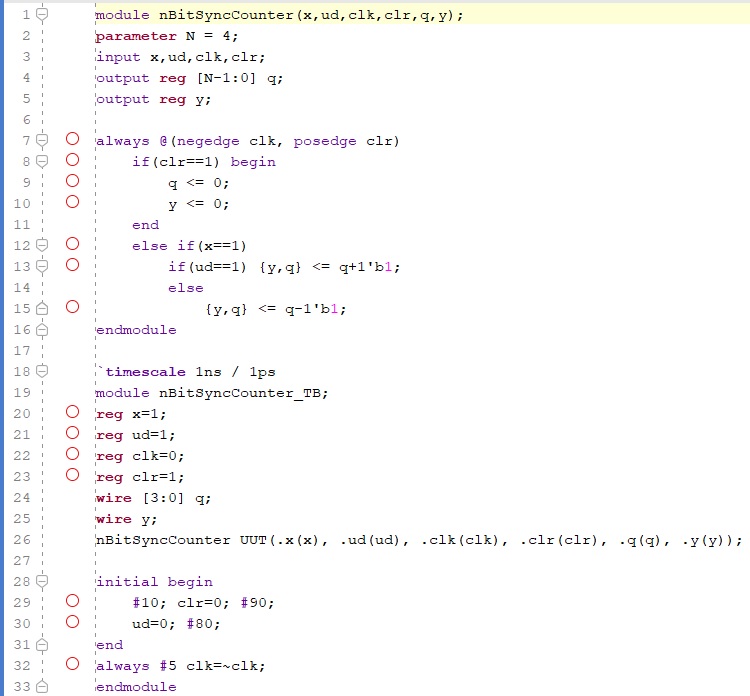

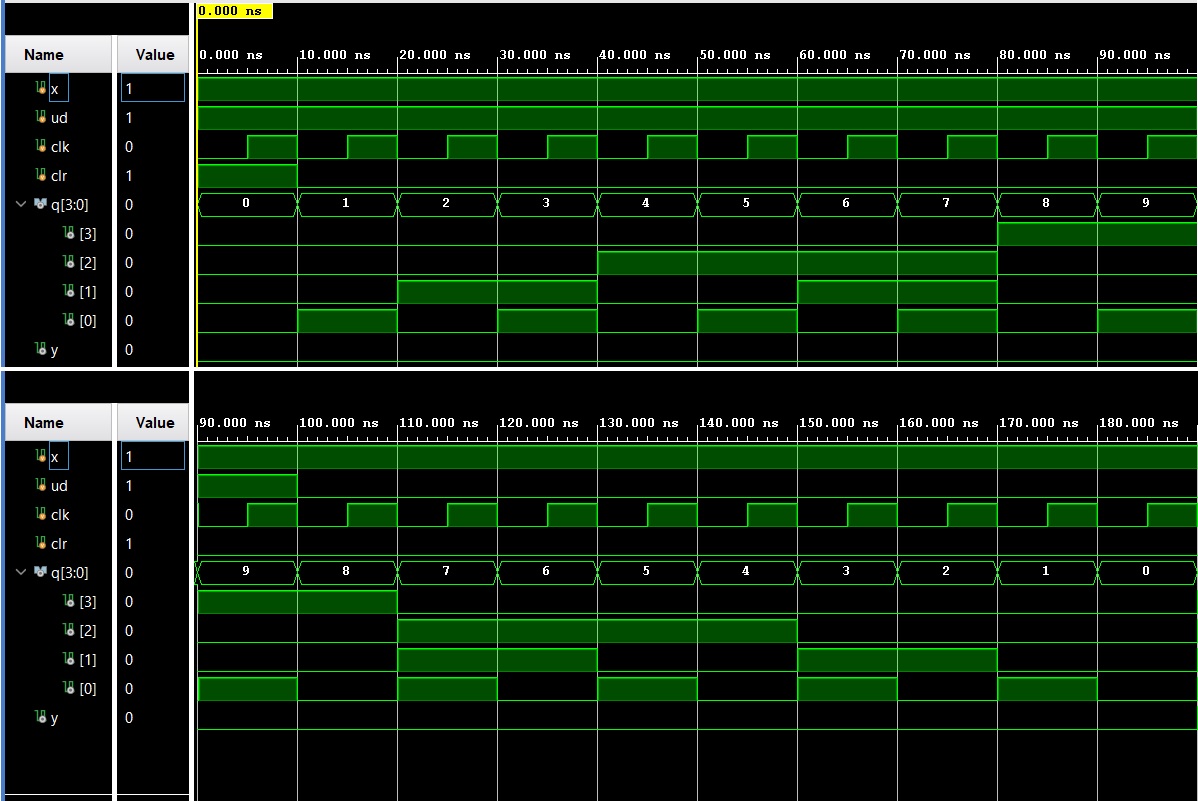

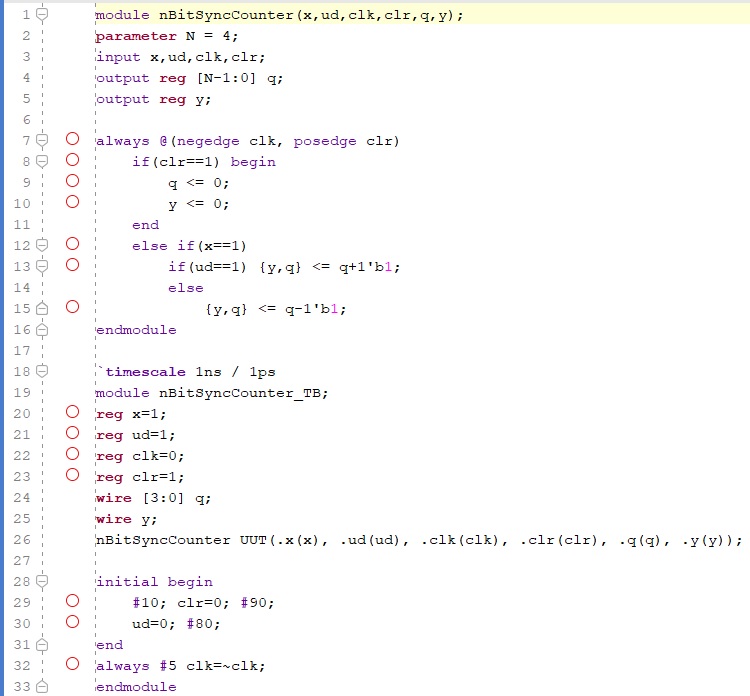

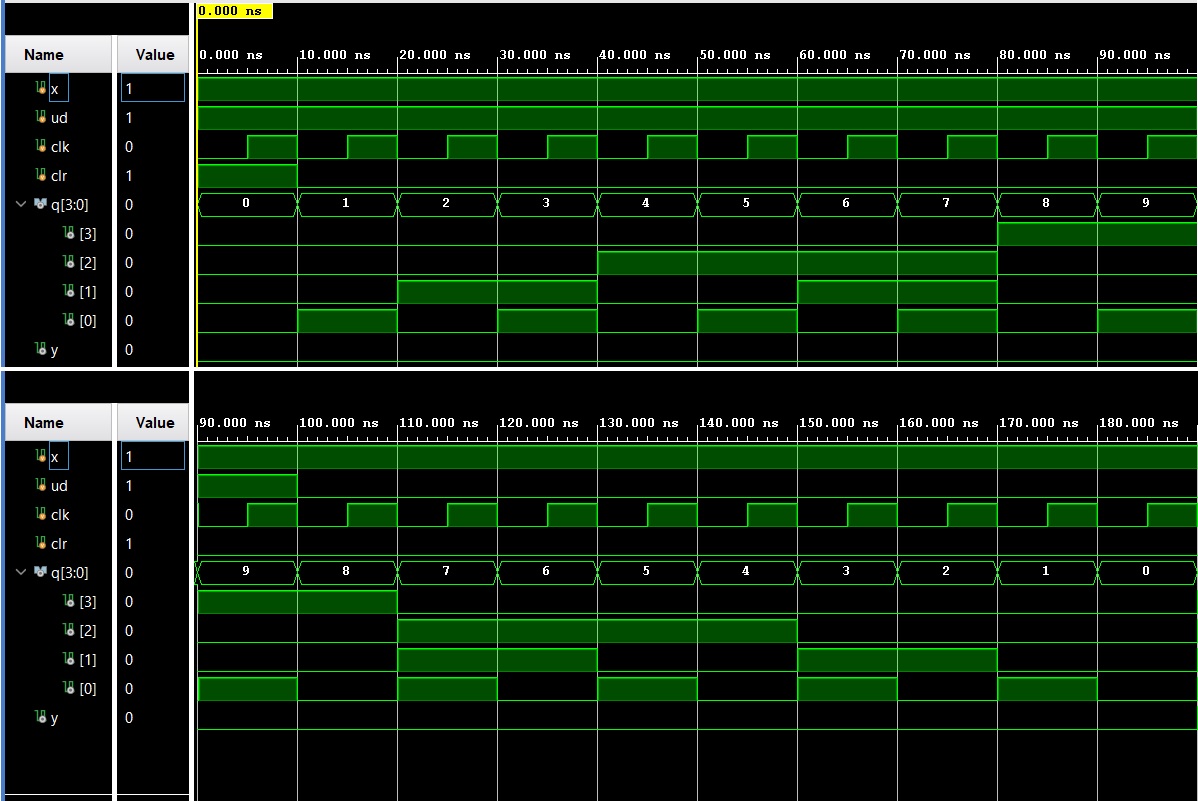

Task 4. Build a counter module and show the simulation results.

Figure 8. Counter module and testbench.

Figure 9. Counter simulation

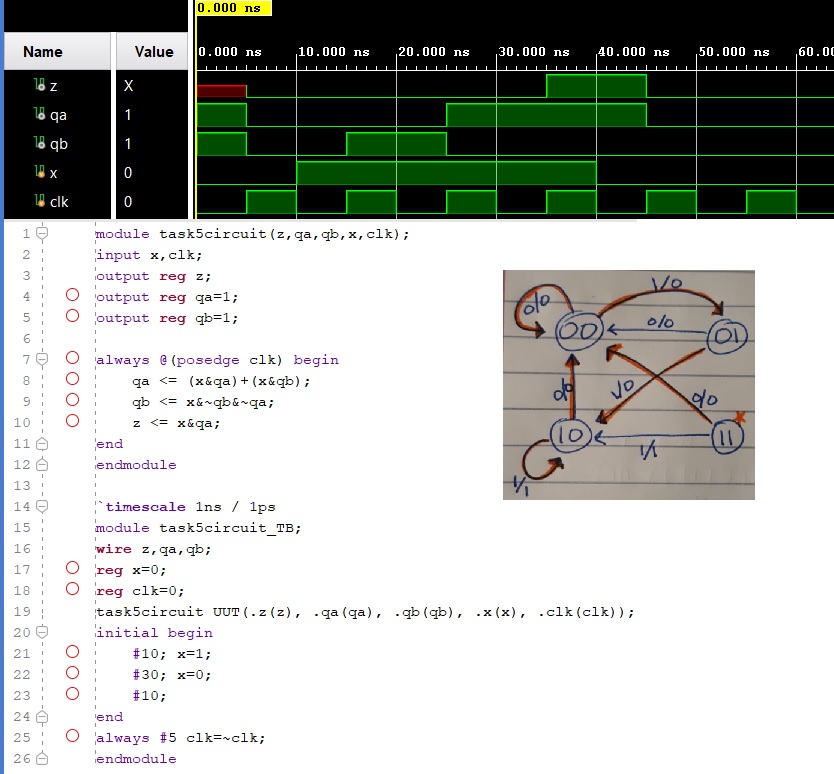

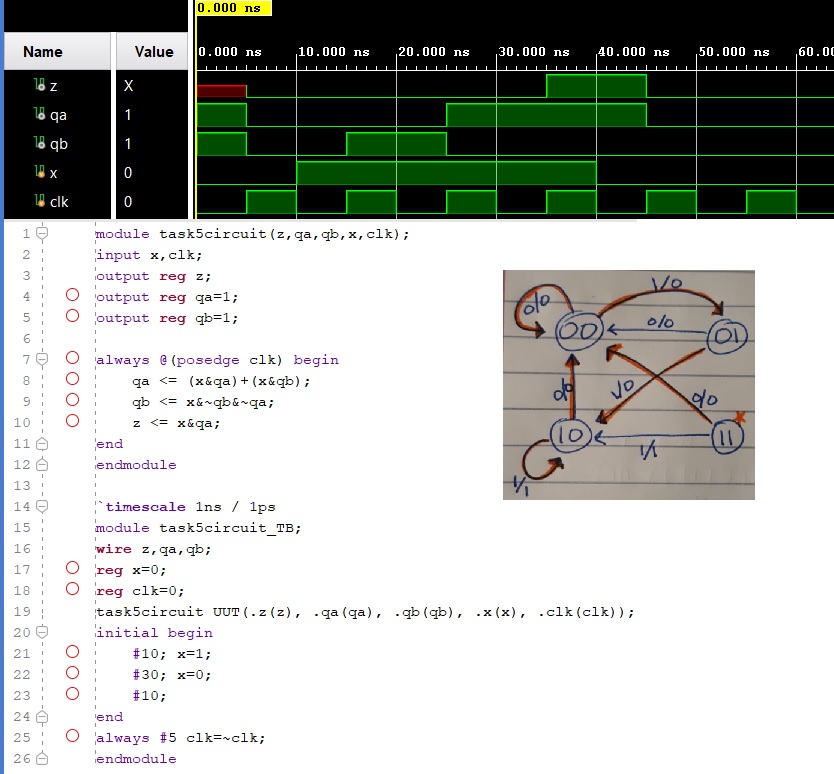

Task 5. Find the logic equation of the given circuit and implement in verilog.

Figure 10.

Task 5 circuit files, simulation and mealy state diagram.

5. Discussion

For this week, the tutorials were easy to understand and follow. I

enjoyed refreshing my memory on concepts and logic blocks that we

learned from fundamentals of logic. It was interesting coding up the

verilog files and running the simulations. I wasn't sure what time the

homework was due so I hope I didn't turn it in too late. Also, the

portion I did not finish is the behavioral files and simulation for

task 2.