CE433 Embedded Systems

Tutorial 1: Verilog and FPGA Basics

Name: Audra Benally

Email: albenally1@fortlewis.edu

1. Title: Verilog and FPGA Basics

2. Introduction: This was the first tutorial of the semester and

goes over the basics of verilog and vivado. This tutorial goes over the

gvim commands for creating a .v file module and testbench. Vivado use

and simulations are also covered in this tutorial.

3. Materials and Methods:

Materials:

- Computer

- Vivado Software

- GVim Software

Methods:

This tutorial was an

introduction to verilog. We were tasked with running simulations for

sections 2.1, 2.2, and 2.3 without knowing what the testbench looked

like. Then we copied the example in 2.4 and created a testbench to show

the difference between blocking and nonblocking methods. Task 3 was to

repeat the simulation in 2.5 in vivado. Task 4 was also the simulation

in 2.5 but with the delay in out1t instead of out2t. This task also

asked we hand draw the simulation in the same format as the given

graph. Finally, task 5 was replicating the example in 2.6.

4. Results:

Task 1: Use gvim and vivado to simulate 2.1, 2.2, and 2.3

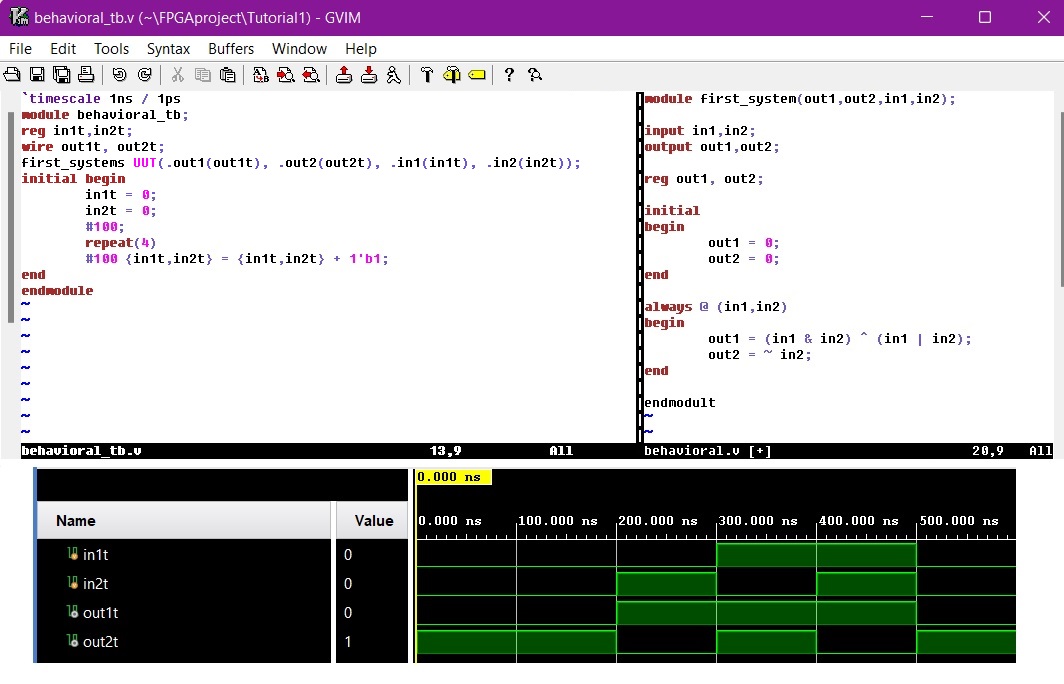

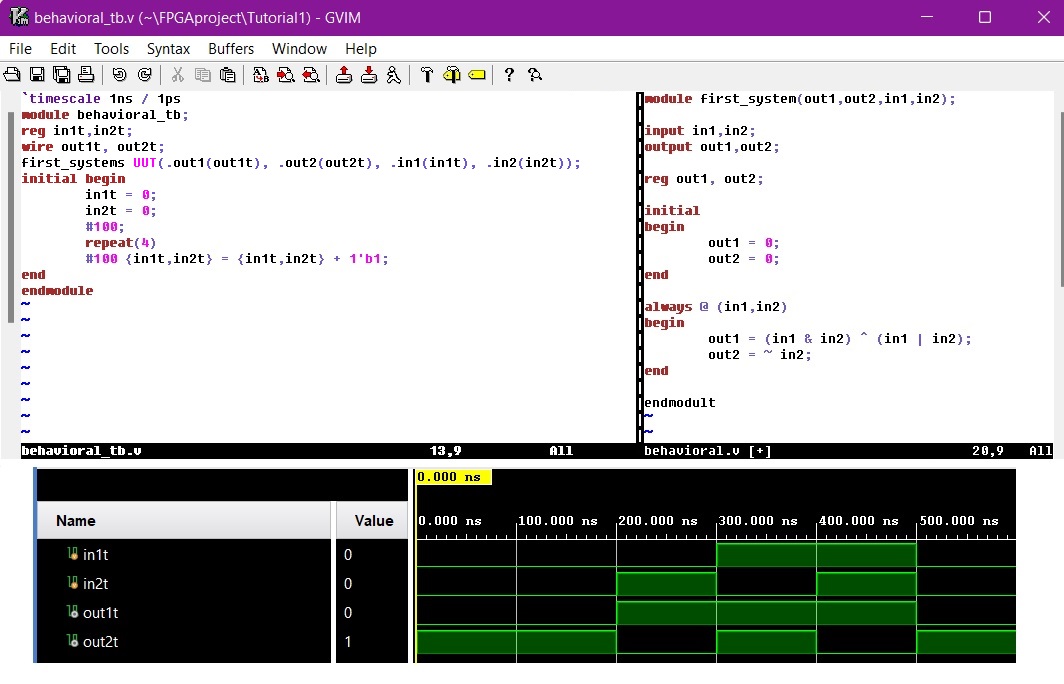

Figure 1. Behavioral model files and simulation.

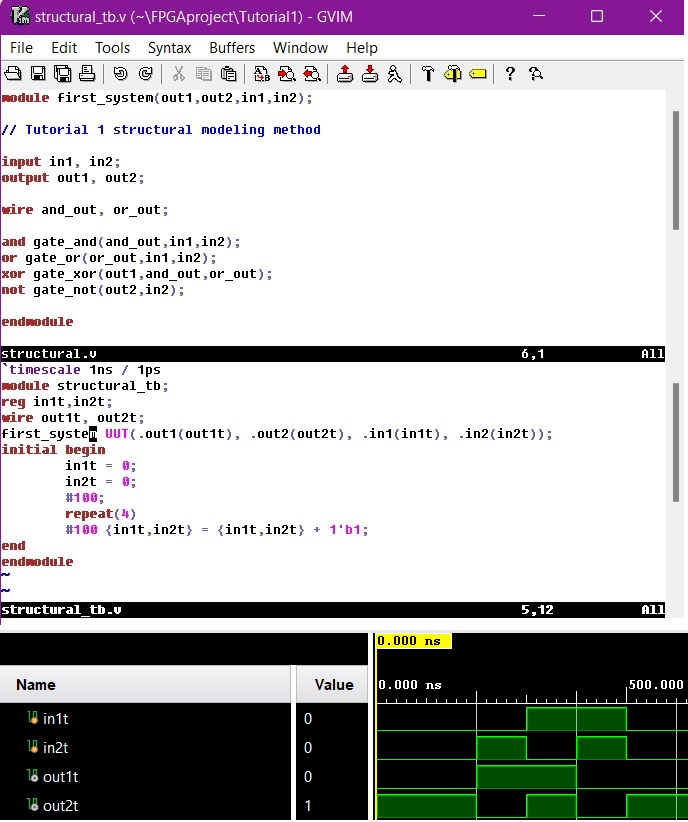

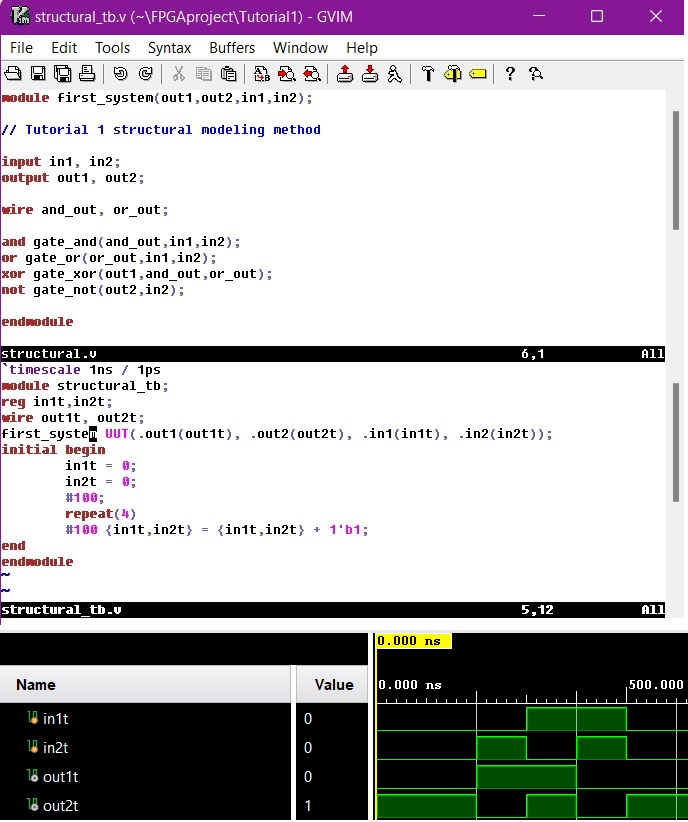

Figure 2.

Structural modeling method testbench and simulation results.

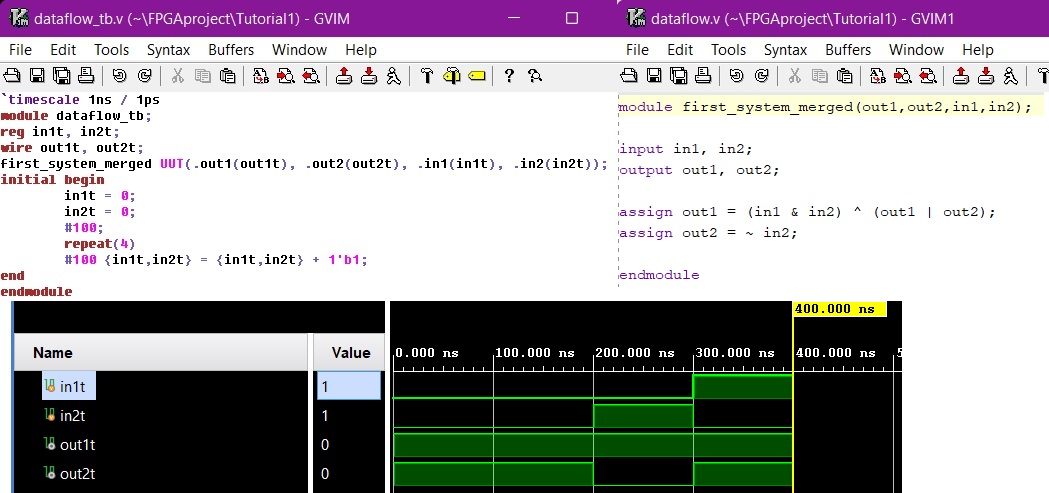

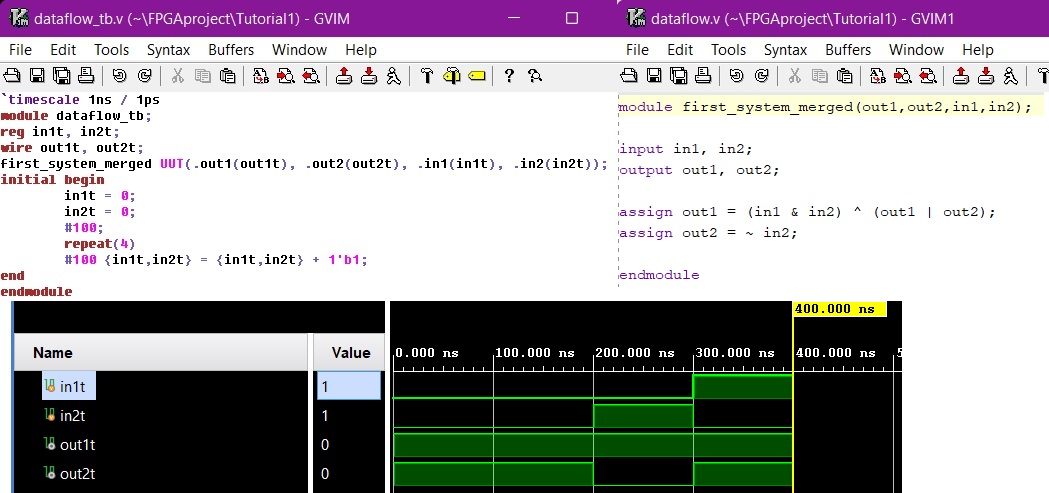

Figure 3. Dataflow modeling method.

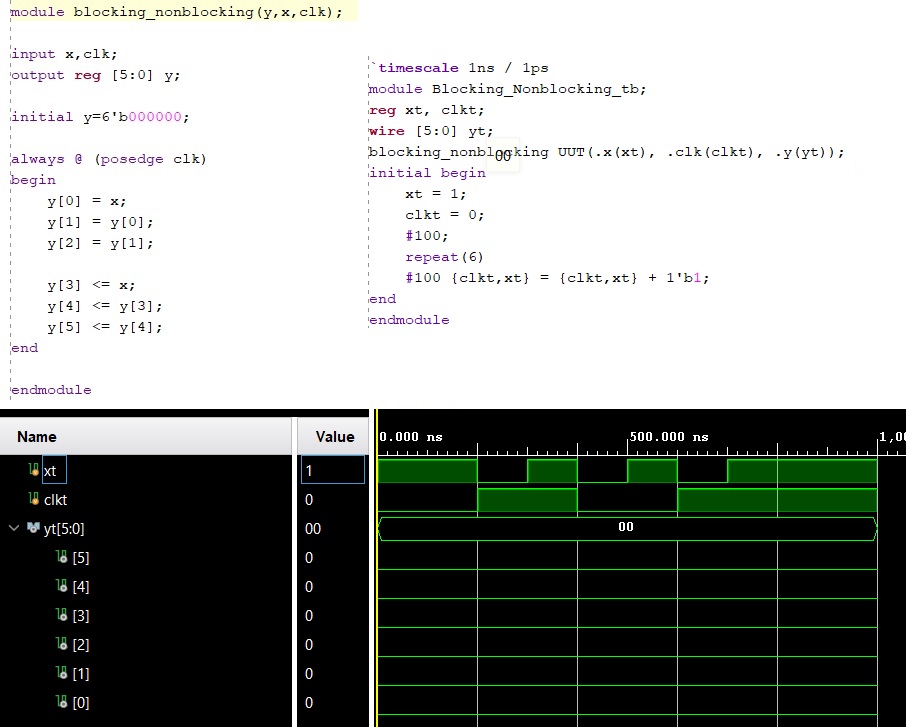

Task 2: Run a simulation to show the difference of blocking and non-blocking (2.4)

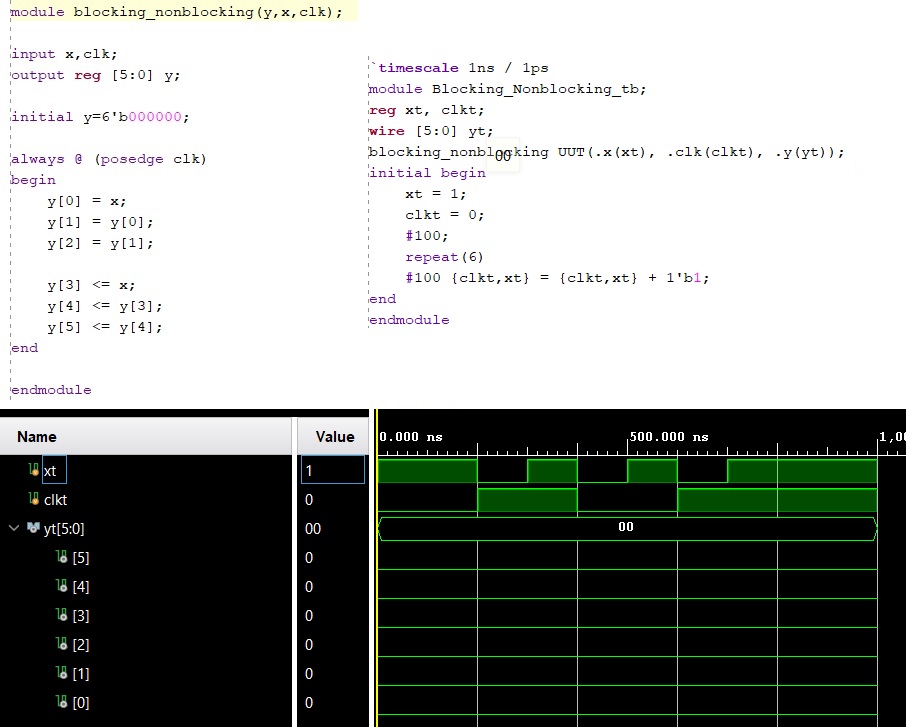

Figure 4. Results from the blocking / nonblocking simulation.

Task 3: Repeat the simulation example in 2.5

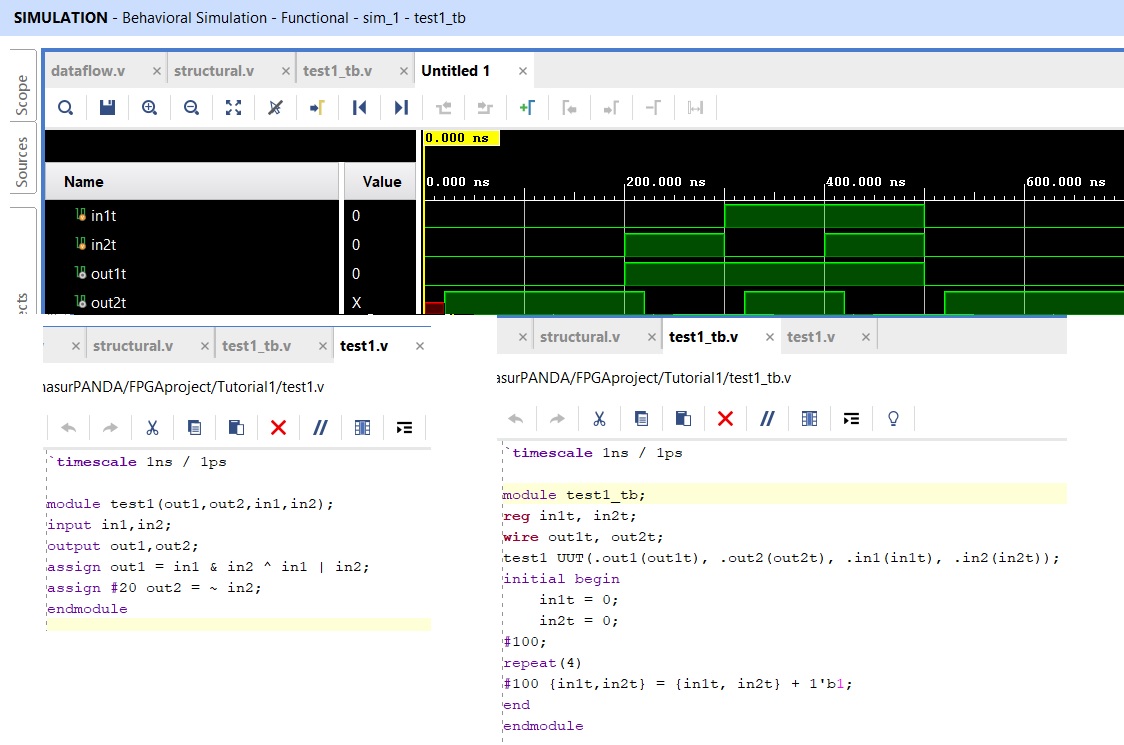

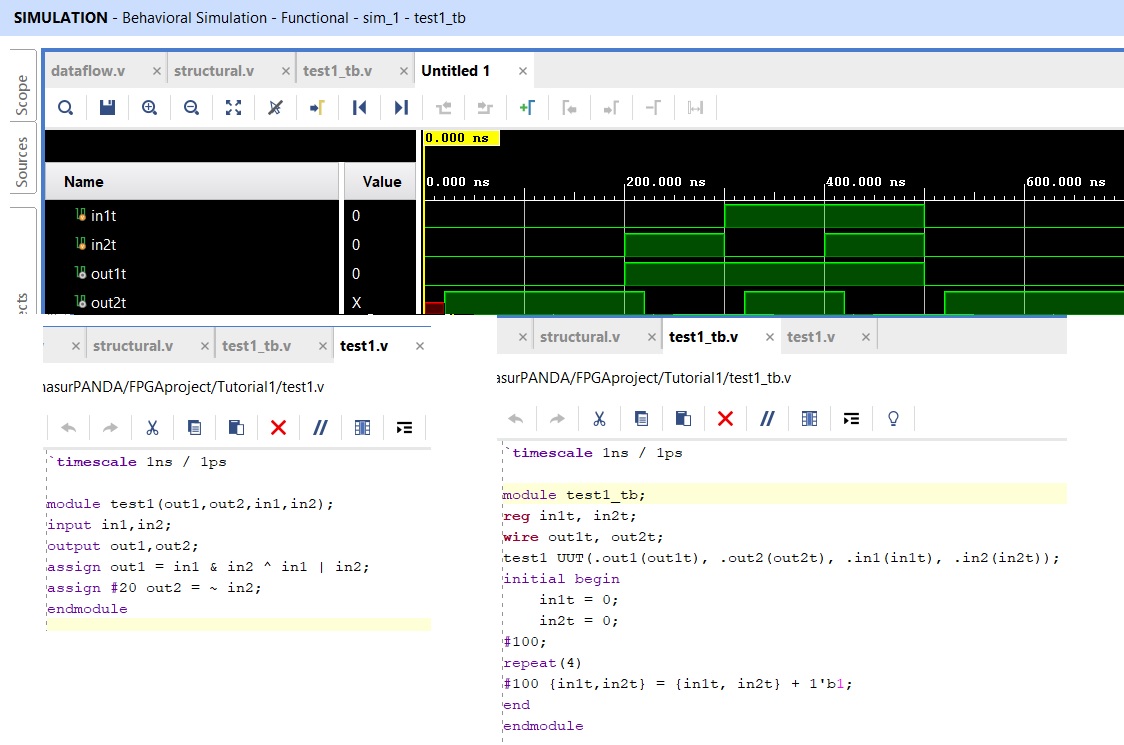

Figure 5. Simulation from the example in part 2.5

Task 4: Run the same 2.5 simulation with the 20ns delay in line 24.

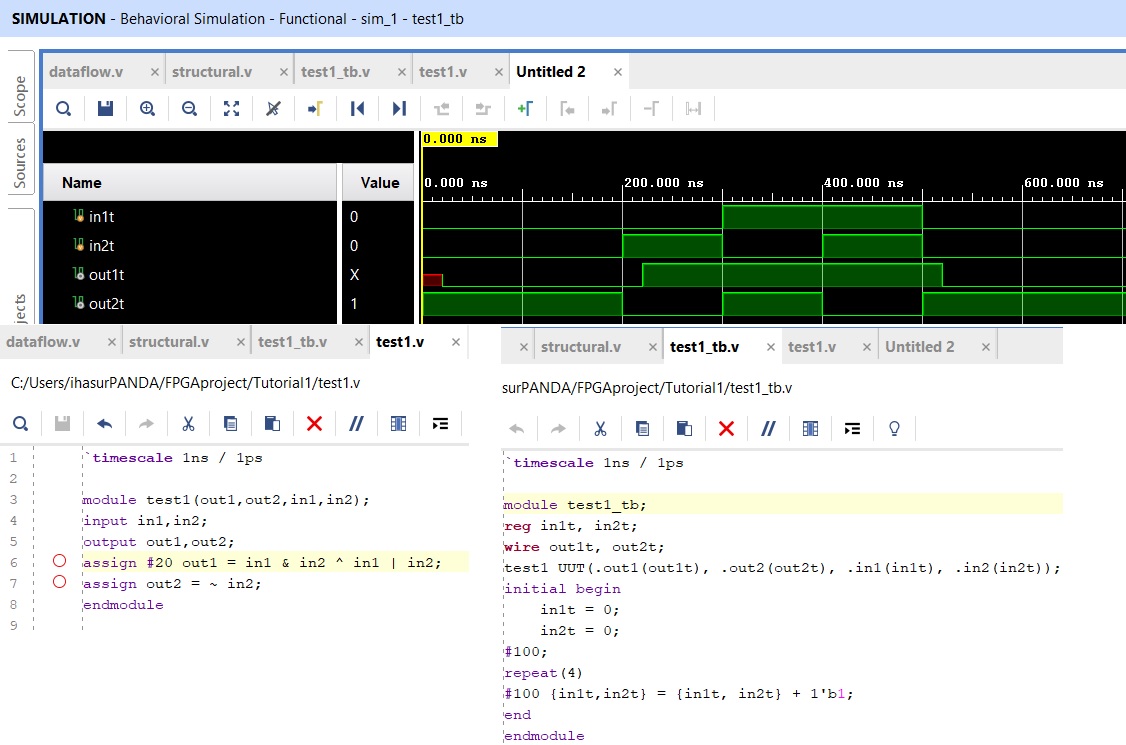

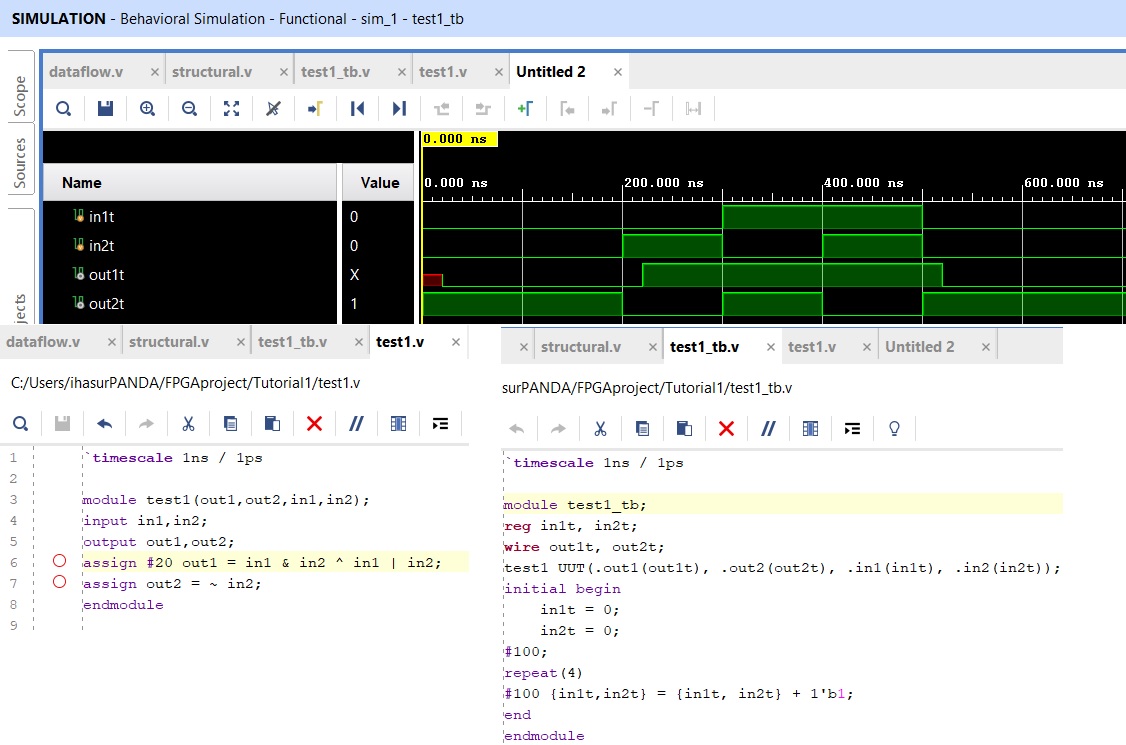

Figure 6.

Simulation with the "#20" delay in output 1 instead of output 2.

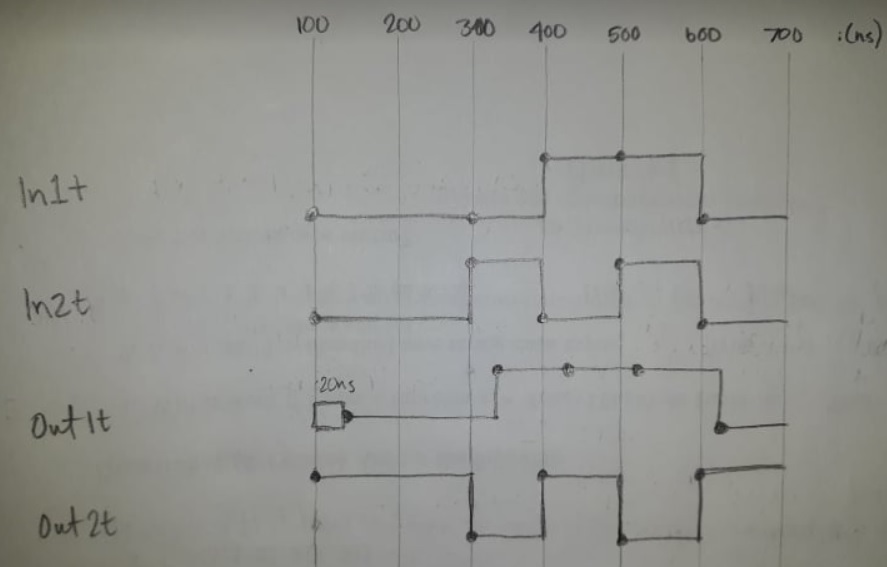

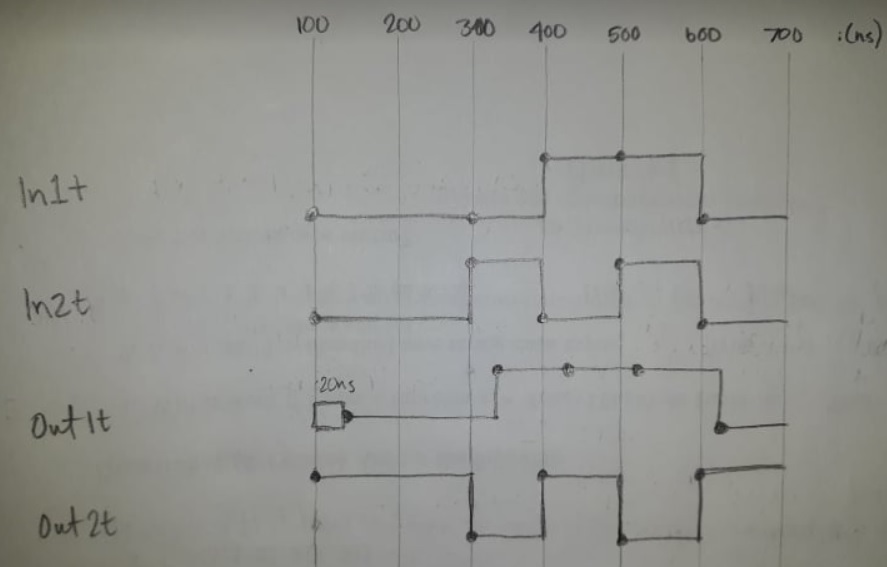

Figure 7. Hand drawn results of the simulation.

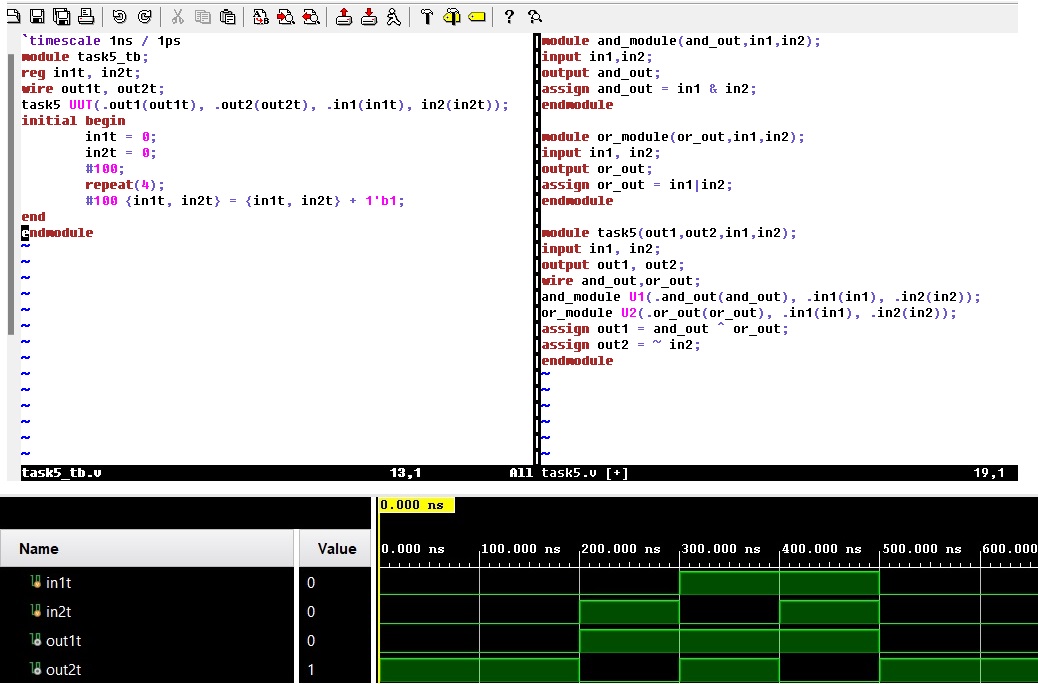

Task 5: Repeat the example in 2.6

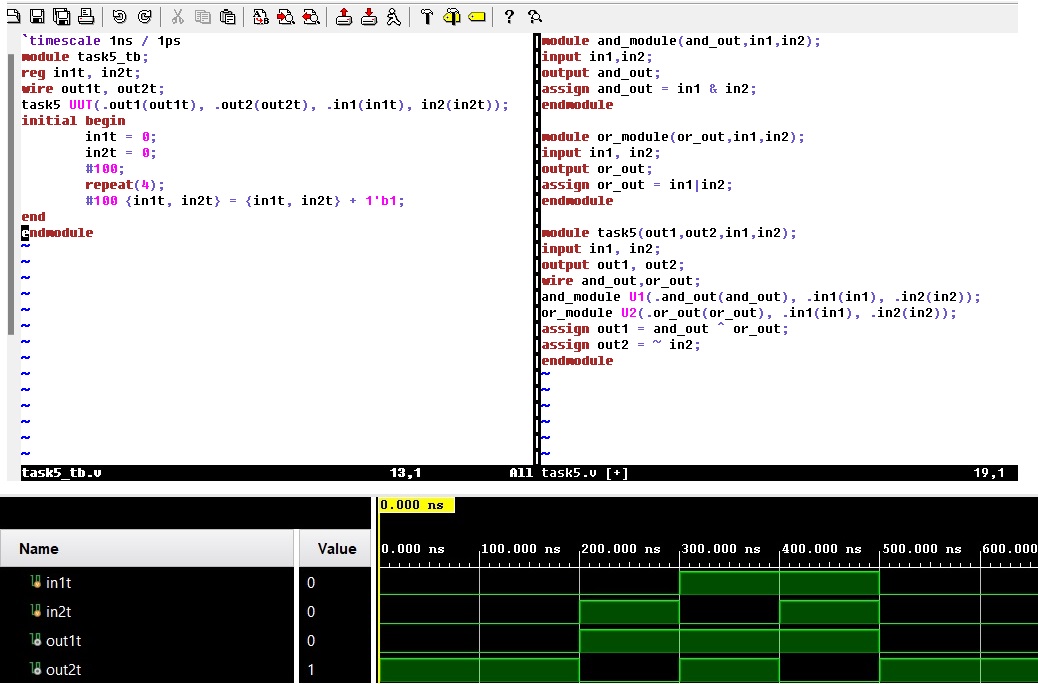

Figure 8.

Simulation results from the example in section 2.6.

5. Discussion

For this tutorial, I thought it was very interesting learning and

practicing vim commands in the gvim editor. I had trouble trying to

figure out the testbenches for the first tasks but after awhile the

files made more sense to me. In the dataflow modeling method I could

not figure out why the simulation stopped at 400ns while all the others

continued on to 700ns. For task 2, I had trouble figuring out how to

attach the components and I think that may be why my simulation did not

turn out well. I'm also unsure if I wrote a workable testbench for task

2 as well. Tasks 3, 4, and 5 were very straightforward. I started with

those first when working with vivado to get the hang of the program. I

had troubles figuring out how the simulation process worked but I think

I was able to understand it eventually. Overall, very fun and I'm

excited to work with the FPGA board.