## ENGR338 HW 3 Semiconductor Basics, the N Well, and C5 Layers

1. Draw a pn junction and explain: (20 points)

1) Without an external voltage, the formation of a depletion region.

2) With an external voltage, explain the changes of the width of the depletion region under 'forward bias' and 'reverse bias' operations.

3) Explain how the depletion region will be changed, and how the diode capacitance will be changed with an increasing voltage under both 'forward bias' and 'reverse bias' operations.

4) Hand-draw the I-V curve of a real diode (with a 0.7 built-in voltage and no reverse breakdown) and the IV curve of an ideal diode.

5) Hand-draw the IV curve of a real Zener diode (with a 0.7 built-in voltage and a -Vz) and the IV curve of an ideal Zener diode.

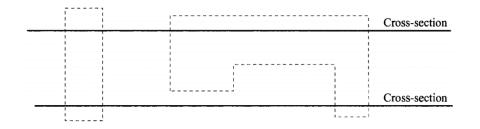

2. For the layout of n-wells seen in the following figure (top view), sketch the cross-sectional views at the places indicated. Is there a parasitic pn junction in the layout? If so, where? (20 points)

3. An n-well resistor has a width of 20 and a length of 400. A 20 by 20 square of n-well has a 15 fF parasitic capacitance. If the square resistance is 800 ohm, what is the time delay through this resistor without any extra load? (10 points)

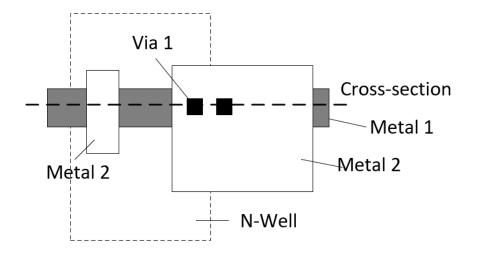

4. The following figure shows the top-view of a layout. Draw the cross-sectional view of the location indicated by the dashed line. (10 points)

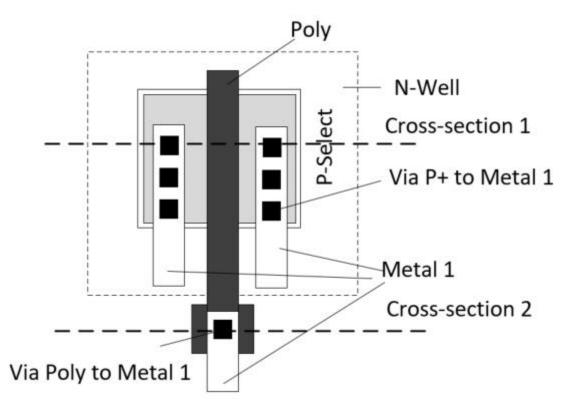

5. The following figure shows the top-view of a layout. Draw the cross-sectional views (cross-section 1 and cross-section 2 of the locations indicated by the dashed lines. (10 points)

6. Draw the cross-sectional view of all the layers of the C5 technology (from P-sub to over-glass opening). (10 points)

7. Why the footprint of N-Select is larger than N-Active? (10 points)

8. Can a polysilicon wire be used as resistors? How to reduce the resistance of a polysilicon wire? (10 points)